# Digital Design with Chisel

# Digital Design with Chisel

Third Edition

# **Digital Design with Chisel**

**Third Edition**

**Martin Schoeberl**

#### Copyright © 2016–2022 Martin Schoeberl

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. http://creativecommons.org/licenses/by-sa/4.0/

Email: martin@jopdesign.com

Visit the source at https://github.com/schoeberl/chisel-book

Published 2019 by Kindle Direct Publishing,

https://kdp.amazon.com/

#### Library of Congress Cataloging-in-Publication Data

Schoeberl, Martin

Digital Design with Chisel Martin Schoeberl Includes bibliographical references and an index. ISBN 9781689336031

Manufactured in the United States of America.

Typeset by Martin Schoeberl.

## **Contents**

| Fo | rewo  | rd                               | Хİ   |

|----|-------|----------------------------------|------|

| Pr | eface |                                  | xiii |

| 1  | Intro | oduction                         | 1    |

|    | 1.1   | Installing Chisel and FPGA Tools | 2    |

|    |       | 1.1.1 macOS                      | 2    |

|    |       | 1.1.2 Linux/Ubuntu               | 3    |

|    |       | 1.1.3 Windows                    | 3    |

|    |       | 1.1.4 FPGA Tools                 | 3    |

|    | 1.2   | Hello World                      | 3    |

|    | 1.3   | Chisel Hello World               | 4    |

|    | 1.4   | An IDE for Chisel                | 5    |

|    | 1.5   | Source Access and eBook Features | 5    |

|    | 1.6   | Further Reading                  | 6    |

|    | 1.7   | Exercise                         | 7    |

| 2  | Bas   | ic Components                    | 9    |

|    | 2.1   | Signal Types and Constants       | 9    |

|    | 2.2   | Combinational Circuits           | 11   |

|    |       | 2.2.1 Multiplexer                | 12   |

|    | 2.3   | Registers                        | 14   |

|    |       | 2.3.1 Counting                   | 16   |

|    | 2.4   | Structure with Bundle and Vec    | 16   |

|    | 2.5   | Wire, Reg, and IO                | 19   |

|    | 2.6   | Chisel Generates Hardware        | 20   |

|    | 2.7   | Exercise                         | 21   |

| 3  | Buil  | d Process and Testing            | 23   |

|    | 3.1   | Building your Project with sbt   | 23   |

|    |       | 3.1.1 Source Organization        |      |

|   |     | 3.1.2     | Running sbt                         |  |   | 25 |

|---|-----|-----------|-------------------------------------|--|---|----|

|   |     | 3.1.3     | Generating Verilog                  |  |   | 26 |

|   |     | 3.1.4     | Tool Flow                           |  |   | 27 |

|   | 3.2 | Testing   | g with Chisel                       |  |   | 27 |

|   |     | 3.2.1     | ScalaTest                           |  |   | 29 |

|   |     | 3.2.2     | ChiselTest                          |  |   | 30 |

|   |     | 3.2.3     | Waveforms                           |  |   | 33 |

|   |     | 3.2.4     | printf Debugging                    |  |   | 35 |

|   | 3.3 | Exercis   |                                     |  |   | 36 |

|   |     | 3.3.1     | A Minimal Project                   |  |   | 36 |

|   |     | 3.3.2     | Using a GitHub Template             |  |   | 38 |

|   |     | 3.3.3     | A Testing Exercise                  |  |   | 39 |

|   |     |           |                                     |  |   |    |

| 4 | Con | ponent    | ts                                  |  |   | 41 |

|   | 4.1 | Compo     | onents in Chisel are Modules        |  |   | 41 |

|   | 4.2 |           | d Components                        |  |   | 45 |

|   | 4.3 | An Ari    | rithmetic Logic Unit                |  |   | 48 |

|   | 4.4 |           | Connections                         |  |   | 50 |

|   | 4.5 | Lightw    | weight Components with Functions    |  |   | 52 |

|   | 4.6 | Extern    | nal Modules                         |  | • | 53 |

| 5 | Con |           | onal Building Blocks                |  |   | 57 |

|   | 5.1 | Combi     | inational Circuits                  |  |   | 57 |

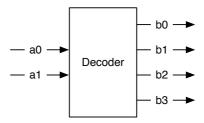

|   | 5.2 | Decode    | ler                                 |  |   | 59 |

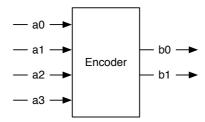

|   | 5.3 | Encode    | ler                                 |  |   | 61 |

|   | 5.4 | Exercis   | ise                                 |  | • | 62 |

| 6 | Seq | uential E | Building Blocks                     |  |   | 63 |

|   | 6.1 | Registe   | ers                                 |  |   | 63 |

|   | 6.2 | Counte    | ers                                 |  |   | 67 |

|   |     | 6.2.1     | Counting Up and Down                |  |   | 69 |

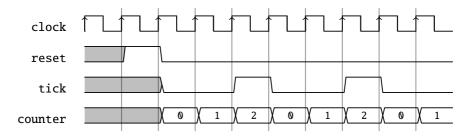

|   |     | 6.2.2     | Generating Timing with Counters     |  |   | 70 |

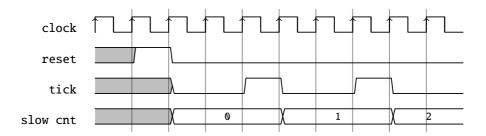

|   |     | 6.2.3     | The Nerd Counter                    |  |   | 71 |

|   |     | 6.2.4     | A Timer                             |  |   | 72 |

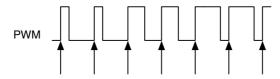

|   |     | 6.2.5     | Pulse-Width Modulation              |  |   | 74 |

|   | 6.3 | Shift R   | Registers                           |  |   | 76 |

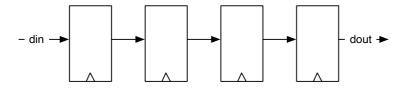

|   |     | 6.3.1     | Shift Register with Parallel Output |  |   | 76 |

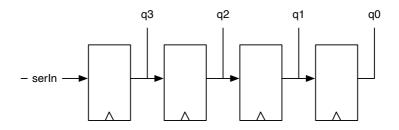

|   |     | 6.3.2     | Shift Register with Parallel Load   |  |   | 77 |

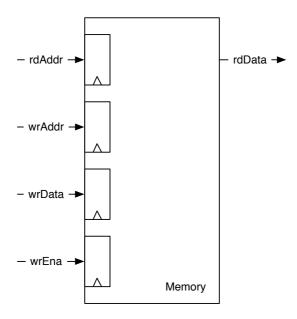

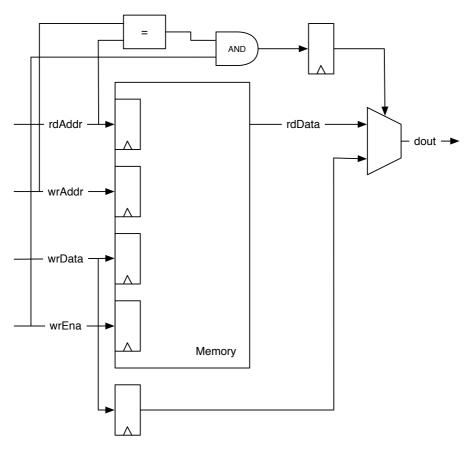

|   | 6.4 | Memor     |                                     |  |   | 70 |

|    | 6.5   | Exercise                                        | 32  |

|----|-------|-------------------------------------------------|-----|

| 7  | Inpu  | t Processing 8                                  | 35  |

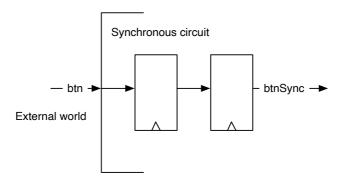

|    | 7.1   | Asynchronous Input                              | 35  |

|    | 7.2   |                                                 | 36  |

|    | 7.3   |                                                 | 38  |

|    | 7.4   |                                                 | 39  |

|    | 7.5   |                                                 | 91  |

|    | 7.6   |                                                 | 92  |

| 8  | Finit | e-State Machines                                | 93  |

|    | 8.1   |                                                 | 93  |

|    | 8.2   |                                                 | 97  |

|    | 8.3   |                                                 | 99  |

|    | 8.4   | Exercise                                        | )3  |

| 9  | Com   | municating State Machines 10                    | )5  |

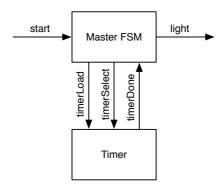

| •  | 9.1   | A Light Flasher Example                         |     |

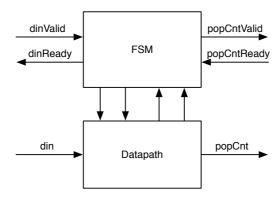

|    | 9.2   | State Machine with Datapath                     | -   |

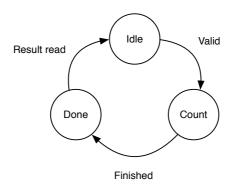

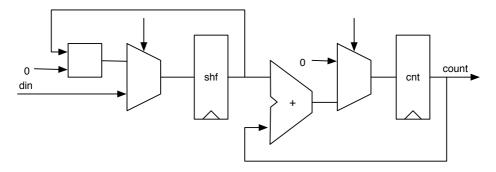

|    | - · - | 9.2.1 Popcount Example                          |     |

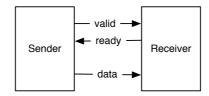

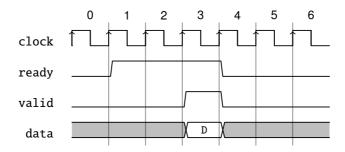

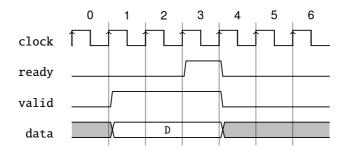

|    | 9.3   | Ready-Valid Interface                           |     |

| 10 | Hard  | ware Generators 1                               | 19  |

|    |       | A Little Bit of Scala                           | -   |

|    |       | Configure with Parameters                       |     |

|    | 10.2  | 10.2.1 Simple Parameters                        |     |

|    |       | 10.2.2 Functions with Type Parameters           |     |

|    |       | 10.2.3 Modules with Type Parameters             |     |

|    |       | 10.2.4 Parameterized Bundles                    |     |

|    | 10.3  | Generate Combinational Logic                    |     |

|    |       | Use Inheritance                                 |     |

|    |       | Hardware Generation with Functional Programming |     |

| 11 | Fxar  | nple Designs                                    | 3.5 |

|    |       | FIFO Buffer                                     |     |

|    |       | A Serial Port                                   |     |

|    |       | FIFO Design Variations                          |     |

|    | 11.0  | 11.3.1 Parameterizing FIFOs                     |     |

|    |       | 11.3.2 Redesigning the Bubble FIFO              |     |

|    |       |                                                 |     |

|    | 11.3.3 Double Buffer FIFO                | 148 |

|----|------------------------------------------|-----|

|    | 11.3.4 FIFO with Register Memory         |     |

|    | 11.3.5 FIFO with On-Chip Memory          |     |

|    | 11.4 A Multi-clock Memory                |     |

|    | 11.5 Exercises                           |     |

|    | 11.5.1 Explore the Bubble FIFO           |     |

|    | 11.5.2 The UART                          |     |

|    | 11.5.3 FIFO Exploration                  | 158 |

| 12 | Design of a Processor                    | 159 |

| -  | 12.1 Start with an ALU                   |     |

|    | 12.2 Decoding Instructions               |     |

|    | 12.3 Assembling Instructions             |     |

|    | 12.4 Exercise                            |     |

|    | 12.1 Exercise                            | 100 |

| 13 | Contributing to Chisel                   | 169 |

|    | 13.1 Publishing a Chisel Library         | 169 |

|    | 13.1.1 Using a Library                   | 169 |

|    | 13.1.2 Prerequisite                      | 170 |

|    | 13.1.3 Library Setup                     |     |

|    | 13.1.4 Regular Publishing                |     |

|    | 13.2 Contributing to Chisel              |     |

|    | 13.2.1 Setup the Development Environment |     |

|    | 13.2.2 Testing                           |     |

|    | 13.2.3 Contribute with a Pull Request    |     |

|    | 13.3 Exercise                            | 174 |

| 14 | Summary                                  | 175 |

| A  | Reserved Keywords                        | 177 |

| В  | Chisel Projects                          | 179 |

| C  | Advanced Testing                         | 181 |

|    | C.1 Multithreaded Testing                |     |

|    | C.2 Simulator Backends                   |     |

|    |                                          |     |

| D  | PeekPokeTester                           | 185 |

| Ε  | Chisel 2                                 | 189 |

# **List of Figures**

| 2.1  | Logic for the expression (a & b)   c. The wires can be a single bit or | 11       |

|------|------------------------------------------------------------------------|----------|

| 2.2  | 1 /                                                                    | 11<br>14 |

| 2.3  | <u>.</u>                                                               | 15       |

| 2.3  | A D inp-nop based register with a synchronous reset to 0               | 13       |

| 3.1  | $1  3  \langle  \mathcal{E}  \rangle$                                  | 24       |

| 3.2  | Tool flow of the Chisel ecosystem.                                     | 28       |

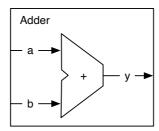

| 4.1  | An adder component                                                     | 42       |

| 4.2  |                                                                        | 42       |

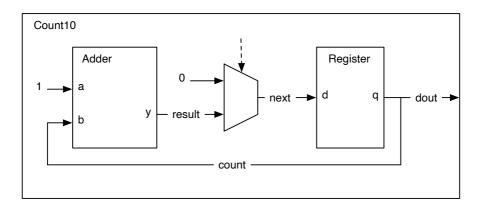

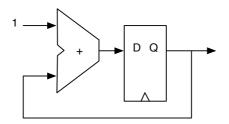

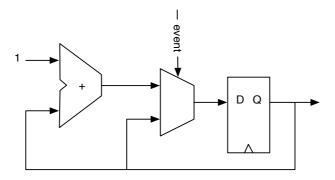

| 4.3  | A counter built out of components                                      | 43       |

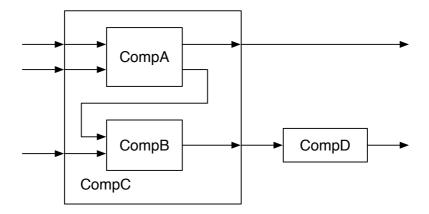

| 4.4  | A design consisting of a hierarchy of components                       | 45       |

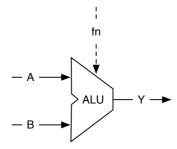

| 4.5  | An arithmetic logic unit, or ALU for short                             | 49       |

| 5.1  | 1                                                                      | 58       |

| 5.2  |                                                                        | 60       |

| 5.3  | A 4-bit to 2-bit encoder                                               | 61       |

| 6.1  |                                                                        | 63       |

| 6.2  |                                                                        | 65       |

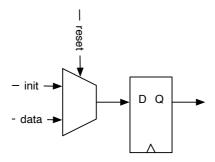

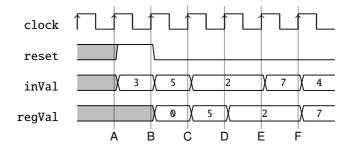

| 6.3  | $\epsilon$                                                             | 65       |

| 6.4  |                                                                        | 66       |

| 6.5  |                                                                        | 66       |

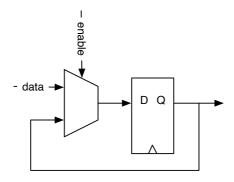

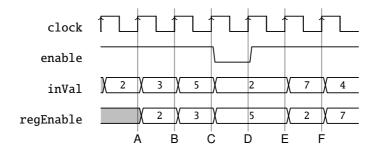

| 6.6  | $oldsymbol{arepsilon}$                                                 | 68       |

| 6.7  |                                                                        | 68       |

| 6.8  |                                                                        | 70       |

| 6.9  | 8                                                                      | 71       |

| 6.10 |                                                                        | 73       |

|      |                                                                        | 74       |

|      | $\epsilon$                                                             | 76       |

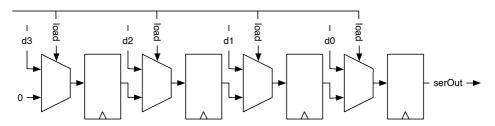

| 6 13 | A 4-bit shift register with parallel output                            | 77       |

| 6.15 | A 4-bit shift register with parallel load                                     |

|------|-------------------------------------------------------------------------------|

| 0.10 | A synchronous memory with forwarding for a defined read-during-write behavior |

| 7.1  | Input synchronizer                                                            |

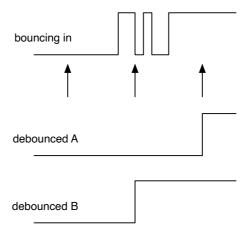

| 7.2  | Debouncing an input signal                                                    |

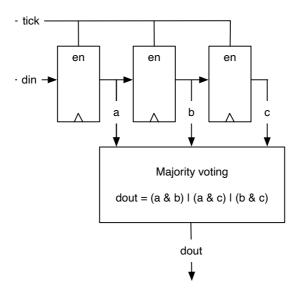

| 7.3  | Majority voting on the sampled input signal                                   |

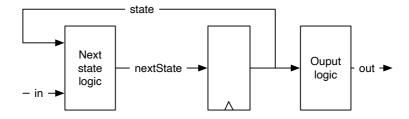

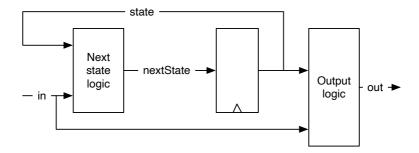

| 8.1  | A finite-state machine (Moore type)                                           |

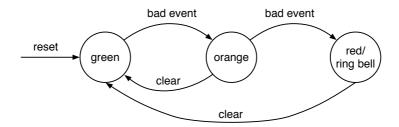

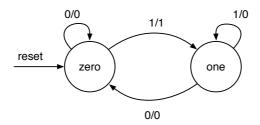

| 8.2  | The state diagram of an alarm FSM                                             |

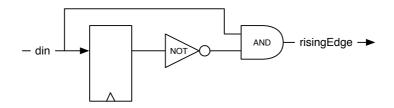

| 8.3  | A rising edge detector (Mealy type FSM)                                       |

| 8.4  | A Mealy type finite-state machine                                             |

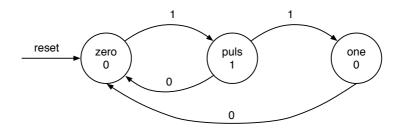

| 8.5  | The state diagram of the rising edge detector as Mealy FSM 99                 |

| 8.6  | The state diagram of the rising edge detector as Moore FSM 101                |

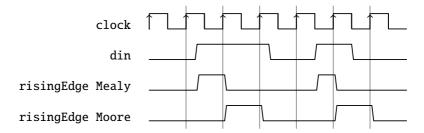

| 8.7  | Mealy and a Moore FSM waveform for rising edge detection 101                  |

| 9.1  | The light flasher split into a Master FSM and a Timer FSM 106                 |

| 9.2  | The light flasher split into a Master FSM, a Timer FSM, and a Counter         |

|      | FSM                                                                           |

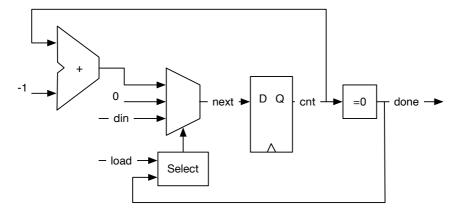

| 9.3  | A state machine with a datapath                                               |

| 9.4  | State diagram for the popcount FSM                                            |

| 9.5  | Datapath for the popcount circuit                                             |

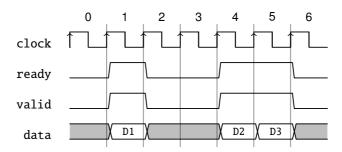

| 9.6  | The ready-valid flow control                                                  |

| 9.7  | Data transfer with a ready-valid interface, early ready                       |

| 9.8  | Data transfer with a ready-valid interface, late ready                        |

| 9.9  | Single cycle ready/valid and back-to-back transfers                           |

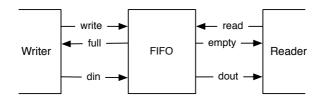

| 11.1 | A writer, a FIFO buffer, and a reader                                         |

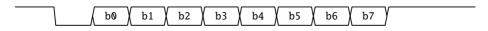

| 11.2 | One byte transmitted by a UART                                                |

## **List of Tables**

| 2.1         | Chisel defined hardware operators               |

|-------------|-------------------------------------------------|

| 2.2         | Chisel defined hardware functions, invoked on v |

| 5.1         | Truth table for a 2 to 4 decoder                |

| 5.2         | Truth table for a 4 to 2 encoder                |

| 8.1         | State table for the alarm FSM                   |

| 12.1        | Leros instruction set                           |

| <b>A.</b> 1 | Reserved keywords from the Scala language       |

| A.2         | Reserved keywords from the Chisel language      |

# Listings

| 1.1  | A hardware Hello World in Chisel                  |

|------|---------------------------------------------------|

| 4.1  | The adder component in Chisel                     |

| 4.2  | The register component in Chisel                  |

| 4.3  | A counter built out of components                 |

| 4.4  | Definitions of component A and B                  |

| 4.5  | Component C                                       |

| 4.6  | Component D                                       |

| 4.7  | Top-level component                               |

| 6.1  | A one-shot timer                                  |

| 6.2  | 1 KiB of synchronous memory                       |

| 6.3  | A memory with a forwarding circuit                |

| 7.1  | Summarizing input processing with functions       |

| 8.1  | The Chisel code for the alarm FSM                 |

| 8.2  | Rising edge detection with a Mealy FSM            |

| 8.3  | Rising edge detection with a Moore FSM            |

| 9.1  | Master FSM of the light flasher                   |

| 9.2  | Master FSM of the double refactored light flasher |

| 9.3  | The top level of the popcount circuit             |

| 9.4  | Datapath of the popcount circuit                  |

| 9.5  | The FSM of the popcount circuit                   |

|      | Reading a text file to generate a logic table     |

| 10.2 | Binary to binary-coded decimal conversion         |

| 10.3 | Tick generation with a counter                    |

| 10.4 | A tester for different versions of the ticker     |

| 10.5 | Tick generation with a down counter               |

|      | Tick generation by counting down to -1            |

| 10.7 C         | hiselTest for the ticker tests                          | 31 |

|----------------|---------------------------------------------------------|----|

| 11.1 A         | single stage of the bubble FIFO                         | 37 |

| 11.2 A         | FIFO is composed of an array of FIFO bubble stages      | 38 |

| 11.3 A         | transmitter for a serial port                           | 40 |

| 11.4 A         | single-byte buffer with a ready/valid interface         | 41 |

| 11.5 A         | transmitter with an additional buffer                   | 42 |

| 11.6 A         | receiver for a serial port                              | 43 |

| 11.7 Se        | ending "Hello World!" via the serial port               | 44 |

| 11.8 E         | choing data on the serial port                          | 45 |

| 11.9 A         | bubble FIFO with a ready-valid interface                | 47 |

| 11.10A         | FIFO with double buffer elements                        | 48 |

| 11.11A         | FIFO with a register based memory                       | 50 |

| 11.12A         | FIFO with a on-chip memory                              | 52 |

| 11.13 <b>C</b> | ombining a memory based FIFO with double-buffer stage 1 | 55 |

| 11.14A         | multi-clock memory generator                            | 55 |

| 12.1 TI        | ne Leros ALU                                            | 61 |

|                | ne Leros ALU function written in Scala                  |    |

|                | ne main part of the Leros assembler                     |    |

|                |                                                         |    |

#### **Foreword**

It is an exciting time to be in the world of digital design. With the end of Dennard Scaling and the slowing of Moore's Law, there has perhaps never been a greater need for innovation in the field. Semiconductor companies continue to squeeze out every drop of performance they can, but the cost of these improvements has been rising drastically. Chisel reduces this cost by improving productivity. If designers can build more in less time, while amortizing the cost of verification through reuse, companies can spend less on Non-Recurring Engineering (NRE). In addition, both students and individual contributors can innovate more easily on their own.

Chisel is unlike most languages in that it is embedded in another programming language, Scala. Fundamentally, Chisel is a library of classes and functions representing the primitives necessary to express synchronous, digital circuits. A Chisel design is really a Scala program that *generates* a circuit as it executes. To many, this may seem counterintuitive: "Why not just make Chisel a stand-alone language like VHDL or SystemVerilog?" My answer to this question is as follows: the software world has seen a substantial amount of innovation in design methodology in the past couple of decades. Rather than attempting to adapt these techniques to a new hardware language, we can simply *use* a modern programming language and gain those benefits for free.

A longstanding criticism of Chisel is that it is "difficult to learn." Much of this perception is due to the prevalence of large, complex designs created by experts to solve their own research or commercial needs. When learning a popular language like C++, one does not start by reading the source code of GCC. Rather, there are a plethora of courses, textbooks, and other learning materials that cater toward newcomers. In *Digital Design with Chisel*, Martin has created an important resource for anyone who wishes to learn Chisel.

Martin is an experienced educator, and it shows in the organization of this book. Starting with installation and primitives, he builds the reader's understanding like a building, brick-by-brick. The included exercises are the mortar that solidifies understanding, ensuring that each concept sets in the reader's mind. The book culminates with *hardware generators* like a roof giving the rest of the structure purpose. At the end, the reader is left with the knowledge to build a simple, yet useful design: a RISC processor.

In *Digital Design with Chisel*, Martin has laid a strong foundation for productive digital design. What you build with it is up to you.

Jack Koenig Chisel and FIRRTL Maintainer Staff Engineer, SiFive

#### **Preface**

This book is an introduction to digital design with the focus on using the hardware construction language Chisel. Chisel brings advances from software engineering, such as object-orientated and functional languages, into digital design.

This book addresses hardware designers and software engineers. Hardware designers, with knowledge of Verilog or VHDL, can upgrade their productivity with a modern language for their next ASIC or FPGA design. Software engineers, with knowledge of object-oriented and functional programming, can leverage their knowledge to program hardware, for example, FPGA accelerators executing in the cloud.

The approach of this book is to present small to medium-sized typical hardware components to explore digital design with Chisel.

#### Foreword for the Second Edition

As Chisel allows agile hardware design, so does open access and on-demand printing allow agile textbook publishing. Less than 6 months after the first edition of this book I am able to provide an improved and extended second edition.

Besides minor fixes, the main changes in the second edition are as follows. The testing section has been extended. The sequential building blocks chapter contains more example circuits. A new chapter on input processing explains input synchronization, shows how to design a debouncing circuit, and how to filter a noisy input signal. The example designs chapter has been extended to show different implementations of a FIFO. The FIFO variations also show how to use type parameters and inheritance in digital design.

#### Foreword for the Third Edition

Chisel has been moving forward in the last year, so it is time for a new edition of the Chisel book. We changed all examples to the latest version of Chisel (3.5.0) and the recommended Scala version (2.12.13).

With Chisel 3.5 the testing environment PeekPokeTester as part of the iotesters package has been deprecated. Therefore, we have changed the testing description to the

new ChiselTest framework. As there are still many Chisel designs available that use the PeekPokeTester, we have moved the description for it into the appendix.

One of the fascinating aspects of the Chisel/Scala/Java environment is that we can piggyback on the available infrastructure to distribute open-source libraries. We can publish hardware components on Maven as simply as any other open-source Java library. Publishing on Maven means that a 3rd party component can be integrated into the compile flow with a single reference in the build.sbt configuration. This is the same process as how you include the chisel library for your design. We have added a section on how to publish a Chisel design on Maven Central.

We have improved the explanation of components with a simpler example.

Hardware *generators* are written in Scala. Therefore, we have added a short section on Scala. We have extended the hardware generator chapter with a section on using functional programing to write generators.

The appendix has been extended with a list of reserved keywords and a list of acronyms. Hans has contributed the description on how to use external components, as so called *black boxes*, and how to use memories for clock domain crossing (multi-clock memories).

#### **Acknowledgements**

I want to thank everyone who has worked on Chisel for creating such a cool hardware construction language. Chisel is so joyful to use and therefore worth writing a book about. I am thankful to the whole Chisel community, which is so welcoming and friendly and never tired to answer questions on Chisel.

I would also like to thank my students in the last years of an advanced computer architecture course where most of them picked up Chisel for the final project. Thank you for moving out of your comfort zone and taking up the journey of learning and using a bleeding-edge hardware description language. Many of your questions have helped to shape this book.

It was a pleasure to use Chisel in the last two years of teaching a digital electronics course. I know it is a challenge to pickup Chisel and Java in parallel in the second semester. Thank you to all students from this course, who had on open mind to pickup a modern programming language for hardware description.

For the third edition, I would like to acknowledge Hans Jakob Damsgaard (@hansemandse) for rewriting all test code to ChiselTest, adding ChiselTest to the testing chapter, adding the black box description, and an example for a multi-clock memory.

#### 1 Introduction

This book is an introduction to digital system design using a modern hardware construction language, Chisel [2]. In this book, we focus on a higher abstraction level than usual in digital design books, to enable you to build more complex, interacting digital systems in a shorter time.

This book and Chisel are targeting two groups of developers: (1) hardware designers and (2) software programmers. Hardware designers who are fluent in VHDL or Verilog and using other languages such as Python, Java, or Tcl to generate hardware can move to a single hardware construction language where hardware generation is part of the language. Software programmers may become interested in hardware design, e.g., as future chips from Intel will include programmable hardware to speed up programs. It is perfectly fine to use Chisel as your first hardware description language.

Chisel brings advances in software engineering, such as object-orientated and functional languages, into digital design. Chisel does not only allow to express hardware at the register-transfer level but allows you to write hardware generators.

Hardware is now commonly described with a hardware description language. The time of drawing hardware components, even with CAD tools, is over. Some high-level schematics can give an overview of the system but are not intended to describe the system. The two most common hardware description languages are Verilog and VHDL. Both languages are old, contain many legacies, and have a moving line of what constructs of the language are synthesizable to hardware. Do not get me wrong: VHDL and Verilog are perfectly able to describe a hardware block that can be synthesized into an ASIC. For hardware design in Chisel, Verilog serves as an intermediate language for testing and synthesis.

This book is not a general introduction to hardware design and the fundamentals of it. For an introduction of the basics in digital design, such as how to build a gate out of CMOS transistors, refer to other digital design books. However, this book intends to teach digital design at an abstraction level that is current practice to describe ASICs or designs targeting FPGAs.<sup>1</sup> As prerequisites for this book, we assume basic knowledge of Boolean algebra and the binary number system. Furthermore, some programming ex-

<sup>&</sup>lt;sup>1</sup>As the author is more familiar with FPGAs than ASICs as target technology, some design optimizations shown in this book are targeting FPGA technology.

perience in any programming language is assumed. No knowledge of Verilog or VHDL is needed. Chisel can be your first programming language to describe digital hardware. As the build process in the examples is based on sbt and make, basic knowledge of the command-line interface (CLI, also called terminal or Unix shell) will be helpful.

Chisel itself is not a big language. The basic constructs fit on one page and can be learned within a few days. Therefore, this book is not a big book, as well. Chisel is for sure smaller than VHDL and Verilog, which carry many legacies. The power of Chisel comes from the embedding of Chisel within Scala, which itself in an expressive language. Chisel inherits the feature from Scala being "a language that grows on you" [12]. However, Scala is not the topic of this book. We provide a short section on Scala for hardware designers. The textbook by Odersky et al. [12] provides a general introduction to Scala. This book is a tutorial in digital design and the Chisel language; it is not a Chisel language reference, nor is it a book on complete chip design.

All code examples shown in this book are extracted from complete programs that have been compiled and tested. Therefore, the code shall not contain any syntax errors. The code examples are available from the GitHub repository of this book. Besides showing Chisel code, we have also tried to show useful designs and principles of good hardware description style.

This book is optimized for reading on a laptop or tablet (e.g., an iPad). We include links to further reading in the running text, mostly to Wikipedia articles.

#### 1.1 Installing Chisel and FPGA Tools

Chisel is a Scala library, and the easiest way to install Chisel and Scala is with sbt, the Scala build tool. Scala itself depends on the installation of Java JDK 1.8 (or a later version). As Oracle has changed the license for Java, it may be easier to install OpenJDK from AdoptOpenJDK.

More detailed setup instructions can be found in Setup.md from the chisel-leb. The first lab explains how to open an existing Chisel project in IntelliJ.

#### 1.1.1 macOS

Install the Java OpenJDK 8 from AdoptOpenJDK. On Mac OS X, with the packet manager Homebrew, sbt and git can be installed with:

\$ brew install sbt git

Install GTKWave and IntelliJ (the community edition). When importing a project, select the JDK 1.8 you installed before.

#### 1.1.2 Linux/Ubuntu

Install Java and useful tools in Ubuntu with:

```

$ sudo apt install openjdk-8-jdk git make gtkwave

```

For Ubuntu, which is based on Debian, programs are usually installed from a Debian file (.deb). However, as of the time of this writing, sbt is not available as a ready to install package. Therefore, the installation process is a little bit more involved. Follow the instructions from sbt download

#### 1.1.3 Windows

Install the Java OpenJDK from AdoptOpenJDK. Chisel and Scala can also be installed and used under Windows. Install GTKWave and IntelliJ (the community edition). When importing a project, select the JDK 1.8 you installed before. sbt can be installed with a Windows installer, see: Installing sbt on Windows. Install a git client.

#### 1.1.4 FPGA Tools

To build hardware for an FPGA, you need a synthesize tool. The two major FPGA vendors, Intel<sup>2</sup> and Xilinx, provide free versions of their tools that cover small to medium-sized FPGAs. Those medium-sized FPGAs are large enough to build multicore RISC style processors. Intel provides the Quartus Prime Lite Edition and Xilinx the Vivado Design Suite, WebPACK Edition. Both tools are available for Windows and Linux, but not for macOS.

#### 1.2 Hello World

Each book on a programming language shall start with a minimal example, called the *Hello World* example. Following code is the first approach:

```

object HelloScala extends App{

println("Hello Chisel World!")

}

```

Compiling and executing this short program with sbt

\$ sbt run

<sup>&</sup>lt;sup>2</sup>former Altera

```

class Hello extends Module {

val io = IO(new Bundle {

val led = Output(UInt(1.W))

})

val CNT_MAX = (500000000 / 2 - 1).U

val cntReg = RegInit(0.U(32.W))

val blkReg = RegInit(0.U(1.W))

cntReg := cntReg + 1.U

when(cntReg === CNT_MAX) {

cntReg := 0.U

blkReg := ~blkReg

}

io.led := blkReg

}

```

Listing 1.1: A hardware Hello World in Chisel

leads to the expected output of a Hello World program:

```

[info] Running HelloScala

Hello Chisel World!

```

However, is this Chisel? Is this hardware generated to print a string? No, this is plain Scala code and not a representative Hello World program for a hardware design.

#### 1.3 Chisel Hello World

What is then the equivalent of a Hello World program for a hardware design? The minimal useful and visible design? A blinking LED is the hardware (or even embedded software) version of Hello World. If a LED blinks, we are ready to solve bigger problems!

Listing 1.1 shows a blinking LED, described in Chisel. It is not important that you understand the details of this code example. We will cover those in the following chapters. Just note that the circuit is usually clocked with a high frequency, e.g., 50 MHz, and we need a counter to derive timing in the Hz range to achieve a visible blinking. In the above example, we count from 0 up to 25000000-1 and then toggle the blinking sig-

nal (blkReg := ~blkReg) and restart the counter (cntReg := 0.U). That hardware then blinks the LED at 1 Hz.

#### 1.4 An IDE for Chisel

This book makes no assumptions about your programming environment or editor you use. Learning the basics should be easy with just using sbt at the command line and an editor of your choice. In the tradition of other books, all commands that you shall type in a shell/terminal/CLI are preceded by a \$ character, which you shall not type in. As an example, here is the Unix 1s command, which lists files in the current folder:

#### \$ 1s

That said, an integrated development environment (IDE), where a compiler is running in the background, can speed up coding. As Chisel is a Scala library, all IDEs that support Scala are also good IDEs for Chisel. It is possible in IntelliJ and Eclipse to generate a project from the sbt project configuration in build.sbt.

In IntelliJ you can create a new project from existing sources with: File - New - Project from Existing Sources... and then select the build.sbt file from the project.

In Eclipse you can create a project via

#### \$ sbt eclipse

and import that project into Eclipse.<sup>3</sup>

Visual Studio Code is another option for a Chisel IDE. The Scala Metals extension provides Scala support. On the left bar select *Extensions* and search for *Metals* and install *Scala* (*Metals*). To import an sbt based project open the folder with *File - Open*.

#### 1.5 Source Access and eBook Features

This book is open source and hosted at GitHub: schoeberl/chisel-book. All Chisel code examples, shown in this book, are included in the repository. All code shown in the book passed the compiler and therefore should not contain any syntax errors. Furthermore, most examples also include a test bench. The code is extracted automatically from that source. We collect larger Chisel examples in the accompanying repository chisel-examples and in ip-contributions.

<sup>&</sup>lt;sup>3</sup>This function needs the Eclipse plugin for sbt.

If you find an error or typo in the book, a GitHub pull request is the most convenient way to incorporate your improvement. You can also provide feedback or comments for improvements by filing an issue on GitHub or sending a plain, old school email.

The repository of the book also contains slides in Latex that I use for a 13 week course on Digital Electronics<sup>4</sup> at the Technical University of Denmark. That course also contains lab exercises in Chisel. If you are teaching digital design with Chisel, feel free to adapt the slides and lab exercises to your needs. All material is open-source. To build the book and slides you need a recent version of Latex and the needed tools for Chisel (sbt and a Java JDK installation). All code is compiled, tested, extracted, and the Latex compiled with a simple:

#### \$ make

This book is freely available as a PDF eBook and in classical printed form Amazon. The eBook version features links to further resources and Wikipedia entries. We use Wikipedia entries for background information (e.g., binary number system) that does not directly fit into this book. We optimized the format of the eBook for reading on a tablet, such as an iPad.

#### 1.6 Further Reading

Here a list of further reading for digital design and Chisel:

• Digital Design: A Systems Approach, by William J. Dally and R. Curtis Harting, is a modern textbook on digital design. It is available in two versions: using Verilog or VHDL as a hardware description language.

The official Chisel documentation and further documents are available online:

- The Chisel home page is the official starting point to download and learn Chisel.

- The Chisel Tutorial provides a ready setup project containing small exercises with testers and solutions.

- ChiselTest is in its own repository.

- The Generator Bootcamp is a Chisel course focusing on hardware generators, as a Jupyter notebook

- A Chisel Style Guide by Christopher Celio.

<sup>&</sup>lt;sup>4</sup>The course page contains the PDF versions of the slides

- The schoeberl/chisel-lab GitHub repo contains Chisel exercises for the course "Digital Electronics 2" at the Technical University of Denmark.

- The empty Chisel project is a good starting point with a very minimal hardware (an adder) and test. That project is a GitHub template where you base your GitHub repository on.

#### 1.7 Exercise

Each chapter ends with a hands-on exercise. For the introduction exercise, we will use an FPGA board to get one LED blinking.<sup>5</sup> As a first step clone (or fork) the chisel-examples repository from GitHub. The Hello World example is in the folder hello-world, set up as a minimal project. You can explore the Chisel code of the blinking LED in src/main/scala/Hello.scala. Compile the blinking LED with the following steps:

```

$ git clone https://github.com/schoeberl/chisel-examples.git

$ cd chisel-examples/hello-world/

$ sbt run

```

After some initial downloading of Chisel components, this will produce the Verilog file Hello.v. Explore this Verilog file. You will see that it contains two inputs clock and reset and one output io\_led. When you compare this Verilog file with the Chisel module, you will notice that the Chisel module does not contain clock or reset. Those signals are implicitly generated, and in most designs, it is convenient not to need to deal with these low-level details. Chisel provides register components, and those are connected automatically to clock and reset (if needed).

The next step is to set up an FPGA project file for the synthesize tool, assign the pins, compile<sup>6</sup> the Verilog code, and configure the FPGA with the resulting bitfile. We cannot provide the details of these steps. Please consult the manual of your Intel Quartus or Xilinx Vivado tool. However, the examples repository contains some ready to use Quartus projects in folder quartus for several popular FPGA boards (e.g., DE2-115). If the repository contains support for your board, start Quartus, open the project, compile it by pressing the *Play* button, and configure the FPGA board with the *Programmer* button and one of the LEDs should blink.

<sup>&</sup>lt;sup>5</sup>If you at the moment have no FPGA board available, continue to read as we will show you a simulation version at the end of the exercise.

<sup>&</sup>lt;sup>6</sup>The real process is more elaborated with following steps: synthesizing the logic, performing place and route, performing timing analysis, and generating a bitfile. However, for the purpose of this introduction example we simply call it "compile" your code.

## Congratulations! You managed to get your first design in Chisel running in an FPGA!

If the LED is not blinking, check the status of reset. On the DE2-115 configuration, the reset input is connected to SW0.

Now change the blinking frequency to a slower or a faster value and rerun the build process. Blinking frequencies and also blinking patterns communicate different "emotions". E.g., a slow blinking LED signals that everything is ok, a fast blinking LED signals an alarm state. Explore which frequencies express best those two different emotions.

As a more challenging extension to the exercise, generate the following blinking pattern: the LED shall be on for 200 ms every second. For this pattern, you might decouple the change of the LED blinking from the counter reset. You will need a second constant where you change the state of the blkReg register. What kind of emotion does this pattern produce? Is it alarming or more like a sign-of-live signal?

If you do not have an FPGA board (yet), you can still run the blinking LED example. You will use the Chisel simulation. To avoid a too long simulation time change the clock frequency in the Chisel code from 50000000 to 50000. Execute following instruction to simulate the blinking LED:

#### \$ sbt test

This will execute the tester that runs for one million clock cycles. The blinking frequency depends on the simulation speed, which depends on the speed of your computer. Therefore, you might need to experiment a little bit with the assumed clock frequency to see the simulated blinking LED.

### 2 Basic Components

In this section, we introduce the basic components for digital design: combinational circuits and flip-flops. These essential elements can be combined to build larger, more interesting circuits.

Digital systems in general built use binary signals, which means a single bit or signal can only have one of two possible values. These values are often called 0 and 1. However, we also use following terms: low/high, false/true, and de-asserted/asserted. These terms mean the same two possible values of a binary signal.

#### 2.1 Signal Types and Constants

Chisel provides three data types to describe signals, combinational logic, and registers: Bits, UInt, and SInt. UInt and SInt extend Bits, and all three types represent a vector of bits. UInt gives this vector of bits the meaning of an unsigned integer and SInt of a signed integer. Chisel uses two's complement as signed integer representation. Here is the definition for different types, an 8-bit Bits, an 8-bit unsigned integer, and a 10-bit signed integer:

```

Bits(8.W)

UInt(8.W)

SInt(10.W)

```

The width of a vector of bits is defined by a Chisel width type (Width). The following expression casts the Scala integer n to a Chisel width, which is used for the definition of the Bits vector:

```

n.W

Bits(n.W)

```

Constants can be defined by using a Scala integer and converting it to a Chisel type:

```

0.U // defines a UInt constant of 0

```

<sup>&</sup>lt;sup>1</sup>The type Bits in the current version of Chisel is missing operations and therefore not very useful for user code.

```

-3.S // defines a SInt constant of -3

```

Constants can also be defined with a width, by using the Chisel width type:

```

3.U(4.W) // An 4-bit constant of 3

```

If you find the notation of 3.U and 4.W a little bit funny, consider it as a variant of an integer constant with a type. This notation is similar to 3L, representing a long integer constant in C, Java, and Scala.

**Possible pitfall:** One possible error when defining constants with a dedicated width is missing the .W specifier for a width. E.g., 1.U(32) will *not* define a 32-bit wide constant representing 1. Instead, the expression (32) is interpreted as bit extraction from position 32, which results in a single bit constant of 0. Probably not what the original intention of the programmer was.

Chisel benefits from Scala's type inference and in many places type information can be left out. The same is also valid for bit widths. In many cases, Chisel will automatically infer the correct width. Therefore, a Chisel description of hardware is more concise and better readable than VHDL or Verilog.

For constants defined in other bases than decimal, the constant is defined in a string with a preceding h for hexadecimal (base 16), o for octal (base 8), and b for binary (base 2). The following example shows the definition of constant 255 in different bases. In this example we omit the bit width and Chisel infers the minimum width to fit the constants in, in this case 8 bits.

The above code shows how to use an underscore to group digits in the string that represents a constant. The underscore is ignored.

Characters to represent text (in ASCII encoding) can also be used as constants in Chisel:

```

val aChar = 'A'.U

```

To represent logic values, Chisel defines the type Bool. Bool can represent a *true* or *false* value. The following code shows the definition of type Bool and the definition of Bool constants, by converting the Scala Boolean constants true and false to Chisel Bool constants.

```

Bool()

```

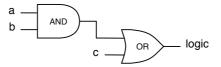

Figure 2.1: Logic for the expression (a & b) | c. The wires can be a single bit or multiple bits. The Chisel expression, and the schematics are the same.

```

true.B

false.B

```

#### 2.2 Combinational Circuits

Chisel uses Boolean algebra operators, as they are defined in C, Java, Scala, and several other programming languages, to described combinational circuits: & is the AND operator and | is the OR operator. Following line of code defines a circuit that combines signals a and b with *and* gates and combines the result with signal c with *or* gates and names it logic.

```

val logic = (a & b) | c

```

Figure 2.1 shows the schematic of this combinatorial expression. Note that this circuit may be for a vector of bits and not only single wires that are combined with the AND and OR circuits.

In this example, we do not define the type nor the width of signal logic. Both are inferred from the type and width of the expression. The standard logic operations in Chisel are:

```

val and = a & b // bitwise and

val or = a | b // bitwise or

val xor = a ^ b // bitwise xor

val not = ~a // bitwise negation

```

The arithmetic operations use the standard operators:

```

val add = a + b // addition

val sub = a - b // subtraction

val neg = -a // negate

val mul = a * b // multiplication

```

```

val div = a / b // division

val mod = a % b // modulo operation

```

The resulting width of the operation is the maximum width of the operators for addition and subtraction, the sum of the two widths for the multiplication, and usually the width of the numerator for divide and modulo operations.<sup>2</sup>

A signal can also first be defined as a Wire of some type. Afterward, we can assign a value to the wire with the := update operator.

```

val w = Wire(UInt())

w := a & b

```

A single bit can be extracted as follows:

```

val sign = x(31)

```

A subfield can be extracted from end to start position:

```

val lowByte = largeWord(7, 0)

```

Bit fields are concatenated with the ## operator.<sup>3</sup>

```

val word = highByte ## lowByte

```

Table 2.1 shows the full list of operators (see also builtin operators). The Chisel operator precedence is determined by the evaluation order of the circuit, which follows the Scala operator precedence. If in doubt, it is always a good practice to use parentheses.<sup>4</sup>

Table 2.2 shows various functions defined on and for Chisel data types.

#### 2.2.1 Multiplexer

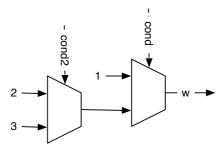

A multiplexer is a circuit that selects between alternatives. In the most basic form, it selects between two alternatives. Figure 2.2 shows such a 2:1 multiplexer, or mux for

<sup>&</sup>lt;sup>2</sup>The exact details are available in the FIRRTL specification.

<sup>&</sup>lt;sup>3</sup>Note, that there is a Cat function available that performs the same operation with Cat(highByte, lowByte).

<sup>&</sup>lt;sup>4</sup>The operator precedence in Chisel is a side effect of the hardware elaboration when the tree of hardware nodes is created by executing the Scala operators. The Scala operator precedence is similar but not identical to Java/C. Verilog has the same operator precedence as C, but VHDL has a different one. Verilog has precedence ordering for logic operations, but in VHDL those operators have the same precedence and are evaluated from left to right.

| Operator  | Description                                   | Data types               |

|-----------|-----------------------------------------------|--------------------------|

| * / %     | multiplication, division, modulus             | UInt, SInt               |

| + -       | addition, subtraction                         | UInt, SInt               |

| === =/=   | equal, not equal                              | UInt, SInt, returns Bool |

| > >= < <= | comparison                                    | UInt, SInt, returns Bool |

| << >>     | shift left, shift right (sign extend on SInt) | UInt, SInt               |

| ~         | NOT                                           | UInt, SInt, Bool         |

| &   ^     | AND, OR, XOR                                  | UInt, SInt, Bool         |

| !         | logical NOT                                   | Bool                     |

| &&        | logical AND, OR                               | Bool                     |

Table 2.1: Chisel defined hardware operators.

| Function                                                                       | Description                                                                                                                                                       | Data types                                                                                 |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <pre>v.andR v.orR v.xorR v(n) v(end, start) Fill(n, v) a ## b Cat(a, b,)</pre> | AND, OR, XOR reduction<br>extraction of a single bit<br>bitfield extraction<br>bitstring replication, n times<br>bitfield concatenation<br>bitfield concatenation | UInt, SInt, returns Bool UInt, SInt UInt, SInt UInt, SInt UInt, SInt UInt, SInt UInt, SInt |

Table 2.2: Chisel defined hardware functions, invoked on v.

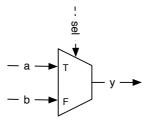

Figure 2.2: A basic 2:1 multiplexer.

short. Depending on the value of the select signal (sel) signal y will represent signal a or signal b.

A multiplexer can be built from logic. However, as multiplexing is such a standard operation, Chisel provides a multiplexer,

```

val result = Mux(sel, a, b)

```

where a is selected when the sel is true.B, otherwise b is selected. The type of sel is a Chisel Bool; the inputs a and b can be any Chisel base type or aggregate (bundles or vectors) as long as they are the same type.

With logical and arithmetical operations and a multiplexer, every combinational circuit can be described. However, Chisel provides further components and control abstractions for a more elegant description of a combinational circuit, which are described in a later chapter.

The second basic component needed to describe a digital circuit is a state element, also called register, which is described next.

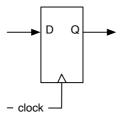

#### 2.3 Registers

Chisel provides a register, which is a collection of D flip-flops. The register is implicitly connected to a global clock and is updated on the rising edge. When an initialization value is provided at the declaration of the register, it uses a synchronous reset connected to a global reset signal. A register can be any Chisel type that can be represented as a collection of bits. Following code defines an 8-bit register, initialized with 0 at reset:

```

val reg = RegInit(0.U(8.W))

```

An input is connected to the register with the := update operator and the output of the

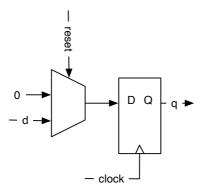

Figure 2.3: A D flip-flop based register with a synchronous reset to 0.

register can be used just with the name in an expression:

```

reg := d

val q = reg

```

A register can also be connected to its input at the definition:

```

val nextReg = RegNext(d)

```

Figure 2.3 shows the circuit of our register definition with a clock, a synchronous reset to 0.U, input d, and output q. The global signals clock and reset are implicitly connected to each register defined.

A register can also be connected to its input and a constant as initial value at the definition:

```

val bothReg = RegNext(d, 0.U)

```

To distinguish between signals representing combinational logic and registers, a common practice is to postfix register names with Reg. Another common practice, coming from Java and Scala, is to use camelCase for identifier consisting of several words. The convention is to start functions and variables with a lower case letter and classes (types), e.g., a Module name, with an upper case letter.

In Chisel you are relative free to name your identifiers. However, use taste and descriptive names. Furthermore, several words are reserved. They are listed in Appendix A.

#### 2.3.1 Counting

Counting is a fundamental operation in digital systems. One might count events. However, more often counting is used to define a time interval. Counting the clock cycles and triggering an action when the time interval has expired.

A simple approach is counting up to a value. However, in computer science, and digital design, counting starts at 0. Therefore, if we want to count till 10, we count from 0 to 9. The following code shows such a counter that counts till 9 and wraps around to 0 when reaching 9.

```

val cntReg = RegInit(0.U(8.W))

cntReg := Mux(cntReg === 9.U, 0.U, cntReg + 1.U)

```

#### 2.4 Structure with Bundle and Vec

Chisel provides two constructs to group related signals: (1) a Bundle to group signals of different types and (2) a Vec to represent an indexable collection of signals of the same type. Bundles and Vecs can be arbitrarily nested.

A Chisel bundle groups several signals. The entire bundle can be referenced as a whole, or individual fields can be accessed by their name. We can define a bundle (collection of signals) by defining a class that extends Bundle and list the fields as vals within the constructor block.

```

class Channel() extends Bundle {

val data = UInt(32.W)

val valid = Bool()

}

```

To use a bundle, we create it with new and wrap it into a Wire. The fields are accessed with the dot notation:

```

val ch = Wire(new Channel())

ch.data := 123.U

ch.valid := true.B

```

Dot notation is common in object-oriented languages, where x.y means x is a reference to an object and y is a field of that object. As Chisel is object-oriented, we use dot

notation to access fields in a bundle. A bundle is similar to a struct in C, a record in VHDL, or a struct in SystemVerilog. A bundle can also be referenced as a whole:

```

val channel = ch

```

A Chisel Vec represents a collection of signals of the same type (a vector). Each element can be accessed by an index. A Chisel Vec is similar to array data structures in other programming languages.<sup>5</sup> A Vec is created by calling the constructor with two parameters: the number of elements and the type of the elements. A combinational Vec needs to be wrapped into a Wire

```

val v = Wire(Vec(3, UInt(4.W)))

```

Individual elements are accessed with (index).

```

v(0) := 1.U

v(1) := 3.U

v(2) := 5.U

val idx = 1.U(2.W)

val a = v(idx)

```

A vector wrapped into a Wire is a multiplexer. We can also wrap a vector into a register to define an array of registers. Following example defines a register file for a processor; 32 registers each 32-bits wide, as for a classic 32-bit RISC processor, like the 32-bit version of RISC-V.

```

val registerFile = Reg(Vec(32, UInt(32.W)))

```

An element of that register file is accessed with an index and used as a normal register.

```

registerFile(idx) := dIn

val dOut = registerFile(idx)

```

We can freely mix bundles and vectors. When creating a vector with a bundle type, we need to pass a prototype for the vector fields. Using our Channel, which we defined above, we can create a vector of channels with:

```

val vecBundle = Wire(Vec(8, new Channel()))

```

A bundle may as well contain a vector:

<sup>&</sup>lt;sup>5</sup>The name Array is already used in Scala.

```

class BundleVec extends Bundle {

val field = UInt(8.W)

val vector = Vec(4,UInt(8.W))

}

```

When we want a register of a bundle type that needs a reset value, we first create a Wire of that bundle, set the individual fields as needed, and then passing this bundle to a RegInit:

```

val initVal = Wire(new Channel())

initVal.data := 0.U

initVal.valid := false.B

val channelReg = RegInit(initVal)

```

With combinations of Bundles and Vecs we can define our own data structures, which are powerful abstractions.

**Possible pitfall:** In Chisel partial assignments are not allowed, although they haven been allowed in Chisel 2 and are possible in Verilog and VHDL. Following code will generate an error during circuit elaboration:

```

val assignWord = Wire(UInt(16.W))

assignWord(7, 0) := lowByte

assignWord(15, 8) := highByte

```

The argument is that it would be better to use bundles for this use case. One possible workaround for this issue is to create a (local) bundle, create a Wire from that bundle, assign the individual fields, casting that bundle with asUInt() to a UInt, and assigning this value to the target UInt. Note, that we define here a Bundle as a local data structure as we need it only locally.

```

val assignWord = Wire(UInt(16.W))

class Split extends Bundle {

val high = UInt(8.W)

val low = UInt(8.W)

}

val split = Wire(new Split())

split.low := lowByte

```

```

split.high := highByte

assignWord := split.asUInt()

```

The small drawback of this solution is that one needs to know in which orders bundle fields are merged to a singe bit vector. Another option is to use a vector of Bool to individually assign values and then convert it to a UInt.

```

val vecResult = Wire(Vec(4, Bool()))

// example assignments

vecResult(0) := data(0)

vecResult(1) := data(1)

vecResult(2) := data(2)

vecResult(3) := data(3)

val uintResult = vecResult.asUInt

```

# 2.5 Wire, Reg, and IO

UInt, SInt, and Bits are Chisel types, which themself do not represent hardware. Only wrapping them into a Wire, Reg, or IO generates hardware. A Wire represents combinational logic, a Reg represents a register (collection of D flip-flops), and an IO represents a connection of a module (like pins of a concrete integrated circuit (IC)). Wire, Reg, or IO can be wrapped over any Chisel type, also a Bundle or a Vec.

You can give a hardware component a name by assigning it to a Scala immutable variables:<sup>6</sup>

```

val number = Wire(UInt())

val reg = Reg(SInt())

```

You can later assign (or reassign) a value or expression to a Wire, Reg, or IO with the Chisel operator :=

```

number := 10.U

reg := value - 3.U

```

Note the small difference between the Scala assignment operator "=" and the Chisel operator ":=". You use Scala's "=" operator when *creating* a hardware object but you

<sup>&</sup>lt;sup>6</sup>Scala also supports mutable variables with var, but those are of no use when describing hardware in Chisel

use Chisel's ":=" operator when assigning or reassigning a value to an *existing* hardware object.

Combinational values can be conditionally assigned, but need to be assigned in every branch of the condition. Otherwise, one would describe a latch, which the Chisel compiler will reject. Best practice is to already define a default value at the creation of the Wire. Therefore, the former code is better rewritten as follows.

```

val number = WireDefault(10.U(4.W))

```

Although Chisel infers the needed bit width for signals and register, it is also a good practice to specify the intended bit width at the creation of the hardware object. In most cases it is also good practice to set registers to known initial values on reset:<sup>7</sup>

```

val reg = RegInit(0.S(8.W))

```

## 2.6 Chisel Generates Hardware

After seeing some initial Chisel code, it might look similar to classic programming languages such as Java or C. However, Chisel (or any other hardware description language) does define hardware components. While in a software program one line of code after the other is executed, in hardware all lines of code *execute in parallel*.

It is essential to keep in mind that Chisel code does generate hardware. Try to imagine, or draw on a sheet of paper, the individual blocks that are generated by your Chisel circuit description. Each creation of a component adds hardware; each assignment statement generates gates and/or flip-flops.

More technically, when Chisel executes your code it runs as a Scala program, and by executing the Chisel statements, it *collects* the hardware components and connects those nodes. This network of hardware nodes is the hardware, which can spill out Verilog code for ASIC or FPGA synthesis or can be tested with a Chisel tester. The network of hardware nodes is what is executed in fully parallel.

For a software engineer imagine this immense parallelism that you can create in hardware without needing to partition your application into threads and getting the locking correct for the communication.

<sup>&</sup>lt;sup>7</sup>Leaving the register value undefined on reset may save some load on the reset wire. However, testing and verification is simplified with known reset values.

## 2.7 Exercise

In the introduction you implemented a blinking LED on an FPGA board (from chiselexamples), which is a reasonable hardware *Hello World* example. It used only internal state, a single LED output, and no input. Copy that project into a new folder and extend it by adding some inputs to the io Bundle with val sw = Input(UInt(2.W)).

```

val io = IO(new Bundle {

val sw = Input(UInt(2.W))

val led = Output(UInt(1.W))

})

```

For those switches, you also need to assign the pin names for the FPGA board. You can find examples of pin assignments in the Quartus project files of the ALU project (e.g., for the DE2-115 FPGA board).

When you have defined those inputs and the pin assignment, start with a simple test: drop all blinking logic from the design and connect one switch to the LED output; compile and configure the FPGA device. Can you switch the LED on an off with the switch? If yes, you have now inputs available. If not, you need to debug your FPGA configuration. The pin assignment can also be done with the GUI version of the tool.

Now use two switches and implement one of the basic combinational functions, e.g., AND two switches and show the result on the LED. Change the function. The next step involves three input switches to implement a multiplexer: one acts as a select signal, and the other two are the two inputs for the 2:1 multiplexer.

Now you have been able to implement simple combinational functions and test them in real hardware in an FPGA. As a next step, we will take a first look at how the build process works to generate an FPGA configuration. Furthermore, we will also explore a simple testing framework from Chisel, which allows you to test circuits without configuring an FPGA and toggle switches.

# 3 Build Process and Testing

To get started with more interesting Chisel code we first need to learn how to compile Chisel programs, how to generate Verilog code for execution in an FPGA, and how to write tests for debugging and to verify that our circuits are correct. A more detailed description on debugging, testing, and verification is given in Chapter ??.

Chisel is written in Scala, so any build process that supports Scala is possible with a Chisel project. One popular build tool for Scala is sbt, which stands for the Scala interactive build tool. Besides driving the build and test process, sbt also downloads the correct version of Scala and the Chisel libraries.

# 3.1 Building your Project with sbt

The Scala library that represents Chisel and the Chisel testers are automatically down-loaded during the build process from a Maven repository. The libraries are referenced by build.sbt. It is possible to configure build.sbt with latest.release to always use the most actual version of Chisel. However, this means on each build the version is looked up from the Maven repository. This lookup needs an Internet connection for the build to succeed. Better use a dedicated version of Chisel and all other Scala libraries in your build.sbt. Maybe sometimes it is also good to be able to write hardware code and test it without an Internet connection. For example, it is cool to do hardware design on a plane.

## 3.1.1 Source Organization

sbt inherits the source convention from the Maven build automation tool. Maven also organizes repositories of open-source Java libraries.<sup>1</sup>

Figure 3.1 shows the organization of the source tree of a typical Chisel project. The root of the project is the project home, which contains build.sbt. It may also include a Makefile for the build process, a README, and a LICENSE file. Folder src contains all source code. From there it is split between main, containing the hardware sources

<sup>&</sup>lt;sup>1</sup>That is also the place where you downloaded the Chisel library on your first build: https://mvnrepository.com/artifact/edu.berkeley.cs/chisel3.

Figure 3.1: Source tree of a Chisel project (using sbt)

and test containing testers. Chisel inherits from Scala, which inherits from Java the organization of source in packages. Packages organize your Chisel code into namespaces. Packages can also contain sub-packages. The folder target contains the class files and other generated files. I recommend to also use a folder for generated Verilog files, which is usually call generated.

To use the facility of namespaces in Chisel, you need to declare that a class/module is defined in a package, in this example in mypack:

```

package mypack

import chisel3._

class Abc extends Module {

val io = IO(new Bundle{})

}

```

Note that in this example we see the import of the chisel3 package to use Chisel classes.

To use the module Abc in a different context (package name space), the components of packet mypack need to be imported. The underscore (\_) acts as wildcard, meaning that all classes of mypack are imported.

```

import mypack._

class AbcUser extends Module {

val io = IO(new Bundle{})

```

```

val abc = new Abc()

}

```

It is also possible to not import all types from mypack, but use the fully qualified name mypack. Abc to refer to the module Abc in package mypack.

```

class AbcUser2 extends Module {

val io = IO(new Bundle{})

val abc = new mypack.Abc()

}

```

It is also possible to import just a single class and create an instance of it:

```

import mypack.Abc

class AbcUser3 extends Module {

val io = IO(new Bundle{})

val abc = new Abc()

}

```

## 3.1.2 Running sbt

A Chisel project can be compiled and executed with a simple sbt command:

```

$ sbt run

```

This command will compile all your Chisel code from the source tree and searches for classes that contain an object that includes a main method, or simpler that extends App. If there is more than one such object, all objects are listed and one can be selected. You can also directly specify the object that shall be executed as a parameter to sbt:

```

$ sbt "runMain mypacket.MyObject"

```

Per default sbt searches only the main part of the source tree and not the test part.<sup>2</sup> To execute tests based in ChiselTest and ScalaTest you can simply run them with

<sup>&</sup>lt;sup>2</sup>This is a convention form Java/Scala that the test folder contains unit tests and not objects with a main.

#### \$ sbt test

If you have a test that does not follow the ChiselTest convention and it contains a main function, but is placed in the test part of the source tree you can execute it with following sbt command:

\$ sbt "test:runMain mypacket.MyMainTest"

#### 3.1.3 Generating Verilog

To synthesize the Chisel code for an FPGA or ASIC we need to translate Chisel into a hardware description language that a synthesize tool understands. With Chisel we can generate a synthesizable Verilog description of the circuit.

To generate the Verilog description, we need an application. A Scala object that extends App is an application that implicitly generates the main function where the application starts. The only action of this application is to create a new Hello object and pass it to the Chisel emitVerilog() function. The following code will generate the Verilog file Hello.v.

```

object Hello extends App {

emitVerilog(new Hello())

}

```

However, just using the default version of emitVerilog() will put the generated files into the root folder of our project (where we run the sbt command). To put the generated files into a subfolder, we need to specify options to emitVerilog(). I recommend to specify a folder generated, as shown in Figure 3.1. The build options can be set as a second argument, which is an array of Strings, The following code will generate the Verilog file Hello.v in the subfolder generated.

```

object HelloOption extends App {

emitVerilog(new Hello(), Array("--target-dir", "generated"))

}

```

You can also request the Verilog code as a Scala String without writing a file. You can simply print out the string for testing.

```

object HelloString extends App {

val s = getVerilogString(new Hello())

println(s)

}

```

This form of output is popular when showing small Chisel examples in Scastie. See as an example the Hello World on Scastie.

#### 3.1.4 Tool Flow

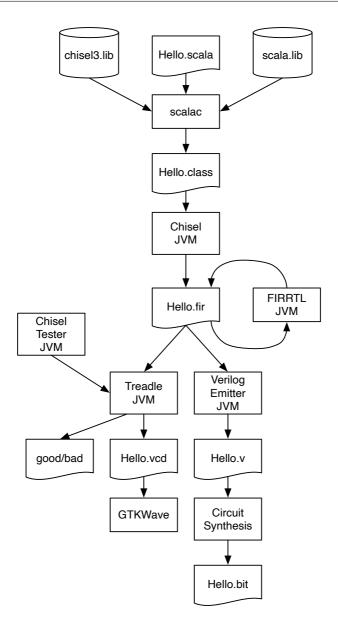

Figure 3.2 shows the tool flow of Chisel. The digital circuit is described in a Chisel class shown as Hello.scala. The Scala compiler compiles this class, together with the Chisel and Scala libraries, and generates the Java class Hello.class that can be executed by a standard Java virtual machine (JVM). Executing this class with a Chisel driver generates the so-called flexible intermediate representation for RTL (FIRRTL), an intermediate representation of digital circuits. In our example the file is Hello.fir. The FIRRTL compiler performs transformations on the circuit.

Treadle is a FIRRTL interpreter to simulate the circuit. Together with the Chisel tester it can be used to debug and test Chisel circuits. With assertions we can provide test results. Treadle can also generate waveform files (Hello.vcd) that can be viewed with a waveform viewer (e.g., the free viewer GTKWave or Modelsim).

One FIRRTL transformation, the Verilog emitter, generates Verilog code for synthesis (Hello.v). A circuit synthesize tool (e.g., Intel Quartus, Xilinx Vivado, or an ASIC tool) synthesizes the circuit. In an FPGA design flow, the tool generates the FPGA bitstream that is used to configure the FPGA, e.g., Hello.bit.

Now that we know the basic structure of a Chisel project and how to compile and run it with sbt, we can continue with a simple testing framework.

# 3.2 Testing with Chisel

Tests of hardware designs are usually called test benches. The test bench instantiates the design under test (DUT), drives input ports, observes output ports, and compares them with expected values. Chisel provides two testing methods, the ChiselTest in package chiseltest and the older PeekPokeTester in package iotesters.<sup>3</sup> Here we describe the ChiselTest method.

One strength of Chisel is that it can use the full power of Scala to write those test benches. One can, for example, code the expected functionality of the hardware in a software simulator and compare the simulation of the hardware with the software simulation. This method is very efficient when testing an implementation of a processor [6].

$<sup>^3</sup>$ iotesters is deprecated since Chisel 3.5. A description how to use the PeekPokeTester can be found in Appendix D

Figure 3.2: Tool flow of the Chisel ecosystem.

#### 3.2.1 ScalaTest

ScalaTest is testing tool for Scala (and Java). ChiselTest is an extension of ScalaTest. Therefore, we first explore a simple ScalaTest example. To use it, include the library in your build.sbt with following line:

Tests are usually found in src/test/scala and the entire test suite can be run with:

```

$ sbt test

```

A minimal test (a testing hello world) to test a Scala Integer addition and a multiplication looks as follows:

```

import org.scalatest._

import org.scalatest.flatspec.AnyFlatSpec

import org.scalatest.matchers.should.Matchers

class ExampleTest extends AnyFlatSpec with Matchers {

"Integers" should "add" in {

val i = 2

val j = 3

i + j should be (5)

}

"Integers" should "multiply" in {

val a = 3

val b = 4

a * b should be (12)

}

}

```

ScalaTest enables simple unit tests that read like an executable specification. The example above contains two tests and the output of the test run will repeat the specification and show that both tests passed:

```

[info] ExampleTest:

[info] Integers

[info] - should add

[info] Integers

[info] - should multiply

```

```

[info] ScalaTest

[info] Run completed in 119 milliseconds.

[info] Total number of tests run: 2

[info] Suites: completed 1, aborted 0

[info] Tests: succeeded 2, failed 0, canceled 0, ignored 0, pending 0

[info] All tests passed.

[info] Passed: Total 2, Failed 0, Errors 0, Passed 2

```

sbt test executes all available tests, which is useful for regression test.<sup>4</sup> However, if you want to run just a single test (suit) you can do this with:

```

$ sbt "testOnly ExampleTest"

```

If you misspell the class name, for example, Exampletest, there will be a relatively silent error message: No tests were executed.

#### 3.2.2 ChiselTest

ChiselTest is the new standard testing tool for Chisel modules based on the ScalaTest tool for Scala and Java, which we can use to run Chisel tests. To use it, include the chiseltest library in your build.sbt with the following line:

```

libraryDependencies += "edu.berkeley.cs" %% "chiseltest" %

"0.5.0"

```

Including ChiselTest this way automatically includes the necessary version of ScalaTest. Therefore, you do not need to include a line for the ScalaTest library. To use ChiselTest, the following packages need to be imported:

```

import chisel3._

import chiseltest._

import org.scalatest.flatspec.AnyFlatSpec

```

Testing a circuit contains (at least) two components: the device under test (often called DUT) and the testing logic, also called a test bench. Tests are started with sbt test. No object with a main function is needed.

The following code shows our simple design under test. It contains two input ports and one output port, all with a 2-bit width. The circuit does a bit-wise AND to its inputs a and b and outputs the result on out:

<sup>&</sup>lt;sup>4</sup>Try sbt test in the repository of this book and you will see more than 70 tests passing.

```

class DeviceUnderTest extends Module {

val io = IO(new Bundle {

val a = Input(UInt(2.W))

val b = Input(UInt(2.W))

val out = Output(UInt(2.W))

})

io.out := io.a & io.b

}