# FPGA Prototyping of Asynchronous Networks-on-Chip

Jon Neerup Lassen

M.Sc. thesis Thesis no.: 26 IMM, DTU Kongens Lyngby 2008

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk

## **Abstract**

Network-on-chip (NoC) is an emerging paradigm for handling the communication in large system-on-chips. This project investigates the ability to prototype asynchronous NoCs on FPGAs.

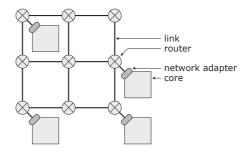

The implementation of asynchronous circuits on standard FPGAs is highly experimental, therefore the first part of the project has been to establish a design flow for the implementation of asynchronous circuits on FPGAs. In the project an asynchronous best-effort NoC for an FPGA has been successfully developed. The NoC implementation consists of a router and network adapters and is implemented using a 4-phase bundled data handshake protocol. Cores connects to the network using an OCP interface. To demonstrate the NoC it has been implemented in a small multi-processor prototype using a mesh topology for the network.

# **Preface**

This thesis has been carried out at the Computer Science and Engineering division of the Informatics and Mathematical Modelling department at the Technical University of Denmark from September 2007 to March 2008.

I would like to thank my supervisor Jens Sparsø for his guidance and support during the project. I would also like to thank Morten Sleth Rasmussen for his help.

Lyngby, March 2008

Jon Neerup Lassen

# **Contents**

| <b>A</b> | Abstract |                                        |    |  |

|----------|----------|----------------------------------------|----|--|

| Preface  |          |                                        |    |  |

| 1        | Intr     | roduction                              | 1  |  |

|          | 1.1      | Project Description                    | 1  |  |

|          | 1.2      | Thesis Overview                        | 2  |  |

| <b>2</b> | Asy      | nchronous Circuits on FPGAs            | 3  |  |

|          | 2.1      | Introduction                           | 3  |  |

|          | 2.2      | Asynchronous Circuit Design            | 4  |  |

|          | 2.3      | Previous Work                          | 8  |  |

|          | 2.4      | FPGA Basics                            | 9  |  |

|          | 2.5      | Asynchronous Design Elements for FPGAs | 12 |  |

|          | 2.6      | Controlling Timing                     | 23 |  |

vi CONTENTS

|   | 2.7                               | Design Flow                              | 33         |  |

|---|-----------------------------------|------------------------------------------|------------|--|

| 3 | Networks-on-Chip                  |                                          |            |  |

|   | 3.1                               | Introduction to Networks-on-Chip         | 41         |  |

|   | 3.2                               | Basic Concepts                           | 42         |  |

|   | 3.3                               | Previous Work                            | 47         |  |

| 4 | Asy                               | nchronous Network-on-Chip Design         | 49         |  |

|   | 4.1                               | General Network Design                   | 49         |  |

|   | 4.2                               | Router Design                            | 56         |  |

|   | 4.3                               | Network Adapter Design                   | 64         |  |

|   | 4.4                               | Traffic Generator Design                 | 73         |  |

| 5 | Asy                               | nchronous Network-on-Chip Implementation | <b>7</b> 5 |  |

|   | 5.1                               | Router                                   | 75         |  |

|   | 5.2                               | Network Adaptor                          | 78         |  |

|   | 5.3                               | Traffic Generator                        | 79         |  |

| 6 | Asynchronous Network-on-Chip Test |                                          |            |  |

|   | 6.1                               | Introduction                             | 81         |  |

|   | 6.2                               | FIFO                                     | 81         |  |

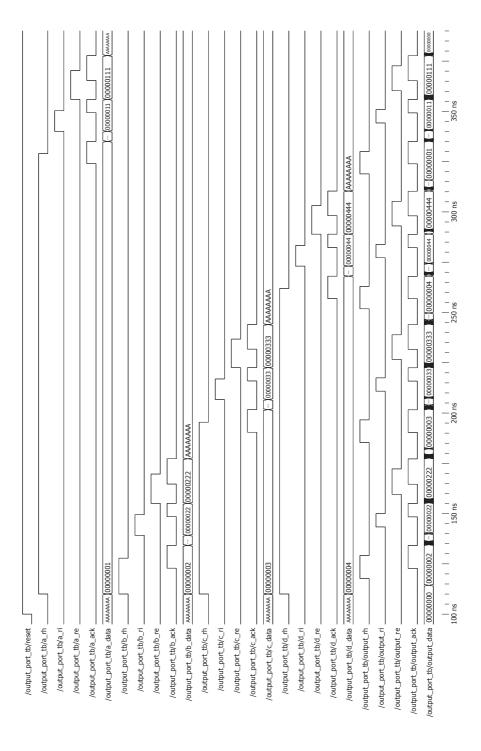

|   | 6.3                               | Input Port                               | 82         |  |

|   | 6.4                               | Output Port                              | 82         |  |

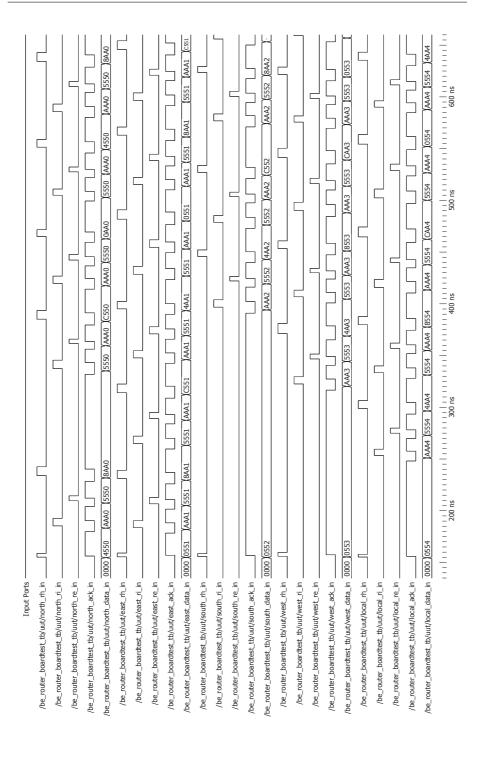

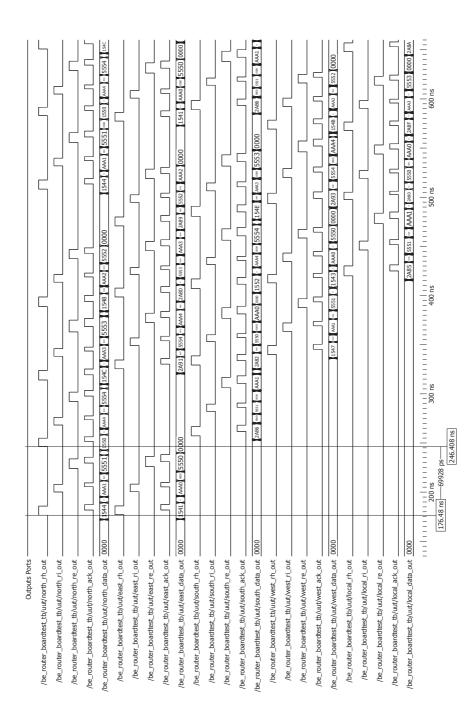

|   | 6.5                               | Router                                   | 83         |  |

| CONTENTS | vii |

|----------|-----|

|          |     |

|              |                                        |                           | $\overline{}$ |  |

|--------------|----------------------------------------|---------------------------|---------------|--|

|              | 6.6                                    | Network Adaptor           | 84            |  |

| 7            | Asynchronous NoC-Based MPSoC Prototype |                           |               |  |

|              | 7.1                                    | Introduction              | 85            |  |

|              | 7.2                                    | Synchronous NoC-Based SoC | 85            |  |

|              | 7.3                                    | MPSoC Overview            | 87            |  |

|              | 7.4                                    | MPSoC Design              | 87            |  |

|              | 7.5                                    | MPSoC Implementation      | 89            |  |

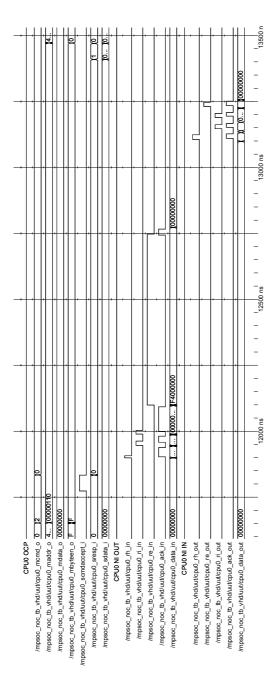

|              | 7.6                                    | MPSoC Test                | 93            |  |

|              |                                        |                           |               |  |

| 8            | Disc                                   | cussion                   | 95            |  |

|              | 8.1                                    | Evaluation                | 95            |  |

|              | 8.2                                    | Future Work               | 98            |  |

| 9            | Con                                    | nclusion                  | 99            |  |

| $\mathbf{A}$ | App                                    | pendices                  | 105           |  |

|              | A.1                                    | Perl SDF script           | 105           |  |

|              | A.2                                    | NoC Tests                 | 107           |  |

|              | A.3                                    | MPSoC Tests               | 120           |  |

|              | A.4                                    | RPM Forum Post            | 124           |  |

|              | A.5                                    | VHDL Code                 | 125           |  |

|              | A.6                                    | C-Code                    | 261           |  |

viii CONTENTS

## Chapter 1

## Introduction

## 1.1 Project Description

The scaling of microchip technologies has made it possible to fabricate large System-on-chip (SoC) designs. Network-on-chip (NoC) is an emerging paradigm for handling the global communication between subsystems in large SoC designs. Due to the scaling of microchip technologies the distribution of a global clock has become increasingly difficult. Designing the NoC using asynchronous design techniques is an appealing approach because it eliminates the need for a global clock. Several examples of asynchronous NoC implementations have been published. All of them are based on CMOS standard cells designs, which makes it complicated and expensive to build prototypes of NoC systems.

The purpose of this project is to investigate how to implement FPGA prototypes of asynchronous NoC systems. This will give researchers the possibility to perform experiments on different asynchronous NoC designs on an FPGA prototype and thereby avoiding to use a custom designed chip which is both expensive and time consuming to build. Because it is targeted at prototyping, reliability of the NoC is not a key concern. The primary goal is to develop a working system so emphasis has not been put on high performance or low cost.

The implementation of asynchronous designs on standard FPGAs targeted syn-

2 Introduction

chronous design is highly experimental. The implementation presented in this thesis is mainly based on the experience collected in a few small projects carried out on IMM, DTU. The asynchronous FPGA design from these projects have been extremely simple; only small circuits that calculates the greatest common divider or generates a list of fibonacci numbers have been implemented. Thus a major part of this thesis is to establish a design flow for implementing large asynchronous systems on FPGAs.

#### 1.1.1 Objectives

The objectives of the thesis are:

- 1. Establish a design flow for implementing asynchronous systems on FPGAs.

- 2. Develop a simple asynchronous best-effort NoC and implement in on an FPGA.

- 3. Develop an FPGA implementation of a multi-processor prototype with the asynchronous NoC used as interconnect.

#### 1.2 Thesis Overview

The structure of the rest of this thesis is as follows:

Chapter 2 is dedicated to present the experiences learned about the implementation of asynchronous circuits on FPGAs. It is meant to present a general design flow for designing asynchronous circuits on FPGAs that is not specifically targeted at NoC design. It also includes an introduction to asynchronous design techniques.

Chapter 3 gives an introduction to NoC design and presents the previous work that have been used for the NoC design.

Chapter 4, 5, and 6 presents the design, implementation, and test of the developed NoC.

Chapter 7 presents a small prototype utilizing the developed NoC.

Finally chapter 8 and 9 contains the discussion and conclusion respectively.

# Asynchronous Circuits on FPGAs

#### 2.1 Introduction

Asynchronous circuit design for FPGAs is not a straight-forward task. FPGAs are solely intended for synchronous designs, thus the design primitives available on the FPGA and the available design tools are only intended for synchronous designs. This chapter will give an explanation of what the challenges in asynchronous FPGA design are and how these challenges are overcome. The chapter is ended with a design flow guideline for implementing asynchronous circuits on FPGAs.

Section 2.2 will give a brief introduction to the fundamental concepts of asynchronous circuit design. Section 2.3 will present previous work about implementing asynchronous circuits on FPGAs. Section 2.4 will describe the FPGA that is used in the project. Section 2.5 will present the implementation of the basic asynchronous design elements. Section 2.6 will describe how timing is controlled when implementing asynchronous circuits. The last section 2.7 will give guidelines for the design flow for the implementation of asynchronous circuits on FPGAs.

### 2.2 Asynchronous Circuit Design

In traditional synchronous designs the flow of data is controlled by a global clock. In asynchronous design the flow of data is controlled locally between neighboring components using a request/acknowledge handshake protocol. The absence of a global clock gives asynchronous circuits some different properties compared to synchronous circuits. Some of the advantages are:

- Low power consumption components are only active when they are actually used.

- high operating speed the operating speed is not limited to the slowest component. The circuits will operate at their natural speeds.

- Low EMC noise the local "clocks" tend to tick at random points in time.

- No clock distribution/skew problems there is no clock!

The following sections will give a brief introduction to the fundamental concepts of asynchronous circuit design. For an in-depth presentation of asynchronous circuit design the reader is referred to [24], which also have been used as the source for the theory presented in the following sections.

#### 2.2.1 Handshake Protocols

The handshaking between neighboring registers is carried out using a handshake protocol. The basic operation of a handshake protocol is: the sender sends a request to the receiver to inform that is has new data for it; when the receiver has captured the data, it acknowledges the request; and the sender is able to take its request down to be ready for another handshake. Two main types of handshaking protocols exists: bundled-data and dual-rail. In bundled-data protocols request and acknowledge uses separate signals, that are bundled with the data signal to form the handshake channel. In a dual-rail protocol the request signal is encoded into the data signals. In this project only the bundled-data protocol is used, thus dual-rail will not be presented here.

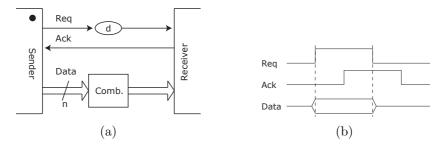

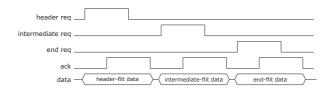

Figure 2.1(b) shows an example of the 4-phase bundled-data protocol. The sender sets the data signals and asserts the request signal. The receiver reads the data and responds by asserting the acknowledge signal. When the receiver sees that the acknowledge signal has been asserted, it pulls down the request signal. The receiver ends the transaction by pulling the acknowledge signal down.

Figure 2.1: The 4-phase bundled data protocol.

Note that the request and acknowledge signal must return to zero before the transaction ends. A more efficient 2-phase bundled-data protocol exists where the superfluous return-to-zero transition is avoided. In the 2-phase protocol a request or acknowledge event is encoded as a signal transition on the control wire, e.g. a  $0 \to 1$  or a  $1 \to 0$  transition, in contrary to the 4-phase bundled-data where a request or acknowledge event is encoded by the level of the respective control wire.

Depending on if it is the receiver or it is the sender who initiates the transaction, handshake channels can be grouped into another two types: push channels and pull channels. In push channels the sender initiates the transaction by sending a request to the receiver. The request signal tells the receiver that the sender has data for it. In pull channels the roles are interchanged, i.e. the receiver initiates the transaction using the request signal, and the request tells the sender that it is ready to receive data. To distinguish between pull and push channels the initiating part is marked with a dot on the diagram as shown on figure 2.1(a).

All bundled data protocols have the timing requirement that the sequence of events at the sender's side is preserved at the receiver's side. For a 4-phase bundled-data push channel this means that the designer *must* assure that the the receiver sees valid data before the request is asserted. If the data signals are delayed, e.g. by propagating through combinatorial logic, the request signal must also be delayed accordingly. This is referred to as *delay matching*. To delay a signal a delay element is used. In figure 2.1(a) a delay element is inserted on the request signal. The inserted delay must at least match the delay through the combinatorial circuit that the data signals propagates through.

The time interval in which data is valid during the handshaking phase is described by the *data validity scheme*. For at 4-phase bundled-data channel four different data validity schemes exists: early, broad, late, and extended early.

- Early data validity: data are valid from the rising request event to the rising acknowledge event.

- Broad data validity: data are valid from the rising request event to the falling acknowledge event.

- Late data validity: data are valid from the falling request event to the falling acknowledge event.

- Extended early data validity: data are valid from the rising request event to the falling request event.

The choice of data validity scheme affects the implementation of the handshaking components.

In synchronous designs signals are only required to carry the correct value during a well defined period around clock-ticks. In between clock-ticks the signals may exhibit hazards or transitions. In asynchronous designs this is not allowed because all signal transitions have a meaning. For example, a hazard on an acknowledge signal will make the sending circuitry believe that the receiver already has captured the data, even though this is not the case. Consequently asynchronous circuits requires that all control signals must be valid and hazard free at all times.

#### 2.2.2 The Muller C-Element

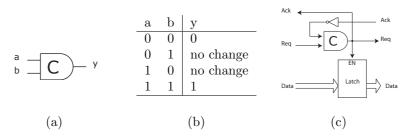

To be able to design hazard free control citcuits a new component is needed: the Muller C-element. The C-element has the property that it indicates both when all inputs are low and when all inputs are high. In comparison a conventional AND gate only indicates when all inputs are high and a conventional OR gate only indicates when all inputs are low.

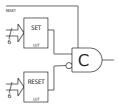

The Muller C-element is a state holding component which is 0 if both inputs are 0 and 1 if both inputs are 1. If the inputs are 01 or 10 the C-element will keep its previous state. Figure 2.2 shows the gate symbol and the truth table for the C-element. The use of the C-element in a handshake component is shown in figure 2.2 (c). This circuit is a single stage of the Muller pipeline, which is the backbone of almost all asynchronous control circuits.

Figure 2.2: The Muller C-element: (a) gate symbol, (b) truth table, and (c) a Muller style handshake latch.

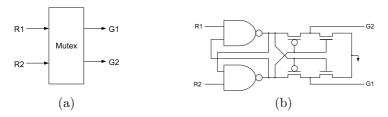

Figure 2.3: Mutex component: (a) symbol, and (b) possible implementation (from [24]).

#### 2.2.3 Mutual Exclusion

Handshake components with more than one input channel usually requires that the input requests are mutual exclusive, i.e. only one request is high at a time. Since the requests may arrive at exactly the same time a mutual exclusion (mutex) component is needed. Figure 2.3 shows the mutex symbol and a possible CMOS transistor level implementation (from [24]). The mutex should exhibit the following behavior: If only one request is asserted the corresponding output should be asserted. If both inputs are asserted but one of them is asserted before the other, the late request should be held back and only allowed to propagate when the other request has been taken down. If both request are asserted at the same time, the mutex must make an arbitrary decision of which signal should be allowed to propagate first. A possible implementation of a mutex component has two cross-coupled NAND-gates, which enables one input to block the other. If two requests arrives simultaneously the cross-coupled NAND-gates will become metastable, hence a metastability filter is needed at the outputs. The shown implementation of the metastability filter is a CMOS transistor level implementation. In section 2.5.2 a metastability filter that can be implemented in an FPGA is presented.

#### 2.3 Previous Work

The previous work about implementing asynchronous circuits on FPGAs is very limited. A number of special courses and course projects (from the course 02204 - Design of Asynchronous Circuits) supervised by Prof. Jens Sparsø have investigated the implementation of basic asynchronous design elements. The 02204course project by Knud Hansen and Guillaume Saoutieff [11] is the first project. A LUT based C-element is implemented together with a fork, a join, a merge, a mux, and a demux component. A simple circuit computing the GCD (greatest common devisor) is implemented on a Xilinx Spartan-II FPGA. All components are based on the 4-phase bundled-data handshake protocol. In a later 02204 course project by Tue Lyster and Morten Thomsen [15] an asynchronous symbol library for the Xilinx schematics editor (Xilinx ECS) based on the components created in [11] is created. In the special course project Asynchronous Circuits in FPGA by Mikkel Stensgaard [26] a number of improvements and additions have been made. The implementation of the components presented in [11] has been improved to better fit the anatomy of an FPGA. The delay element is now implemented as a chain of AND gates. A design flow for implementing Petrify circuits is presented. Un-, semi- and fully-decoupled latch controllers and mux and demux components are specified by STGs and implemented using Petrify. The latch controllers are tested in a FIFO and in a FIFO-ring circuit. Again the GCD circuit is used as test circuit for the other components. All components are added to a VHDL library. The circuits have been implemented on a Xilinx Spartan-IIE FPGA. In the special course Asynchronous Circuits on FPGAs by Morten Rasmussen, Christian Pedersen, and Matthias Stuart [21] the implementation of the components from [26] is changed to fit a new VHDL library. The library is extended with 4-phase dual-rail implementations of the components from [26]. The new library allows for easy switching between the two types of handshake protocols. The following new components are added: adder, subtracter, inverter, shifter, and comparator. Also, the library is documented in a complete library reference. The library utilizes user-defined data types which must be converted by wrappers for successful implementation. In the special course Implementation of Asynchronous Circuits in FPGAs by Esben Hansen and Anders Tranberg-Hansen [10] another complete redesign of the library has been carried out after evaluation of the existing library from [21]. They found that the use of user-defined data-types made it too tedious to implement even simple circuits. New 4-phase bundled data components are added: a register file, a block-ram based memory, a AND-, OR-, NOR-, and a XOR- component, and a simple ALU. The components are tested in a simple Fibonacci circuit on a Spartan-3 FPGA. Also, oscilloscope measurements of the delay element is performed. A user guide for using the library is included along with a complete library reference. In the 02204 course project FPGA Implementation of an Asynchronous Arbiter by Mads Kristensen and Jon Lassen [14] a mutex and an

2.4 FPGA Basics 9

arbiter component is implemented. The mutex is implemented solely in LUTs and it is based on a standard gate mutex design presented by Ran Ginosar [8]. The design of the arbiter is based on the design from [24] and is implemented on a Xilinx Spartan-3 FPGA.

In the Aspida project [13] made by a consortium between FORTH-ICS, Politecnico di Torino, University of Manchester, and IHP Microelectronics a desynchronized implementation of the DLX RISC CPU is presented. The DLX RISC CPU is a 5-stage pipelined CPU similar to the MIPS processor. Desynchronization is a method for converting an existing synchronous design into an asynchronous systems. When de-synchronization is performed all pipeline flip-flops are taken out and replaced by latches and asynchronous control circuits. The asynchronous pipeline latches are implemented so they are guaranteed to provide an equivalent behavior as the clocked flip-flops. This is done without touching the datapath at all. In this way the global clock is completely replaced by handshake signals. Delay elements must be inserted on the request path to match the delay of the combinatorial blocks between the asynchronous pipeline latches. The processor has been implemented on a Xilinx Spartan-2E FPGA and on a chip.

Details from the set of previous work presented here, which are interesting for this project, is presented in the relevant sections in the report.

#### 2.4 FPGA Basics

This section will give a short introduction to the Xilinx FPGA used in the project and the development tools provided by Xilinx.

For the project the XC5VSX50T Xilinx Virtex-5 FPGA is used. The Virtex-5 is the newest FPGA generation supplied by Xilinx. The description of the FPGA is focused on how the logic resources are organized, because it is the most interesting from an asynchronous design point of view.

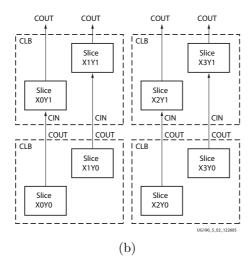

The FPGA consists of a large array of Configurable Logic Blocks (CLBs). Each CLB is connected to a switch matrix which handles the routing between the CLBs. A CLB contains two slices placed in separate columns. The slices does not have any direct connection between them, but each slice has a carry-chain which connects slices in the same column. Figure 2.4 shows the row and column relationship between CLBs and slices and the slice numbering scheme. The slice numbering is important for RPM creation, which is described in section 2.6.3.

Figure 2.4: Arrangement of CLBs and slices, from [35].

Each slice contains four Look-Up Tables (LUTs), four storage elements, multiplexers and carry-logic. The LUTs are used as logic functions generators and have 6 inputs and two outputs. The extra output allows the LUT to perform two different logic functions, if the functions have common inputs. The storage elements can be configured to behave either as a latch or as a flip-flop. In the asynchronous design components presented later in this chapter, the LUTs are also used as state-holding elements by feedback-coupling the output.

The FPGA has a total of 32640 LUTs and the same number of flip-flops/latches. Earlier generations of Xilinx FPGAs only had 4-input LUTs, thus with 6-input LUTs more logic can be packed into fewer LUTs.

The ISE software package is the logic design environment provided by Xilinx. Below is a description of the most important ISE tools which have been used during the project:

**Project Navigator** is the primary user interface for ISE. Most other tools can be accessed from here.

**XST** is the Xilinx synthesizer. Performs the logic synthesization of the VHDL to Xilinx specific netlist files.

MAP performs the mapping from the synthesized netlist to FPGA primitives.

**PAR** performs place and route of the mapped design.

2.4 FPGA Basics 11

Floorplanner used to perform floorplanning tasks. It can be used before MAP and after PAR. Before MAP it is used to assign constraints to the design. After PAR it can be used to manually make changes to the floorplan. It can also be used in an iterative process of re-assigning constraints and rerunning MAP and PAR.

**FPGA Editor** can be used to manually fine-tune the design after PAR. It can also be used as a detailed viewer of the place and routed design.

Design constraints are used to constrain the final implementation produced by the tools, e.g. tell the tools to place two logic functions in the same slice. Constraints can be added in two ways: Directly in HDL or in the User Constraints File (UCF). Constraints added in the UCF file is not read until after synthesis. Not all constraints can be added in HDL. The Xilinx Constraints Guide [29] documents all the available constraints.

Simulations of the design can be performed on four different levels of abstractions:

- **Behavioral** simulation is an RTL level simulation of the design. It is used to validate correct functionality of the design. No timing information is included, so all signals changes instantaneously.

- **Post-Translate** simulation is a gate-level functional simulation of the synthesized design. Is used to verify that the design has been synthesized correctly. Still no timing information is included.

- **Post-MAP** simulation is run after MAP and provides partial timing information. The simulation includes gate delays but no routing delays. It is primary used as a debug step if Post-PAR simulation fails.

- **Post-PAR** simulation provides full timing information. It simulates the design after place and route and contains both gate and routing delay.

For the Behavioral simulation FPGA primitives is simulated using a library called UNISIM while after synthesis the SIMPRIM library is used. The SIMPRIM library uses a more detailed model of the primitives. For asynchronous design the primary simulation modes used is the Behavioral and Post-PAR.

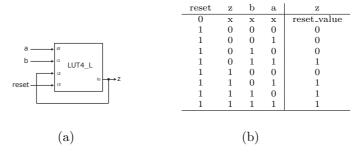

Figure 2.5: C-element LUT implementation and truth table

### 2.5 Asynchronous Design Elements for FPGAs

Section 2.2 presented the fundamental concepts of asynchronous circuit, where a number of asynchronous design elements was presented. This section will present FPGA implementations of these basic building blocks along with a synchronizer component.

#### 2.5.1 C-Element

The C-element is a simple state holding device much similar to a set-reset latch. The truth table was shown in figure 2.2 (p. 7). The implementation presented here is from the asynchronous circuit FPGA design library presented in [10] and it has not been changed for the use in this project.

The C-element can be implemented in a single LUT primitive with the output looped back to one of the inputs. This is shown in figure 2.5. A *generic* value is used to define the desired reset value for proper initialization. The instantiated LUT is a lut4\_l primitive which is a LUT with local output. This instructs the tool to use local routing for the feedback signal.

In figure 2.6 an example of a VHDL instantiation of a C-element is shown. The truth table values from figure 2.5(b) is used as the initialization value. The implementation of the C-element is found in appendix A.5.1.2 (p. 127).

Figure 2.6: VHDL instantiation of a C-element, from [10]

#### 2.5.2 Mutex

The mutex component was introduced in section 2.2.3 and figure 2.3 (p. 7) showed a possible implementation of mutex. As shown on the figure a metastability filter is needed on the output to prevent the circuit from propagating possible undefined values, resulting from a metastable state at the cross-coupled NAND gates. An FPGA implementation of a mutex component is presented in [14] with satisfactorily results. This implementation has been used for this project. The VHDL code for the mutex implementation is found in appendix A.5.1.3 (p. 128).

The following will be presented in this section:

- The implementation of the mutex from [14].

- Some small modifications to the implementation to optimize it for a Virtex-5 FPGA.

- A solution to post place and route simulation problems of the mutex that has not been covered in [14].

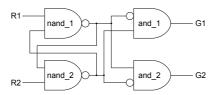

An FPGA implementation of the mutex can (of course) only use the primitives available on the FPGA. The metastability filter in figure 2.3 is a CMOS transistor level implementation, thus it cannot be implemented in an FPGA. In [8] Ran Ginosar presents a mutex component build only from standard gates. The standard gate mutex design is shown in figure 2.7. The design still uses two cross-coupled NAND gates to let one input block the other. The metastability filter is implemented by two AND gates with one inverted input. Each of the four gates can be implemented in one LUT primitive.

The circuit cannot be considered as a safe design; if the NAND gates gets into metastability, they will stay there for an unknown length of time, but will

Figure 2.7: A mutex component build from standard gates

eventually choose one side randomly. While the NAND gates are in a metastable state, the AND gates will have unspecified behavior, because their inputs are undefined. However, If the NAND gates stabilizes "fast enough", the AND gates will not "see" the metastability for a long enough period to propagate the undefined inputs. To assure that the NAND gates stabilizes as fast as possible, they should be placed in the same slice to minimize the routing delay.

Another reason to place the NAND gates in the same slice, is to optimize the fairness of the mutex. The fairness is very dependant on the wire delays between the gates. If the wire delay of the cross-coupling signal from NAND\_1 to NAND\_2 is larger than the wire delay from NAND\_2 to NAND\_1 the R2 will get higher priority than R1, since the NAND\_1 gate will be blocked faster. To make the implemented mutex as fair as possible the wire delays between the two nand-gates should be kept as equal as possible.

The mutex presented in [14] is implemented on an older FPGA generation with only two LUTs in each slice, so the mutex occupies two slices. Therefore the implementation has been changed slightly to fit the mutex in a single slice. Everything else is unchanged.

In the implementation of the mutex the four gates are placed in the same slice using rloc constraints (further explained in section 2.6.3). This will keep the wire delays between the gates as equal as possible. However it is not possible to specify the exact placement within the slice, hence some variations in the wire delays may occur. In an actual example from a post place and route simulation, the wire delay from NAND\_1 to NAND\_2 is 186 ps while the wire delay from NAND\_1 is only 130 ps. In this example the R2 signal will have priority, however the priority may be different when implemented on a FPGA since the relation between the delays may be different for an actual circuit. The small delay difference internal in the mutex component will most likely be insignificant compared to the difference in wire delay experienced by the input signals.

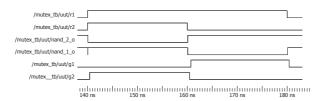

Figure 2.8: Printout from Modelsim showing an oscillating mutex.

The mutex has not been analyzed for Mean-Time-Between-Failure (MTBF). The theory for determining the MTBF of the mutex is the same as for the synchronizer which will be presented in section 2.5.4. In fact a synchronizer is a special case of a mutex, where the clock is connected to one of the inputs [20]. Since this project is aiming at system prototyping and not at in-production systems, the standard gate mutex is used without any further analysis or testing for MTBF and fairness.

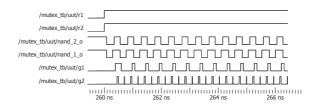

There exists some issues with simulation of the mutex after place and route that has not been covered in [14]. In an actual circuit the NAND gates will not stay in a metastable state forever. This situation is different when it comes to simulation. During simulation the metastable state will result in an infinite oscillation between 0 and 1. In a behavioral (RTL) simulation the simulation will stop due to the oscillation. This happens because the simulation cannot proceed to the next delta-time and an *iteration limit reached* error is issued. During a post place and route simulation the oscillation will propagate to the outputs with a period matching the wire- and gate-delays. Figure 2.8 shows this situation. The period of oscillation is 476 ps for all oscillating signals which matches with the wire and gate delays of the simulation model.

In the case of a behavioral simulation the problem is easily solved by using a higher-level (non-synthesizable) simulation model of the mutex. This solution is used in [14].

In the case of a post place and route simulation the solution is not so easily solved. If the design hierarchy is kept all the way from synthesis to place and route it will also be possible to insert a strictly behavioral simulation model of the mutex into the post place and route simulation model. But if the design is flattened during synthesis it will be very tedious to insert another simulation model. Also, the timing behavior of the mutex will be lost. Therefore another

Figure 2.9: NAND stages of an unfair mutex. (a) shows the desired NAND stage. (b) shows the possible FPGA implementation of the circuit.

solution is needed. Two other solutions have been considered:

- Implementation of an unfair mutex.

- Make the implemented mutex unfair, by changing the simulation model.

Both solutions tries to break the oscillation by making the gate delay of one of the NAND gates larger than the other. By only changing the simulation model some inconsistency will be introduced between the actual circuit and the simulated circuit. If the changes made have minimal influence on the timing behavior of the mutex this inconsistency can be neglected.

The delay model used in the SIMPRIM simulation library effects how the mutex simulation problem can be solved. In VHDL delays can be modeled in two ways: as transport delays and as inertial delays. A transport delay models an ideal device with infinite frequency responses, where any input pulse will produce an output pulse. An inertial delay models devices with finite frequency responses, where an input pulse must have a minimum length before an output pulse is produced, otherwise it will be rejected. By studying the source code of the SIMPRIM simulation library it can be seen that the delay model for wire and gate delays are specified in a library called VITAL (VHDL Initiative Towards ASIC Libraries) which models the delays as transport delays. A simple solution could be to change the delay model used in the library to inertial delays. This will however affect the simulation of all components in the design, which is not desirable.

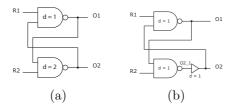

The first solution considered is the implementation of an unfair mutex. An unfair mutex should have unequal gate delays of the NAND gates. This will give the fast gate priority over the slow gate. In figure 2.9(a) this situation is illustrated with gate delays of 1 and 2 respectively. The LUT primitives in an FPGA all have the same timing characteristics, therefore it is only possible to imitate a slow gate as a concatenation of two gates, as shown in figure 2.9(b).

```

(CELL (CELLTYPE "X_LUT6")

(CELL (CELLTYPE "X_LUT6")

(INSTANCE nand_1)

(INSTANCE nand_1)

(DELAY

(DELAY

(ABSOLUTE

(ABSOLUTE

(PORT ADR3 ( 914 )( 914 ))

(PORT ADR3 ( 914 )( 914 ))

(PORT ADR4 ( 130 )( 130 ))

(PORT ADR4 ( 0 )( 0 ))

(PORT ADR5 ( 1013 )( 1013 ))

(PORT ADR5 ( 1013 )( 1013 ))

(IOPATH ADR3 0 ( 80 )( 80 ))

(IOPATH ADR3 O ( 80 )( 80 ))

(IOPATH ADR4 0 ( 80 )( 80 ))

(IOPATH ADR4 0 ( 0 )( 0 ))

(IOPATH ADR5 0 ( 80 )( 80 ))

(IOPATH ADR5 0 ( 80 )( 80 ))

)

)

(b)

(a)

```

Figure 2.10: Delay specification of a 2-input NAND gate with reset from the simulation SDF file. (a) original and (b) is modified to decrease the delay for the ADR4 port.

Due to the transport delay model used in the SIMPRIM simulation library the circuit in figure 2.9(b) will still oscillate, because all pulses on the O2\_1 signal will propagate to the the O2 signal. Consequently it is not possible to solve the simulation problem by implementing a simple unfair mutex.

The chosen solution to solve the oscillation problem is to alter the post place and route simulation model. The post place and route simulation model consists of two files: an VHDL netlist file and an SDF file. The VHDL netlist instantiates simulation models of the FPGA primitives from the Xilinx SIMPRIM library. The SDF file specifies all wire and gate delays used in the simulation. The format of the SDF file is specified using the  $Standard\ Delay\ Format\ Specification\ [18]$ . In figure 2.10(a) an example of a delay specification for a NAND gate with a reset input is shown. Wire delays are modeled as delays at the input ports and is specified as PORT delays. Gate delays are specified as IOPATH delays. Both wire and gate delays can be specified individually for each input. A delay is specified as the rising and falling delay for the particular input and the unit is ps.

To solve the oscillation problem one of the NAND gates should be made faster than the other by decreasing the PORT and/or the IOPATH delays in the SDF file. It is only necessary to decrease the delay of the specific input connected to the other NAND gate; the other inputs can be leaved untouched. This will make the propagation delay through entire mutex element unaffected by the delay change. How much should the delay be decreased to kill the oscillation? Because the transport delay model is used in the simulation model the combined wire and gate delay through the gate must be 0 before the oscillation is killed. In figure 2.10(b) the modified SDF delay specification is shown. Figure 2.11 shows a simulation of the mutex after modification of the SDF file.

Figure 2.11: Simulation of the mutex after modification of the SDF file.

A Perl script that modifies all instances of NAND pairs in an SDF file as described above has been written and can be found in appendix A.1 (p. 105).

#### 2.5.3 Delay Elements

In asynchronous circuit design the ability to delay a signal in a precise and predictable manner is crucial. When performing delay matching of an asynchronous circuit a delay element is inserted in the request path to delay the request signal by an equal amount of time compared to the delay experienced by the data signal, or to put in another way: the *minimum* delay of the delay element should at least match the *maximum* delay experienced by the data signals. When designing traditional synchronous circuits the maximum allowed clock frequency of a design is solely determined by the *maximum* delay through the combinatorial circuit, i.e. synchronous designs are inherently insensitive to the minimum delay of a combinatorial circuit.

In the datasheet for the Virtex-5 FPGA [34] the maximum delay through a LUT is specified to be between  $0.08ns - 0.10ns^{-1}$ , but the minimum delay is unspecified. The only guarantee about minimum delays given by Xilinx is that hold times are never violated. In general minimum delays in CMOS designs are usually not very well defined, since there can be large variations with e.g. change of temperature, supply voltage, etc. In an answer to a question posted in a newsgroup (dated 1996) [1] an Xilinx employee estimates that the minimum delay through a LUT approximately will be 25% of the specified maximum delay. It has not been possible to find any official estimates from Xilinx. This ratio between minimum and maximum delays are given for variations in supply voltage, temperature, and processing, so the delay difference between two LUTs on the same chip, under the same operating conditions, must be expected to be much lower. In this project no incidents have been encountered where a design have failed due to the aforementioned delay variations. The problems may be more prominent if the designs are tested on more different FPGAs and under varying operating conditions.

<sup>&</sup>lt;sup>1</sup>Varies with the speedgrade of the FPGA

Figure 2.12: Asymmetric delay element.

A circuit using the 4-phase bundled data handshake protocol can be designed such that, it is only necessary to insert delays on the rising edge of the request signal. Delays on the falling edge will only slow down the circuit. An asymmetric delay element with this property is shown in figure 2.12. A transition from high to low will have to propagate through the entire chain of AND gates, while a low to high transition only have to propagate through the last AND gate. The signal will be delayed by the combined amount of gate and routing delay in the LUT chain.

In the rest of this section the following points will be presented:

- The implementation of the delay element presented in one of the special course projects [10].

- The implementation of the delay element used in Aspida [13]

- The implementation of the delay element used in this project.

In [10] an FPGA implementation of an asymmetric delay element is presented. The implementation instantiates a chain of LUT-instantiated AND gates connected as in figure 2.12. The number of AND-gates in the delay element is parameterized. To avoid that the synthesizer optimizes the LUT-chain away the keep constraint is applied to the signals connecting the gates. The keep constraint is a synthesis and mapping constraint that tells the synthesizer and mapper not to merge the two components connected by the signal into one component, thus keeping the signal in the design.

The design of the delay element used in Aspida project [13] is a little different than the one presented in [10]. It consists of two parts: a symmetric part and an asymmetric part. The symmetric part is used to generate a pulse delay and consists of a chain of a even number of inverters. The pulse delay is used to control the pulse width of the latch control signal. The asymmetric part is used to generate a matched delay and consists of a chain of AND gates similar to the one in figure 2.12. They also use the keep constraint to avoid that the synthesizer optimizes the delay element away. In the delay element used in the Aspida project [13] they experience a "keep conflict" error when the keep constraint is assigned to two signals which in fact are the same signal. This happens

with the first AND gate in the LUT-chain. They solved this issue by inserting two inverters in front of the first AND gate. To improve the predictability of the delay element, they manually restrict the physical placement of each delay element to a specific area of the FPGA by applying a constraint called area\_group using the Floorplanner tool. By constraining the placement of the delay elements they experience improved predictability without using extensive floorplanning. They also observe increased predictability when the available area is small and decreased predictability when the available area is increased. The other option they have tried is to manually assign each LUT in the delay element to physical slice placement using the loc constraint. They claim that when the loc constraint is used, the predictability of the delay is nearly 100%. However, it turned out that the use of loc constraints had a very negative impact on the optimization of the datapath, especially when the utilization of the FPGA resources was high. Their conclusion is that the use of the area\_group constraint gives almost the same predictability, as when loc constraints are used, and it requires less floorplanning and it does not have the optimization issues of the datapath experienced with the loc constraint.

The implementation of the asymmetric delay elements used in this project is a modified version of the asymmetric delay element presented in [10]. The implementation is modified by constraining the placement of the LUTs in the delay-chain to improve predictability. Constraining the placement will minimize variations in the routing delay, and thereby improve the predictability. The VHDL code for the delay element is found in appendix A.5.1.1 (p. 125).

A different approach is used for constraining the placement of the delay elements, than the one used in Aspida. Instead of constraining the delay LUTs to a physical area of the FPGA, only the relational placement between the LUTs in the delay element are constrained. This allows the tool to place the complete delay element anywhere on the FPGA area, while maintaining the internal placement of the LUTs in the delay element. This is done by assigning rloc constraints to the LUTs. A component constrained using rloc is referred to as an relationally placed macro (RPM) in the Xilinx documentation. The use of RPMs is explained in more detail in section 2.6.3

The layout of the delay LUTs is shown in figure 2.13. The delay LUTs are placed such that the signal between two consecutive LUTs in the LUT-chain will have to be routed to the neighboring CLB in the vertical direction. The main reason for creating the delay element as an RPM is to improve the predictability, however placing the delay LUTs such that longer routing path is required will improve the performance of the delay element, i.e. increasing the delay without using additional LUT resources. Only a limited experimentation of different placement layouts have been tried. If the layout in figure 2.13 is changed, such that the routing is done in the horizontal direction instead of in the vertical direction, the

Figure 2.13: Arrangement of delay LUTs.

tool will issue an error, that the routing resources between the CLBs have been exhausted. Hence, a more optimal placement may exist, but if the utilization of routing resources is near saturation the performance of neighboring logic may be affected.

The issues with keep conflicts experienced in Aspida have not been experienced in this project. The version of the XST synthesizer that is used in this project automatically solves keep conflicts. However, it has been observed that the synthesizer will optimize the first AND gate into a simple buffer LUT. This optimization does not change the intended function of the LUT-chain since the signal still have to propagate through the LUT.

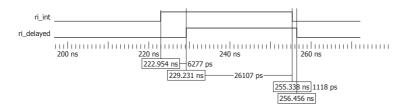

Figure 2.14: Modelsim print of a delay element simulation of size 10 showing the  $0 \to 1$  and  $1 \to 0$  delay.

Figure 2.14 shows a print of a Modelsim simulation of a delay element with a size of 10. The asymmetric properties are clearly shown with a low  $\rightarrow$  high delay of 6.3 ns and a high  $\rightarrow$  low delay of 1.1 ns. In section 2.6.1 a number of experiments of the size and predictability of the delay element in different contexts are presented.

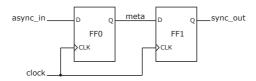

#### 2.5.4 Synchronizer

When a synchronous system communicates with the outside world it must use a synchronizer circuit. All inputs to the system that does not come from the same clock domain must be passed through a synchronizer to assure proper synchronization with the local clock-domain. The synchronizer will assure that the input signal satisfies the setup and hold time requirements of the local clock-domain. The problem with synchronization is well-known and described in many text-books on digital design, e.g. in [27]. In a GALS (Globally Asynchronous Locally Synchronous) design with several local clocked synchronous circuits connected by an asynchronous interconnect, such as the system presented in chapter 7, a synchronizer is needed on the signals coming in from the interconnect. The most common synchronizer design is to let the asynchronous signal pass through a series of flip-flops clocked with the clock of the synchronous system. This is also the method applied in this project. Figure 2.15 shows a synchronizer design with two flip-flops.

A synchronizer will always suffer from metastability problems. If the asynchronous input changes during the decision window of the flip-flop the output of the flip-flop may become metastable and stay in the metastable state for an arbitrary period of time. By having more concatenated flip-flops in the synchronizer the probability that the output of the synchronizer becomes metastable can be reduced, however it can never be removed completely. In the Xilinx Application Note Metastable Recovery in Virtex-II Pro FPGAs [2] the MTBF of

Figure 2.15: Synchronizer design with two concatenated flip-flops.

a synchronizer flip-flop is measured for a Virtex-II Pro FPGA. The conclusion is that if a two flip-flop synchronizer is used the metastable delay can safely be ignored for speeds below 200 MHz. It also states that for this conclusion to hold, the routing delay between the two flip-flops should be minimized. The MTBF is a statistically defined value and is calculated by the following formula:

$$MTBF = \frac{e^{K2 \cdot \tau}}{F1 \cdot F2 \cdot K1}$$

where F1 is the frequency of the clock input of the flip-flops, F2 is the frequency with which the asynchronous input changes, K1 is a device dependent constant describing the likelihood of going into metastability, K2 is the time interval available for resolving the metastability, and  $\tau$  is a device dependent time constant. Note that the formula assumes that the changes of the asynchronous input is uniformly distributed over the clock period. The formula is equivalent to the one presented in [27]. It has not been possible to find information targeting the Virtex-5 FPGA, but it is expected that due to the newer process used the MTBF is further improved.

In the implementation of the synchronizer the two flip-flops should be placed in the same slice component using the rloc constraint to minimize the routing delay between them. Details on the use of rloc is found in section 2.6.3. The implementation is found in appendix A.5.1.4 (p. 131).

## 2.6 Controlling Timing

Controlling timing is vital for any digital design. In asynchronous designs the delay matching process is highly dependent of the ability to control path delays in the design.

In section 2.6.1 the predictability of the delay elements is investigated through a series of simulation experiments. In the Xilinx design flow the preferred way to control timing is by assigning timing constraints to the design. The ability to use these timing constraints on asynchronous designs are explained in section

2.6.2. Another method which can ease the delay matching process is the ability to create design macros with repeatable timing metrics. This method is called relationally placed macros. Some problems have been encountered for creating relationally placed macros of asynchronous components. Section 2.6.3 explains this.

#### 2.6.1 Delay Element Experiments

The delay element presented in section 2.5.3 does not give fixed delay lengths for a given size. Even though the delay through a LUT is fixed for all LUTs on the FPGA, variations in the wire routing will lead to variations in the delay produced by the delay element. In this section a number of experiments based on post place and route simulations of the delay element will be presented.

The purpose of the experiments is to document a number points:

- How large is the delay of a delay element of a given size.

- How predictable is the delay of a delay element, i.e. how large are the fluctuations of the produced delay of delay elements with equal sizes.

- How the use of placement constraints affects the predictability.

- If changing the size of a delay element will affect the timing of the datapath, such that the delay to be matched will change.

To investigate if the context in which a delay element is used affects the predictability, the delay element simulations are performed in two scenarios:

- Delay elements alone.

- Delay elements instantiated in a larger design.

By simulating the delay elements in a larger design the fluctuations of the delay of the datapath can be measured.

For the simulations where the delay elements is instantiated in a larger design, the measurements are performed on the delay elements in a FIFO stage of the NoC router presented in section 4.2. The FIFO stage is connected to an input port of the router and the depth of the FIFO is one. No IO buffers are inserted when the design is implemented. A simulation module is used to send data

into the FIFO. Only measurements on the rising edge of the request signals are performed.

After the delay simulations was performed an error was discovered in the design of the FIFO stage.<sup>2</sup> Therefore, the FIFO stage presented in section 4.2 differs from the one used for the delay simulations. This does not affect the conclusions about the delay simulations, since the delay observations are general for any circuit.

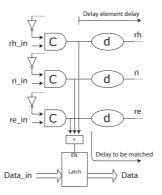

The FIFO stage includes three delay elements; one for each of the three request signals. Figure 2.16 shows the section of the FIFO stage used in the simulations.

In the rest of this section the following results will be presented:

- The ratio between gate delays and wire delays in the delay element.

- Comparison of the delay produced by a placement constrained delay element and an unconstrained delay element when simulated alone.

- The same comparison but with the delay elements instantiated in a NoC router.

- Correlation between the size of the delay elements and the delay to be matched in the datapath. Changing the size of a delay element affects the overall placement of the design, resulting in variations in the delay to be matched.

When the delay element is simulated alone, there is no wire delay on the input signal, because it is the only component in the design. For the simulations of the FIFO stage the delays are measured from the output of the C-elements to the output of the delay element, i.e. the wire delay between the C-element and the delay element is included in the measurement. The delay which the delay element must match are measured from the output of the C-element to when data is stable on the output of the latch. In the simulations the size of the delay elements are varied from 2 to 30 LUTs. Since each FIFO stage includes three delay elements, three independent measurements can be made from each simulation. Both post map and post place and route simulations are presented. Because a post map simulation does not include wire delays, the post map delay will be the same for all equal sized delay elements.

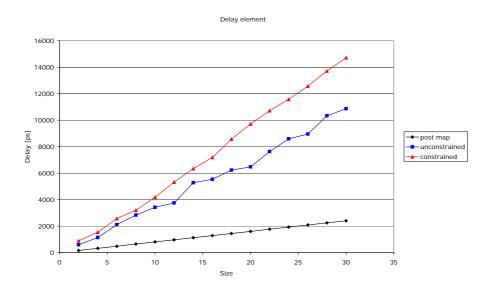

The simulation results with delay elements alone are shown in figure 2.17. The constrained graph is for the delay element where the LUT placement has been

$<sup>^2\</sup>mathrm{The}$  latch was wrongly set to be opaque when EN = 0. The latch should be opaque when EN = 1.

Figure 2.16: Section of the FIFO stage used in the simulations.

constrained as shown in figure 2.13 on page 21. The *unconstrained* graph is a delay element where rloc constraints have not been applied. The post map graph is completely linear and satisfies the equation

$$delay = 80 \cdot size$$

which agrees with a LUT delay of 80 ps, as specified in the data sheet. Using linear regression to approximate an equation for the post place and route delays in figure 2.17 (forced through (0,0)) gives

$$delay_{unconstrained} = 352 \cdot size$$

$$delay_{constrained} = 478 \cdot size$$

The gate delay only constitutes from 18% to 23% of the total delay giving approximately a 1:5 ratio between gate and wire delays. In the Xilinx Constraints Guide [29] it is stated that the routing delay typically accounts for 45% to 65% of the total path delay for a combinatorial circuit. So the contribution of the routing delay is larger than expected. Constraining the placement of the delay LUTs results in an average increase in the resulting delay of approximately 35% The predictability of the unconstrained delay element is quite good, with only small fluctuations in the delay. The constrained delay element is even better with almost no fluctuations. The small fluctuations for the constrained delay element can be explained by the fact, that even if the LUTs in the delay element are constrained to a specific slice, the internal placement within the slice can still vary, and also the chosen routing between slices can deviate from one another. The conclusion of the simulations of the delay elements alone is that the predictability is improved for the placement constrained delay elements compared with the unconstrained delay elements but the unconstrained delay elements still produces fairly predictable delays. The constrained delay elements

Figure 2.17: Simulations of a single delay element, with and without placement constraints.

produces larger delays for the same size, due to the longer routing caused by the placement.

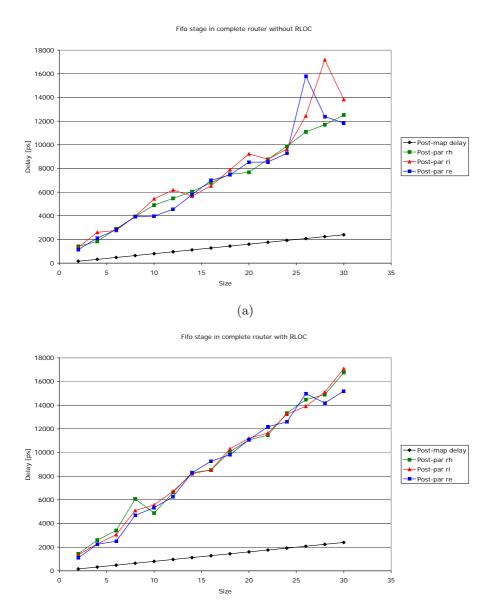

Figure 2.18 shows the simulation results for the delay elements in the FIFO stage. A stage has 3 request signals: rh, ri, and re. Figure 2.18(a) shows the simulations with the unconstrained delay element and figure 2.18(b) shows the simulations for the constrained delay element. Comparing the unconstrained delay element when it is inserted in a larger design and when it is simulated alone shows comparable predictability for small sizes. For larger sizes significant delay fluctuations are observed. An increase in the size of 2 results in a single case in an additional delay of more than 6 ns. For the constrained delay element the produced delays are free from such large fluctuations. Both the unconstrained and the constrained delay element produces larger delays when inserted in a larger design compared with the single case. The reason for this is the extra wire delay from the output of the C-element to he input to the delay element. Variations of this wire delay can also explain the decreased predictability of the constrained delay element. Constraining the placement of the delay elements increases the predictability of the delay when the delay element is used in a larger design. It is expected that the fluctuations of the unconstrained delay element will be even more noticeable for larger designs with a higher LUT utilization ratio.

Figure 2.18: Delay simulations of a FIFO stage. (a) Using unconstrained delay elements. (b) Using constrained delay elements. (a)

(b)

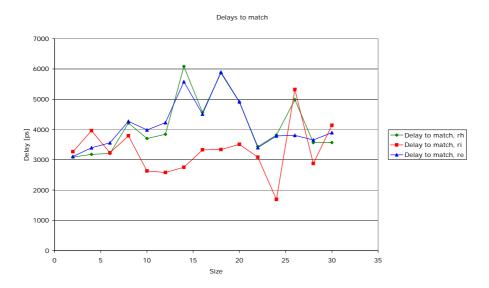

Figure 2.19: Delays in the datapath to be matched.

When performing delay matching of a circuit, changing the size of a delay element will affect the delay that the delay element should match. In fact, even a small change in the design will affect where logic is placed thus altering the routing and thereby changing the timing parameters. To investigate how significant this effect is the size of the delay element versus the delay to be matched in the datapath has been measured. For the simulations the same setup as in figure 2.16 has been used with a complete router design. The measurements are shown in figure 2.19. The x-axis is the size of the delay elements and the y-axis is the time interval from when the request signal is asserted to the output of the latch is stable. The graphs show fluctuations in the delay to be matched of more than 3 ns. This indicates that extra overhead is needed when a circuit is delay matched to account for delay fluctuations in the datapath.

# 2.6.2 Timing Constraints

In the Xilinx design flow the preferred way to control timing is by assigning timing constraints to the design. This section will describe the timing constraints that are available to control the timing of a design.

The guidelines for assigning timing constraints provided by Xilinx are found in

the Xilinx Constraints Guide [29]. Two groups of timing constraints exists:

Global timing constraints affects all paths in the clock domain. Global timing constraints are used to specify global constraints for clock signals, input/output pads, and combinatorial pin-to-pin paths. They are most commonly used on clock signals.

Specific timing constraints are assigned to a specific path in the design. A specific timing constraint can either be a static path constraint or a multicycle path constraint. A multi-cycle path constraint is used when the timing of the path between two registers must be constrained to a multiple of the register clock. A static constraint is assigned to a pad-to-pad path without registers.

All timing constraints are assigned in the UCF file and is applied after synthesis.

To constrain a clock net it must be assigned a name using the tnm\_net constraint and the desired clock period are assigned to the clock net using the timespec period constraint. The design tool will try to optimize the datapath to meet the timing constraint applied to the clock net. If there is not specified any global clock constraints the design tool will identify possible internal clock signals in the design and perform optimizations according to these local clocks. This is referred to as Performance Evaluation mode by Xilinx. Performance Evaluation mode is only used when Timing Driven Packing and Placement is enabled in the mapper. Timing Driven Packing and Placement is one of the phases of the Xilinx mapping process. For older platforms, than the Virtex-5, timing driven packing and placement was optional, but for the the Virtex-5 it is a required step of the mapping process [32]. In an asynchronous-only design there will typically not be any global clock constraints. Therefore the designer should be aware of the optimizations performed when Performance Evaluation mode is active.

The static path constraints are the only constraints that are not related to a clock, therefore they are the only timing constraints applicable to asynchronous components. When assigning a static path constraint the pad-to-pad delay must be constraint to an absolute time period, e.g. 10 ns. Because timing constraints are assigned to the design after synthesis, the process of assigning constraints to all instances of a component can be cumbersome since all the pin-names must be identified in the post-synthesis net-list.

Static path constraints could be used in the delay matching process. The combinatorial delay experienced by the data signals could be constrained to a reasonable time period. The delay element should then be dimensioned according

to the constrained delay. The problem with this approach is to determine how large the constrained delay should be. It will be hard to avoid a large overhead of the constraint delay, and as a result wasting area and degrading performance due to oversized delay elements. To avoid over-constraining the delay a cumbersome iterative process of design implementation, delay constraining, reimplementation, and delay re-constraining must be applied. This must be done individually for all constrained paths in the design. Nonetheless they use this approach in Aspida [13]. This is manageable because the Aspida design only contains five delay elements and a well-defined datapath with a priori knowledge of the combinatorial delay from the synchronous implementation. In the MPSoC system presented in chapter 7 the number of delay elements exceeds 200. Therefore this approach has been abandoned.

The overall conclusion is that the available timing constraints are not very well suited to control the timing of large asynchronous systems. Due to the manual process of assigning the timing constraints the process becomes too cumbersome, unless the number of constrained paths in the design is very small.

### 2.6.3 Relationally Placed Macros

For timing critical designs Xilinx provides a method for locking the internal placement of a subcomponent of a design. This method allows the designer to create a relationally placed macro (RPM) that can be instantiated in another design with repeatable performance and timing properties. An RPM is a collection of FPGA primitives grouped together in a set in which the placement of each primitive is relationally constraint. This allows the placer to move the macro freely around on the chip area without touching the internal placement.

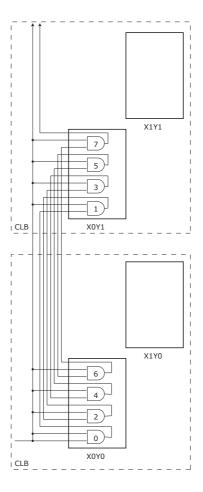

The relational placement of the primitives is defined using the placement constraint rloc. rloc is used to assign a primitive to a slice using slice coordinates, e.g. "X0Y0". The slice coordinates was described in section 2.4 (p. 9). If another primitive is assigned to the slice "X1Y0", the two primitives will always be placed in slices next to each other column wise, however nothing is specified about their absolute placement. A guide describing how to create an RPM manually is found in an article from the TechXclusive Xilinx magazine [9] and details about the rloc constraint is found in the Xilinx Constraints Guide [29].

RPMs can be created using two different approaches:

- By manually assign rloc constraints to FPGA primitives in the design.

- Using Floorplanner to create an RPM from a place and routed design.

The manual assignment of rloc constraints is done in the HDL code. A major drawback of this approach is that it can only be used for FPGA primitives directly instantiated in the design. rloc cannot be applied in HDL to primitives inferred by the design tools. Obviously this approach is only useful for very small macros. In this project this approach is used in the delay elements in section 2.5.3, in the mutex in section 2.5.2, and in Petrify circuits in section 2.7.2.

The Xilinx Floorplanner tool is able to create an RPM macro based on a placed and routed design. After place and route the design is loaded into Floorplanner, which extracts the relative placement of all primitives as rloc constraints and writes them to the UCF file. The netlist and UCF file is then combined to a macro file, which can be instantiated in another design as a black box macro. Detailed information about the RPM creation process can be found in the Xilinx Application note in [31] and in the Floorplanner documentation [30].

When designing an asynchronous system it will be highly desirable to be able to delay match small subcomponents individually and then create an RPM macro component with locked placement. When connecting several RPM macros only the routing between the macros will be able to inflict incorrect timing. To create an RPM of a subcomponent the Floorplanner approach must be used, unless the subcomponent solely consists of instantiated FPGA primitives. Unfortunately it has not been possible to successfully create an RPM macro of an asynchronous design using Floorplanner. In the following the problems encountered will be explained.

When Floorplanner is used to extract the relative placement of the design primitives it does not include all primitives present in the design. Some primitives are present in the Floorplanner design hierarchy but are unplaced. Other primitives are not even present in the Floorplanner design hierarchy even though they are present when the design is loaded into FPGA Editor. It has been determined that all problematic primitives are LUTs which is marked as "route throughs". A LUT is used as a "route through"-LUT to let a signal get access to slice resources that is only accessible through a LUT. This situation may arise if the internal slice signal dedicated to bypass the LUT are already used by other logic. Because a "route through" does not perform any function in the design but is solely used as a routing resource, it may be the reason that it is not included in the RPM. However, it has not been possible to find any Xilinx documentation to support this theory. Consequently all C-elements are marked as "route throughs" LUTs and thereby not included in the RPM macro. The marking of a C-element as a "route through" does not really make any sense. As C-elements are a vital part of any asynchronous circuit it is crucial to include them in the RPM. Also simple mux'es and demux'es have suffered from the same problem. Even a strictly combinatorial demux circuit is found to give trouble. It has been tried to rewrite the HDL code to see if that could solve the

2.7 Design Flow 33

problem, without any success. A description of the problem have been posted to the Xilinx user forums and the internet newsgroup comp.arch.fpga but no replies have been received. The forum post is included in appendix A.4. Since also non-asynchronous circuits suffer from problems it is suspected to be caused by a bug in the Floorplanner software. It should be noted that RPMs can successfully be created from other combinatorial circuits using the Floorplanner tool.

The inability to create RPMs of asynchronous components has the consequence that a larger margin must be included in the matched delay, however it has not proved to be a major issue as long as performance does not have high priority.

# 2.7 Design Flow

This sections aims at describing the design flow for implementing asynchronous circuits using the Xilinx tools. On the basis of the results from the experiments on the delay element presented in section 2.6.1 a guideline for delay matching is presented in section 2.7.1. The design flow for implementing Petrify circuits is presented in 2.7.2. In section 2.7.3 various settings and constraints used for the Xilinx tools are described.

# 2.7.1 Delay Matching Guidelines

This section describes the work flow for performing delay matching of a circuit. The output port component from the router design (section 4.2.2) is used as an example.

Wire and gate delays will introduce different propagation delays for the handshake signals and for the data signals. The 4-phase bundled data protocol requires that the data are valid before the request signal is asserted. If the request signals have a smaller path delay than the data signal (which they will have in most cases) the request signals must be delayed to obey the handshake protocol. If not, the receiver may latch invalid data.

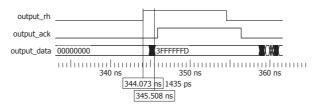

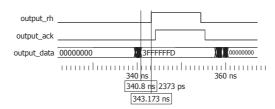

When measuring the required delay one should make sure that all data signals make a transition, because all the data signals will have different propagation delays. In the example below it has been aimed at that all data signals makes a  $0 \rightarrow 1$  transition, but to assure that the packet follows the correct path through the router this has not been possible for all data signals. Figure 2.20(a) shows

### (a) before delay matching

(b) after delay matching

Figure 2.20: Modelsim print of a request signal in an router output port before and after delay matching.

a Modelsim print of a handshake transaction in an output port: output\_rh is the request output and output\_data is the output of the data latch. A curser marks the time when the request signal is asserted and another curser marks when the output of the data latch is stable. The figure shows a difference of 1.4 ns. The chart in figure 2.18 (b) (p. 28) is used to estimate the size of the delay element. According to the delay chart a size of 3 should give a delay of about 2 ns. To allow for the delay fluctuations mentioned in section 2.6.1 an extra delay should be inserted. The experience from this project is that in general a delay overhead of about 2-3 ns is sufficient to cover the delay fluctuations. Thus, the target is a delay of about 4 ns. According to the delay chart a size of 8 should give a delay in the target range. After the insertion of a delay element with size 8, the design is synthesized and implemented again. A Modelsim print of the handshake transaction after insertion of the delay element is shown in figure 2.20(b). After insertion of the delay element the delay overhead is 2.4 ns, which lies in the target range. It should be noted that a delay overhead of 2-3 ns is a quite conservative estimate. In many cases a smaller overhead will be sufficient.

In a larger design with many instances of the same component it is not feasible to manually check if each and every delay element is sufficiently large. By following the handshake protocol it is guaranteed that the correct data is latched, but even if the handshake protocol is not completely obeyed data might be correctly

2.7 Design Flow 35

latched anyway. In other words, the primary goal is not to assure that the handshake protocol is strictly followed under all circumstances but to assure that correct data is latched in all cases. The Modelsim simulation tool will issue warnings if a latch experience setup or hold time violations. If the simulation of the complete system does not result in any warnings it indicates that the delay matching is sufficient.

### 2.7.2 Petrify Circuits

This section presents the design flow for implementing control circuits synthesized by Petrify [6].

Petrify is a tool which synthesizes speed-independent control circuits specified by State-Transition Graphs (STGs). An STG is a way to specify a timing diagram in a formal way and is based on Petri nets. The tool Visual STG Lab (VSTGL) is a visual tool for creating and simulating STGs and it has been used in this project for the creation of STGs. The input to Petrify is an STG and the output is a set of boolean equation which implements the circuit. Petrify automatically solves Complete State Coding (CSC) violations by inserting extra state variables, however the designer should try to limit the amount of needed CSC state variables to as few as possible. The amount of needed CSC state variables can be reduced by redesigning the STG specification.

The general process of implementing a circuit specified by an STG and synthesized by Petrify is described in chapter 6 in [24]. The process of mapping a set of petrify equations onto an FPGA is described in [26]. Two different methods is presented in [26]:

- Complex gates.

- Generalized C-elements.

When the target is a complex gate implementation Petrify generates equations such that each non-input signal is implemented by a single complex gate. The -cg option is used to instruct Petrify to target a complex gate implementation. A complex gate must be implemented in a single LUT element, hence the number of inputs to a complex gate is limited by the number of inputs available on a LUT. The state-holding capabilities of the complex gate is implemented as a feedback input, in the same way as in the implementation of the C-element in section 2.5.1. The reset signal can be implemented using an internal MUX in the slice such that it does not occupy an input on the LUT. In [26] an FPGA

Figure 2.21: Implementation of a Petrify circuit using a C-element.

with 4-input LUTs is used, thereby leaving 3 inputs free. With the 6-input LUTs available in the Virtex-5 FPGA a 5-input complex gates is the maximally possible to implement. If more inputs is needed Petrify must be used to do speed-independent preserving decomposition else the circuit will not be hazard free.

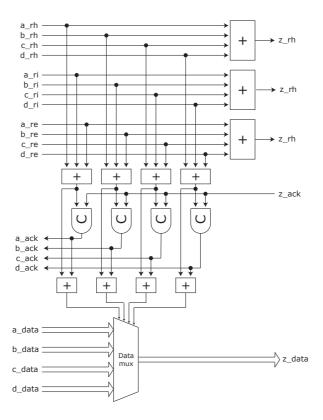

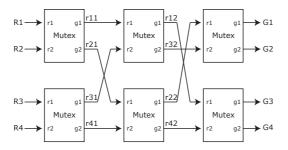

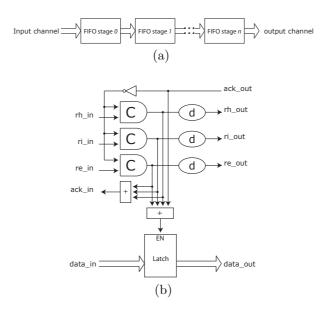

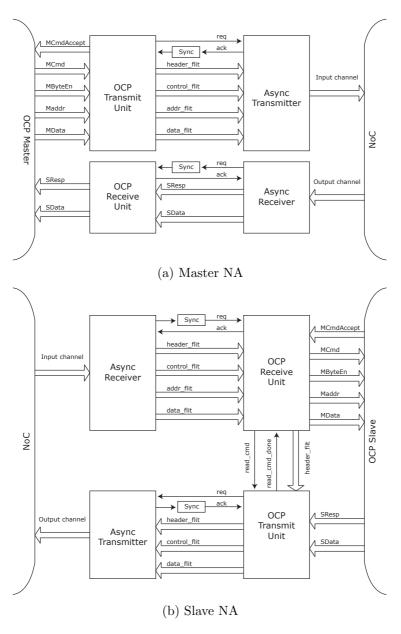

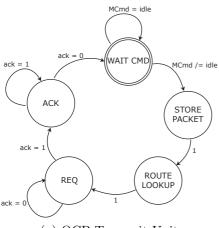

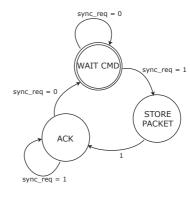

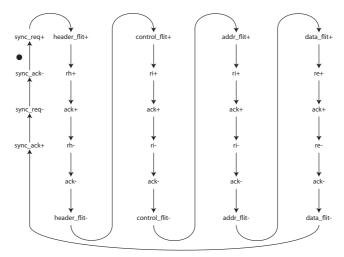

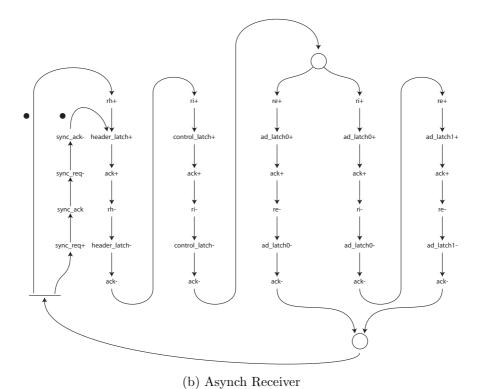

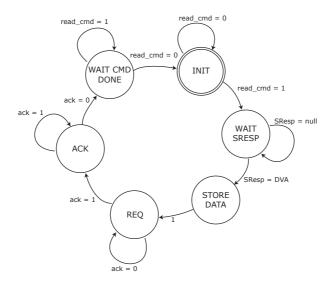

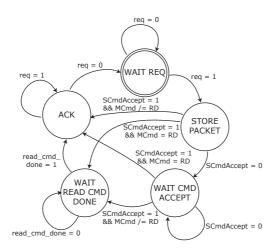

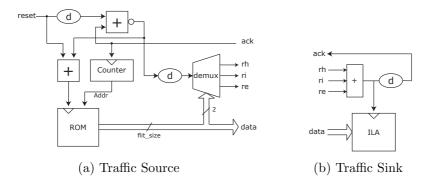

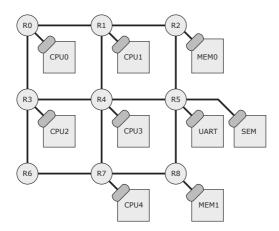

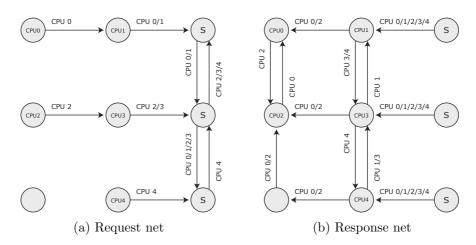

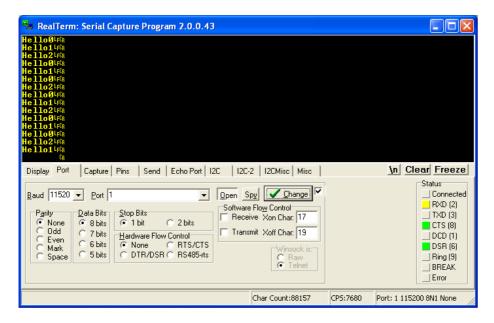

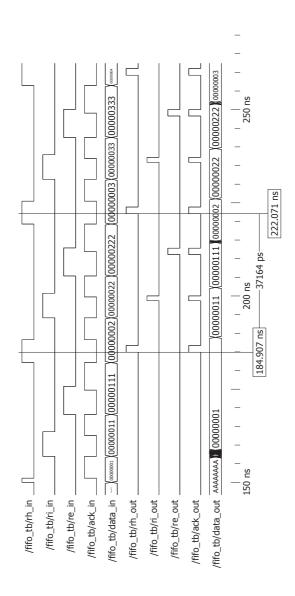

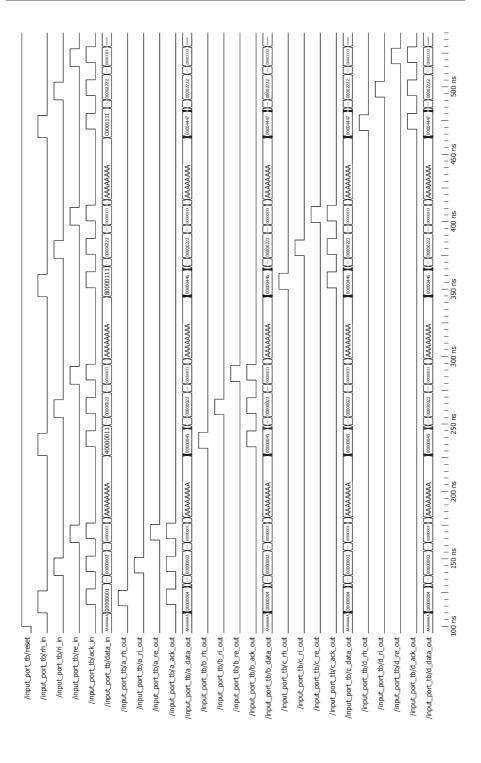

A solution based on generalized C-elements uses a state-holding element. The state-holding element can be either a set-reset latch or a C-element. Petrify generates equations implementing the set and reset functions for the state-holding element. When a SR latch is used the set and reset functions are wired to the set and reset input of the SR latch respectively. When a C-element is used the set function is wired to one input and the complemented reset function is wired to the other input. To be able to control the initial state of the SR latch or the C-element a reset signal must be used. For the SR latch implementation an internal mux can be used to save an input of the LUTs implementing the set/reset functions as with the complex gate. The C-elements already have a separate reset input. The set/reset functions can have up to six inputs. If a larger number of inputs is needed several LUTs can be combined in a sum-ofproducts configuration. To assure that the sum-of-product implementation is hazard free. Petrify must be instructed to apply the monotonic cover constraint, using the -gcm option. With the monotonic cover constraint only one term in the sum-of-products implementation is allowed to be high at a time, thus eliminating the possibilities of static and dynamic hazards. In [26] the generalized C-elements are implemented using SR latches.