### Design Optimization of Safe and Secure Real-Time Systems

Jakob Menander

Kongens Lyngby 2014 IMM-M.Sc.-2014-xxxx

Technical University of Denmark Department of Applied Mathematics and Computer Science Matematiktorvet, building 303B, 2800 Kongens Lyngby, Denmark Phone +45 4525 3351 compute@compute.dtu.dk www.compute.dtu.dk IMM-M.Sc.-2014-xxxx

# Summary (English)

Many languages uses a single expression to cover the two English terms: Safety and Security. In Danish the term "sikkerhed" is used, in German they use the term "sicherheit" and even in Chinese they use only one single expression [LRNT06].

The meaning behind the term "safety", is to make sure that people and the environment are protected from harm caused by a faulty system, e.g. to protect the driver of a vehicle by releasing the airbags at impact or to prevent the impact altogether by making sure that the breaks and ABS are working as they are meant to. The definition of the term "security" is to protect information in a given system from being leaked, manipulated or forged by third parties or systems. For example we expect protection of our private information so it will not fall into the wrong hands. So one might think of safety and security as two nearly identical words which has a lot of similarities, but their objectives for protection are each other's opposites.

Conventionally, safety systems have not been concerned with security, e.g. the pressure in a steam engine secured by a safety valve, and the systems involved contained no information that could be revealed. Security related system did not have the need for using safety abilities, since security was something one would handle with a vault.

As time went by, electric and computer controlled systems, such as automatic factory machines, saw the day, but focus was mostly still on safety and not on security. With the increased use of the internet, security has become a larger part of the online universe. The internet are used to transport many sensitive information and they are now available on more media and devices, e.g laptops, smartphones, etc. In other words, the internet allows us to communicate on different devices and exchange information. Safety systems might communicate with other systems through the internet or wireless protocols. This fusion of safety and security has made it necessary for industries that only had to think of incorporating safety in their design, now also have to incorporate security.

The aim of this thesis is to shed light on the issue of incorporating security in a safety system. Based on an existing safety system, I will come with a realistic estimate on how it can expand and also cover the fundamental capabilities in security.

I will base my work on a system called "Multiple Independent Levels of Security (and Safety)" (MILS), which is already designed to keep the integrity of the information, which is a capability in both safety and security.

Thus, security is already incorporated in the system in terms of protecting the integrity, but security also has another property, which in many systems will be described as the primarily property: confidentiality.

"Confidentiality" can be divided into two areas: Preventing information from being passed on to unauthorized persons or systems, and preventing comprehension of information if it should fall into the wrong hands. The first area creates a challenge because information should not flow downwards to a lower security level. This is exactly opposite of the integrity property in safety, where information flow is not allowed to move up a level. The second area needs to prevent a person to get valuable knowledge, if he/she should forcefully gain access to the information. This means that information has to be encrypted.

Both areas of security will be covered in the report and a proposal of how it can be implemented and which consequences a design choice will have on a system.

# Summary (Danish)

Begrebet "sikkerhed" kan traditionelt tolkes på to forskellige måder. Begrebet "safety" dækker over det at sikre personer eller omgivelserne mod at tage skade fra et givet system. Det kunne være at beskytte føreren af en bil, ved at udløse airbags ved en ulykke, men det kunne også være at sikre at ulykken ikke vil indtræde i første omgang, ved at sikre at eksempelvis bremser og ABS virker efter hensigten. Omvendt dækker begrebet "security" over det at beskytte informationer i et givet system fra at blive afsløret, manipuleret eller forfalsket af personer eller systemer udefra. Eksempelvis vil vi gerne have vores private oplysninger ikke falder i forkerte hænder. Så selvom man i første omgang tænker på safety og security som to næsten identiske begreber som rummer mange ligheder, er deres mål for beskyttelse modpoler til hinanden.

Traditionelt set har safety systemer ikke haft brug for security. Damptryk sikrede man med en sikkerhedsventil og systemerne indeholdte ingen information som kunne afsløres. Security relaterede systemer havde heller ikke brug for safety egenskaber, da security ofte var noget man ordnede med en bankboks.

Sener fik man elektriske og computer styrede systemer, som automatiserede fabriksmaskiner, men fokus var stadigvæk på safety og ikke på security.

Med internettets fremhersken er security blevet en større og større del af det online univers. Internettet bruges til at kommunikere et utal af følsomme informationer og informationerne er tilgængelige på flere og flere medier og enheder. Med andre ord, internettet tillader forskellige enheder at kommunikere sammen og udveksle informationer. Også safety systemer gør brug af at kommunikerer med andre systemer over lokale netværk, trådløse protokoller eller internettet. Denne sammensmeltning at safety og security, er med til at en påkræve at en industri som før kun skulle indtænke safety i deres design også skal til at indtænke security.

Målet med dette speciale er at belyse problemstillingen med at inkorporerer security i et safety system. Med udgangspunkt i et eksisterende safety system, vil jeg komme med et reelt bud på hvordan det kan udvides til også at dække de basale egenskaber i security.

Jeg tager udgangspunkt i et system som hedder "Multiple Independent Levels of Security (and Safety)" (MILS) og som allerede er designet til at varetage integriteten af informationer, hvilket er en egenskab i både safety og security. Dermed er security allerede inkorporeret i systemet i form af beskyttelse af integriteten, men security indeholder i midlertidig også en anden egenskab, som i mange systemer vil blive betegnet som den primære egenskab, nemlig fortrolighed.

"Fortrolighed" kan deles op i to grene: At forhindre informationer i at blive videregivet til uautoriseret personer eller systemer og at forhindre forståligheden af information hvis de alligevel skulle falde i de forkerte hænder. Den første egenskab byder på en udfordring, da det reelt betyder at informationer ikke må flyde nedad til et lavere sikkerheds niveau. Dette er stik modsat integritets egenskaben i safety, hvor informationer ikke må bevæge sig op i niveau. Den anden egenskab skal forhindre en person i at få nyttig viden, hvis han selv fremtvinger sig adgang til informationerne. Dette betyder at informationerne skal krypteres.

Begge aspekter af security belyses i rapporten og jeg giver et bud på hvordan det kan implementeres og hvilke konsekvenser et given design valg kan få for systemet.

## Preface

This thesis was prepared at the department of Informatics and Mathematical Modelling at the Technical University of Denmark in fulfilment of the requirements for acquiring a M.Sc. in Informatics.

The thesis is a research project and deals with the problem of combining safety and security in embedded systems. Based on a known safety system with a layer of security integrity, I propose methods to add security confidentiality to the system.

The thesis consists of five chapters, including an introduction and conclusion, and two appendixes with abbreviations and notations.

The work has been supervised by Associate Professor Paul Pop and co-supervised by Associate Professor Christian D. Jensen.

Lyngby, 11-July-2014

Jalud Mamand

Jakob Menander

## Acknowledgements

I would like to thank my supervisor Associate Professor Paul Pop a lot for giving me the chance to work on this thesis. The thesis was customised to a desire to work with security in the safety domain and I thank Paul Pop for creating this thesis for me.

I would also like to thank him for his guidance, input and feedback through the work and for suggesting relevant articles.

A big thank shall also be given to my co-supervisor Associate Professor Christian D. Jensen for guidance and input of the security part of the thesis and to PhD Domitian Tamas-Selicean for review and feedback on the report.

The biggest thanks goes to my girlfriend Caroline and our daughter Ella, whom has grown from 5 to 10 months during this thesis. Without their love and support, the thesis would not have been a possibility.

Jakob Menander July 2014, Copenhagen viii

## Contents

| Summary (English) i |       |                                                             |     |  |  |  |  |  |  |

|---------------------|-------|-------------------------------------------------------------|-----|--|--|--|--|--|--|

| Su                  | ımma  | ary (Danish)                                                | iii |  |  |  |  |  |  |

| Pr                  | eface |                                                             | v   |  |  |  |  |  |  |

| Ac                  | knov  | vledgements                                                 | vii |  |  |  |  |  |  |

| 1                   | Intr  | oduction                                                    | 1   |  |  |  |  |  |  |

|                     | 1.1   | Safety and Security Properties                              | 2   |  |  |  |  |  |  |

|                     | 1.2   | Security Models                                             | 3   |  |  |  |  |  |  |

|                     | 1.3   | Multiple Independent Levels of Security (and Safety) (MILS) | 4   |  |  |  |  |  |  |

|                     | 1.4   | ACROSS MPSoC                                                | 5   |  |  |  |  |  |  |

|                     | 1.5   | Attacker model                                              | 5   |  |  |  |  |  |  |

|                     | 1.6   | Contribution                                                | 7   |  |  |  |  |  |  |

| <b>2</b>            | App   | Application Model                                           |     |  |  |  |  |  |  |

|                     | 2.1   | Notation                                                    | 9   |  |  |  |  |  |  |

|                     | 2.2   | Rules                                                       | 10  |  |  |  |  |  |  |

|                     | 2.3   | Safety and Security Level                                   | 12  |  |  |  |  |  |  |

|                     |       | 2.3.1 Safety Level                                          | 13  |  |  |  |  |  |  |

|                     |       | 2.3.2 Security Level                                        | 14  |  |  |  |  |  |  |

|                     | 2.4   | Application Examples                                        | 14  |  |  |  |  |  |  |

| 3                   | Arc   | hitecture Model                                             | 17  |  |  |  |  |  |  |

|                     | 3.1   | The Architecture                                            | 18  |  |  |  |  |  |  |

|                     |       | 3.1.1 The Trusted Architectural Layer                       | 19  |  |  |  |  |  |  |

|                     |       | 3.1.2 The Top-Layer                                         | 21  |  |  |  |  |  |  |

|                     | 3.2   | Architecture Examples                                       | 25  |  |  |  |  |  |  |

|               |                 | 3.2.1                  | The ACROSS MPSoC Architecture                                                                                                                         | 25 |  |  |

|---------------|-----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|               |                 | 3.2.2                  | Simple VaM Example                                                                                                                                    | 26 |  |  |

|               |                 | 3.2.3                  | The Partitioning                                                                                                                                      | 26 |  |  |

|               | 3.3             | Safety                 | Mechanism                                                                                                                                             | 28 |  |  |

|               |                 | 3.3.1                  | Separation and Partitioning                                                                                                                           | 28 |  |  |

|               |                 | 3.3.2                  | Redundancy / Diversity                                                                                                                                | 29 |  |  |

|               |                 | 3.3.3                  | Time-Triggered Architecture                                                                                                                           | 29 |  |  |

|               |                 | 3.3.4                  | Trusted Subsystem                                                                                                                                     | 29 |  |  |

|               | 3.4             | Securi                 | ty Mechanism                                                                                                                                          | 30 |  |  |

|               |                 | 3.4.1                  | Individual Integrity and Confidentiality Level                                                                                                        | 30 |  |  |

|               |                 | 3.4.2                  | Separation and Partitioning                                                                                                                           | 31 |  |  |

|               |                 | 3.4.3                  | The Trusted Subsystem                                                                                                                                 | 32 |  |  |

|               |                 | 3.4.4                  | Secure Channel                                                                                                                                        | 32 |  |  |

|               |                 | 3.4.5                  | Crypto Component                                                                                                                                      | 32 |  |  |

|               | 3.5             | $\operatorname{Behav}$ |                                                                                                                                                       | 33 |  |  |

|               |                 | 3.5.1                  | VaM                                                                                                                                                   | 33 |  |  |

|               |                 | 3.5.2                  | Secure Channel                                                                                                                                        | 34 |  |  |

|               | 3.6             | Assum                  | nptions                                                                                                                                               | 36 |  |  |

|               |                 | 3.6.1                  | TSS Is Free For Design Faults                                                                                                                         | 36 |  |  |

|               |                 | 3.6.2                  | No Malicious Attack Before Runtime                                                                                                                    | 37 |  |  |

|               |                 | 3.6.3                  | No Malicious Attack on TTNoC                                                                                                                          | 37 |  |  |

|               |                 | 3.6.4                  | Not Looking Into the TTNoC                                                                                                                            | 37 |  |  |

|               |                 | 3.6.5                  | One Combined Safety-Security-Level                                                                                                                    | 37 |  |  |

| 4             | $\mathbf{Des}$  | ign Ta                 | sks                                                                                                                                                   | 39 |  |  |

|               | 4.1             | 0                      | lesign decisions influence the system                                                                                                                 | 39 |  |  |

|               |                 | 4.1.1                  | Safety                                                                                                                                                | 39 |  |  |

|               |                 | 4.1.2                  | Security                                                                                                                                              | 40 |  |  |

|               |                 | 4.1.3                  | $Schedulability \ldots \ldots$ | 44 |  |  |

| 5             | Cor             | nclusio                | n                                                                                                                                                     | 47 |  |  |

| Α             | Abl             | oreviat                | ions                                                                                                                                                  | 49 |  |  |

|               |                 |                        |                                                                                                                                                       |    |  |  |

| в             | B Notations 51  |                        |                                                                                                                                                       |    |  |  |

| $\mathbf{Bi}$ | Bibliography 53 |                        |                                                                                                                                                       |    |  |  |

### CHAPTER 1

## Introduction

The terms Safety and Security [LRNT06] have a lot in common, but they are also each other's opposites and obstructing each other. The close relation can be experienced in a lot of languages where safety and security is described together in one single word, e.g. in Danish the word "sikkerhed" covers both safety and security. In common they describe a "system" in an environment. Distinct from each other, safety aims for protecting the environment from the system, while security aims for protecting the system from the environment. Software designed with a safety purpose focuses on handling random (and maybe some periodic) faults caused by the system [HH09], while software designed for security focuses on protecting the information in the system from malicious parties.

Traditionally, embedded systems are used in the safety industry without any security, as the embedded systems operate in a closed environment, where direct access has to be obtain by an intruder to compromise the system. Systems built with focus on security are often associated with online systems with no relation to safety. But in these days where embedded safety systems are growing in size and complexity, with communication over open networks and possibly connected with the internet, security is needed to ensure the safety mechanisms.

#### 1.1 Safety and Security Properties

Safety has two major properties; availability and integrity. In some systems, e.g. avionics, availability is more important than integrity, as the aircraft would otherwise crash. In other systems, e.g. medical instruments where the wrong dosage may be lethal, integrity is of higher importance. Despite of the importance of availability in some systems, availability is out of the scope of this thesis and I will only focus on integrity.

Security is mostly associated with its confidentiality property, but integrity is also a property in security. I will cover confidentiality as well as the integrity. It is worth to note that safety does not hold a confidentiality property, as disclosure of information would not affect the safety in a pure safety system. There are two major ways to prevent information to be disclosed. One is to control the information flow, such that a trusted message carrying secret information would never end at an untrusted endpoint. The other procedure is to prevent an untrusted intruder from getting information from a snooped message, i.e. cryptographic algorithms would prevent revealing of secret information.

Integrity is a property of both safety and security, but the meaning of safety integrity and security integrity is not the same. Safety integrity is the ability of a safety function to continue to be effective in spite of partial loss of its implementation measures [LRNT06]. Security integrity requires that an altering of the information must not be performed by unauthorised process or subject and an authorised process or subject must not make any unauthorised altering to the information. It is also required that the information will not change due to events that happen inside or outside the system that are not meant to change the information [KF09]. We can interpret safety integrity as a unit that is introduced to the environment and the environment will remain in a safe state after introduction of the unit, i.e. the environment will not change after the introduction of the unit. Furthermore we can interpret *security integrity* as a unit we can add information to and even if an intruder should try to change the information it can never be changed and will remain unchanged. So both safety and security wants to protect alternation (environment/information) after introducing an event (the unit/an intruder). I will in the thesis interpret safety integrity and security integrity as one single property: integrity, as violation of the integrity will affect both safety and security.

#### 1.2 Security Models

As mentioned in 1.1, security is mostly associated with its confidentiality property and confidentiality is often associated with cryptographic algorithms. Another part of confidentiality is to avoid information to be leaked to untrusted parties. In 1973 Bell and LaPadula [BL73] published a security model where a downward information flow was prohibited. The model is commonly known as no read up, no write down and formed a basic security model that ensures the confidentiality of the information flow, by disallowing a subject to read information of a higher classification and to write information to a lower classifying object and thereby declassify information to a lower and less secure level.

Bell and LaPadula's model only focuses on confidentiality without considering integrity. In 1977 Biba [Bib77] proposed a complimentary model with a reverse information flow. Biba's integrity model is commonly known as *no read down*, *no write up* and prevents low integrity information from being upgraded to a higher integrity level.

Biba's integrity model is the foundation for most safety models, but is in its pure form too strong and restrictive to use in practice. One of the issues with Biba's integrity model is that information would be downgraded over time, as information could only flow from one integrity level to equal or lower integrity levels. Totel [TBDP98] proposed in 1998 a model based on Biba, but where Biba's model only has the ability to downgrade information, due to the writedown policy, Totel's integrity model preserves the integrity level and can even promote information of a lower integrity level to a higher integrity level. To do that, he introduced three kind of objects, where an object is defined as an entity providing one or multiple services to a subject or another object. The three kind of objects are (1) Single-Level Objects  $(SLO)^1$  with a constant integrity level. (2) Multi-Level Objects (MLO) with the ability to modify the integrity level to reflect the integrity level of the invoker. They have no "memory" and they restore their integrity level when freshly created. The third (3) is a Validation Object (VO), which has a single level of integrity, but takes input from redundant or diverse objects with a lower integrity level. The output would be at the same integrity level as the VO itself. E.g. a VO would take input from low level sensors to validate them together to a single high level output.

There arises a big problem when systems grows bigger and more complex: The certification of the system. In Totel's integrity model the whole system would be certified as once. There was a need to divide the system up in smaller pieces, easier to certify. Rushby [Rus81] introduced in 1981 the concept of separate

<sup>&</sup>lt;sup>1</sup>A full list of abbreviations can be found in Appendix A.

subsystems. A *Separation Kernel* (SK) isolates processes from each other and the single subsystems could now be certified individual. This made it much easier to design and maintain more complex safety systems.

#### 1.3 Multiple Independent Levels of Security (and Safety) (MILS)

Based on the concept of separation, the *Multiple Independent Levels of Security* (and Safety) (MILS) approach was described in 2005/2006 [AFHOT06]. MILS consists of three layers [BDRS08], with the SK as the lowest layer. Next comes a *Trusted Subsystem* (TSS) ensuring the communication between the applications. On top of that is the last layer where the untrusted application services are executed.

Where Totel's integrity model is designed to run on a single processor [WM12], the MILS is designed for *Multi-Processor System-on-a-Chip* (MPSoC) devices. To support the architecture a *Time-Triggered Network-on-a-Chip* (TTNoC) was introduced in 2010 [WESK10] as the communication network. This ensures both a spatial and temporal separation in the transportation of messages.

The *Time-Triggered* (TT) network is preferred over an *Event-Triggered* (ET) network. An ET network may deliver the message from an asynchronous event faster than TT, but the messages may also be delayed if many events are triggered at the same time. TT may not send a message at the occurrence of an event, but every process is guaranteed a sending slot in an a priori known point in time and within a given deadline. This makes TT less flexible than ET, but more deterministic, fault tolerant and manageable for the designer of the architecture [Alb04]. The deep integration of TTNoC makes MILS a *Time-Triggered Architecture* (TTA).

MILS consists of components (or  $\mu$  Components) [WESK10] connected together by a TTNoC. The components can be assigned independent security levels, which will affect the possible information flow, but also affect the cost for validation in time and money. The higher the level, the higher the cost. A Trusted Interface Subsystem (TISS) provides the interface between the components and the TTNoC. A Trusted Network Authority (TNA) manages the routes in the TTNoC and a Resource Management Authority (RMA) guards for unauthorised changes of the TNA. The routes are called Encapsulated Communication Channels, which means they are unidirectional communication channels with one sender and one or several receivers at a specific point in time. To cope with the inflexibility of Biba's integrity model, a middleware can be placed between the application and the TISS. This middleware can be designed to validate redundant input and functions in the same way as the VO in Totel's integrity model.

MILS is basically an integrity model with a downward information flow. Cryptographic algorithms can be added to ensure the secrecy of information and thereby adding a bit of confidentiality to the system. It is possible to reverse the information flow [WESK10] from downward to upward and thereby get a pure confidentiality model, but then the integrity is neglected.

#### 1.4 ACROSS MPSoC

MILS is only described theoretical and the industry lacks a MPSoC system with focus on safety. An European project, the ARTEMIS ACROSS project, was formed in  $2010^2$  to come up with such architecture [SEH<sup>+</sup>12]. The result was the ACROSS MPSoC architecture; a MILS system. Small variations in the descriptions of the architecture can be found, e.g. the TNA and RMA described in [WESK10] are combined to a *Trusted Resource Manager* (TRM) in the descriptions of the ACROSS MPSoC architecture [WM12].

Further in this thesis I will use the ACROSS MPSoC architecture and describe it in extensive details.

#### 1.5 Attacker model

But why is security and specially security confidentiality needed in a safety system? Of course the integrity needs to be preserved even after a malicious attack or it would endanger the safety, but what information in a safety system needs confidentiality?

An intruder may have several interests in attacking the system. He might want to drain the system for information by eavesdropping on the communication, he might want to take control of the system or simply to put it out of function. The intruder can choose to attack the components, the communication channel or a combination of both.

A car is a safety system we also want to be secure. Most cars these days are

<sup>&</sup>lt;sup>2</sup>The ACROSS project was closed again in 2013. http://www.across-project.eu

relying more and more on embedded systems, so called *Electronic Control Units* (ECU), and in a near future most car will have steer- and brake-by-wire, i.e. mechanical and hydraulic will be substituted by ECUs. As said, most modern cars contain a lot of ECU, but the architecture binding the ECUs together offer no security. In new cars, it is possible to connect a mobile phone to manage and upgrade the GPS, provide easy handfree communication, listen to music stored on the mobile device, etc. This means that a you can connect a device that is not validated for safety nor security, to the internal system. A mobile phone has often access to the internet and an attack via the internet through the mobile phone, could give a malicious intruder access to the internal systems. One can also conceive that access to the internet integrated directly in the internal system, is not of a distance future.

But an attack on a safety system may not only be at runtime. It is reasonable to conceive that attacks take place in the development phase. A malicious employer may implement a backdoor or malicious code may find its way through the internet on the machine the system is developed on. Even the use of USB sticks can cause malicious code to be implemented into the system.

But what makes a malicious attack on a car desirable for an intruder? By eavesdropping, an intruder can listen to conversations in the car, as more and more cars have a microphone integrated to enable the driver to talk handless in his mobile phone. The information (e.g. the contact list or messages) on a mobile phone connected to the cars integrated system can also be leaked. Information on the cars position (GPS) or its general status (e.g. the speed or odometer) can also be of interest of an eavesdropper.

If messages from the ECUs is kept in a black box for future investigations, e.g. after a traffic accident, altering messages can be used in assurance fraud. Altering messages can also be used to make a car appear less used by altering the data of the odometer, which will result in a higher sales price if it is resold.

Deleting messages to the inflater of an airbag, would cause the airbag to not function. In a combination with deleting messages from the foot brake sensors the result could be fatal, as the car could crash without inflating the airbags. It could also just be limited to an annoying character, by disable e.g. the heater, air condition, windows or even the engine.

Adding information could result in executing commands and more or less taking over the system. Annoying functions could be activated (e.g. activating the horn in a car), but also potential dangerous functions as releasing the airbags at full speed or turn off the light of a car, can be activated. In cars with drive-by-wire, an intruder can also take control by steering the car. With this in mind, tomorrow's safety systems cannot rely on safety alone any more. Security need to be added to ensure the safety properties.

#### 1.6 Contribution

The ACROSS MPSoC architecture is a safety architecture with a layer of security integrity and described in 2012 [WM12]. It is based on the MILS architecture from 2005/2006 [AFHOT06]. The architecture I use is therefore described earlier and is not new knowledge. My contribution is to analyse and suggest a method to add confidentiality to the ACROSS MPSoC architecture. A similar approach has been described in [WESK10], where a confidentiality flow is described at the expense of the integrity flow. In my system the integrity flow is preserved along with a confidentiality flow.

The information flow is only one part of confidentiality; the other part is the secrecy. I bring a Secure Channel [IW13] into the system to provide end-toend encryptions for communication over external network. For long lasting encryption I have proposed the use of a special Crypto Component and analysed what has to be take into account.

## Chapter 2

## **Application Model**

Integrity has been in focus in most MPSoC models. To extend such a model to also focus on confidentiality, we must provide some mechanisms to enforce confidentiality without compromising integrity. These mechanisms are primarily in the architecture, but in order understand and improve the architecture, we must understand the application model as well.

The proposed application model is an adoption and slightly reformulated version of the application model in [TSP13]. An entire list of notations can be found in Appendix B.

#### 2.1 Notation

An application  $\mathcal{A}_i$  is a direct, polar and acyclic graph  $\mathcal{G}_i(\mathcal{V}_i, \mathcal{E}_i)$  and the set of all applications is specified as  $\Gamma$ . The application graph  $\mathcal{G}_i$  consist of all nodes  $\mathcal{V}_i$  and all the edges between the nodes  $\mathcal{E}_i$  in the given application subsystem  $\mathcal{A}_i$ . Each node represent one task  $\tau_j \in \mathcal{V}_i$ . All nodes are mapped to *Processing Elements* (PE) by the function  $M : \mathcal{V}_i \to \mathcal{N}$  and a task in the node is associated to exactly one partition slice  $\phi(\tau_j) \to p_{ij}^k$  where  $\tau_j \in \mathcal{V}_i, \phi : \mathcal{V} \to \mathcal{P}$ . A partition is denoted  $P_j$  and a set of partition slices on  $N_i$  is denoted  $\mathcal{P}_{ij}$ . The  $k^{th}$  partition slice is denoted  $p_{ij}^k$ . The scheduling of tasks to partitions is made using *Static-Cyclic Scheduling* (SCS). In some cases two tasks are not allowed in same partition, e.g. two redundant tasks may not share partition, as both tasks could be affected of a failure in the partition. A *Protection Requirement Graph*  $\Pi(\mathcal{V}, \mathcal{E})$ , where  $\mathcal{V}$  is a set of all tasks and  $\mathcal{E}$  is the dependencies between them, enforce prohibition of sharing partitions. The edge  $sr_{ij} \in \mathcal{E}$  means that  $\tau_i$  and  $\tau_j$  are not allowed in the same partition.

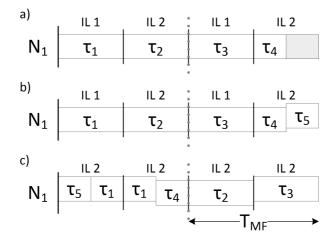

The edge  $e_{jk} \in \mathcal{E}_i$  has output from  $\tau_j$  and input in  $\tau_k$ . A task must receive all its input before its ready and will first output messages after termination. Messages  $m_i$  are used by tasks, located on different PEs to communicate with each other. The size  $s_{m_i}$  of  $m_i$  are known. The deadline  $D_{g_i}$  has be to reached within the period  $T_{g_i}$  for each  $g_i$ , i.e.  $D_{g_i} \leq T_{g_i}$ . The Worst-Case Execution Time (WCET)  $C_i$  are known for task  $\tau_i$ . Messages can only be sent at a priori known point in time according to a time scheme. The period of the time scheme  $T_{cycle}$  is repeated continuously. The  $T_{cycle}$  is divided in several Major Frames (MF) with a length given by the designer and with a period denoted as  $T_{MF}$ . The partitions are grouped together in MFs.

An integrity level  $IL : \mathcal{V}_i \to \{ILk\}$ , where  $k \in \{0, \ldots, 4\}$  (covering the integrity of both safety and security) and a confidentiality level  $CL : \mathcal{V}_i \to \{CLk\}$ , where  $k \in \{0, \ldots, n\}$  is assigned to every task in order to determine the restriction of the information flow and certification. A task  $\tau_i$  is assigned both an integrity level  $IL(\tau_i)$  and a confidentiality level  $CL(\tau_i)$  independent of each other.

#### 2.2 Rules

There are some rules to follow to ensure the safety and security requirements. The rules are an adaptation of the rules proposed in [WM12], with some addition to cover not only integrity, but also confidentiality.

Rule 1: A task is placed in exactly one partition slice and is allowed to share partition with another task *iff* the two tasks do not share an edge in  $\Pi$  and they have same integrity and confidentiality level.

The integrity level and the confidentiality level of a task may be set so low that they will be non-critical and not impact the safety and security of the system. Even though, both an integrity level and confidentiality level must be assigned a task. *Rule 2:* A task is assigned exactly one integrity level and exactly one confidentiality level.

Communication between tasks is done by passing messages over the communication channel. To apply Biba's integrity model [Bib77] we must ensure a downward information flow.

Rule 3: The information flow is allowed, only if the sending task has a higher or equal integrity level than the receiving task;  $IL(\tau_{send}) \geq IL(\tau_{receive})$ .

In a model dealing with both integrity and confidentiality, the upward confidentiality flow proposed by Bell and LaPadula [BL73], apply as well as the downward integrity flow. The confidentiality flow is an extension of the original rules proposed in [WM12]

Rule 4: An information flow from one task to another is allowed only if the sending task has a lower or equal confidentiality level than the receiving task;  $CL(\tau_{send}) \leq CL(\tau_{receive}).$

Rule 3 enforces a rigid downward information flow, where information can only flow downward, and that is not practical to work with. The downward flow can be circumvented in rule 5 by allowing an upward flow, if the information is validated to a higher integrity level.

*Rule 5:* Messages from a task with a low integrity level to a task with a higher integrity level must pass through a *Validation Middleware* (VaM). The VaM must receive information from several different redundant or (even better) diverse tasks, with a lower integrity level than the VaM. The information must be received within a given time span.

While rule 5 relaxes the information integrity flow in a safe and secure manner, where information is validated and upgraded to a higher integrity level, the confidentiality flow is relaxed in a way where sensitive information is filtered out of the information flow.

*Rule 6:* Information can flow from a task with a high confidentiality level to a task with a lower confidentiality level *iff* sensitive data is filtered out of the messages or the message is protected by encryption with no possibility to decrypt at the receiving task.

As long as tasks are communicating on-chip through the TTNoC, eavesdropping is not possible. But off-chip communication cannot guarantee the confidentiality of the information. **Table 2.1:** The three colons from left indicates a task and its configuration. The colon to the right indicate the possible flow to other tasks.  $\tau_2$  can only send messages to other tasks with the same configuration, while the configuration of  $\tau_3$  allows it to send messages to every other task without regard to their configuration.

| $	au_i$ | $IL(\tau_i)$ | $CL(\tau_i)$ | $\  \tau_i \to \mathcal{V}_j$                   |

|---------|--------------|--------------|-------------------------------------------------|

| $	au_1$ | L            | L            | $\tau_1 \to \{\tau_1, \tau_2\}$                 |

| $	au_2$ | L            | Н            | $	au_2 \to \{	au_2\}$                           |

| $	au_3$ | Н            | $\mathbf{L}$ | $\tau_3 \to \{\tau_1, \tau_2, \tau_3, \tau_4\}$ |

| $	au_4$ | Н            | Н            | $ \tau_4 \to \{\tau_2, \tau_4\} $               |

Rule 7: Information must be encrypted before sending through an external network.

#### 2.3 Safety and Security Level

Rule 2 dictates that a task is assigned exactly one *Integrity Level* (IL), covering both the safety integrity and the security integrity, and one Confidentiality Level (CL). The consequence of these two separate levels is that messages can flow free from a task with a high IL and low CL, while information from a task with a low IL and high CL are limited to send messages to other components with the same configuration. A simple example where the security levels can be either High (H) or Low (L) is shown in Table 2.1. The table illustrates the allowed flow from one configuration of tasks to another configuration. The three colons to the left indicates a task  $\tau_i$  and its IL and CL configuration. The color to the right indicates the possible flow from  $\tau_i$  to other tasks with different configurations. One could argue to combine the two security levels as one single level with four configurations. But in reality the security levels are not limited to just a high or low configuration. It is easy to see the increased complexity in Table 2.2, where three levels of IL and CL are used. To keep the allowed communication routes simple and comprehensible, I have therefore chosen to keep the IL and CL separated. The IL and CL do not affect each other, but they affect the overall information flow between two tasks, i.e. a restriction in the confidentiality flow will not make any restrictions to the integrity flow and vice versa.

**Table 2.2:** A more complex model than Table 2.1, where  $\tau_3$  can only send messages to other tasks with the same configuration, while the configuration of  $\tau_7$  allows it to send messages to every other task without regard to their configuration.

| $	au_i$ | $IL(\tau_i)$ | $CL(\tau_i)$ | $	au_i 	o \mathcal{V}_j$                                                      |

|---------|--------------|--------------|-------------------------------------------------------------------------------|

| $	au_1$ | 1            | 1            | $\tau_1 \to \{\tau_1, \tau_2, \tau_3\}$                                       |

| $	au_2$ | 1            | 2            | $\tau_2 \to \{\tau_2, \tau_3\}$                                               |

| $	au_3$ | 1            | 3            | $\tau_3 \to \{\tau_3\}$                                                       |

| $	au_4$ | 2            | 1            | $	au_4 \to \{	au_1, 	au_2, 	au_3, 	au_4, 	au_5, 	au_6\}$                      |

| $	au_5$ | 2            | 2            | $\tau_5 \to \{\tau_2, \tau_3, \tau_4, \tau_5\}$                               |

| $	au_6$ | 2            | 3            | $\tau_6 \to \{\tau_3, \tau_6\}$                                               |

| $	au_7$ | 3            | 1            | $	au_7 \to \{	au_1, 	au_2, 	au_3, 	au_4, 	au_5, 	au_6, 	au_7, 	au_8, 	au_9\}$ |

| $	au_8$ | 3            | 2            | $	au_8 \to \{	au_2, 	au_3, 	au_5, 	au_6, 	au_8, 	au_9\}$                      |

| $	au_9$ | 3            | 3            | $\tau_9 \to \{\tau_3, \tau_6, \tau_9\}$                                       |

Table 2.3: ISO/DIS 26262 SIL decomposition scheme [TSP13]. Shows the possible decomposition of a SIL.

| $\operatorname{SIL}$ | Can be decomposed as                         |

|----------------------|----------------------------------------------|

| SIL 4                | SIL 4 or SIL 3 + SIL 1 or SIL 2 + SIL 2      |

| SIL $3$              | SIL 3 or SIL 2 + SIL 1                       |

| SIL $2$              | ${ m SIL}~2~{ m or}~{ m SIL}~1~+~{ m SIL}~1$ |

| SIL $1$              | SIL 1                                        |

#### 2.3.1 Safety Level

Industrial standards as the Safety Integrity Level (SIL) used to dictate the development process and the certification procedure of safety related functions [TSP13]. SIL are operating with four levels, with SIL 1 as the lowest level and SIL 4 as the highest level. The higher the level, the lower the tolerable hazard rate, i.e. the SIL can be associated with the tolerable hazard rate [LRNT06]. There is a SIL 0, but it is assigned to non-critical tasks and are not covered by the standards [TSP13]. I will use the notation IL instead of SIL, as SIL refer to safety and this thesis operates with both safety integrity and security integrity, i.e. IL covers both safety and security.

A high IL ensures a high level of safety, but it also cost time and money to develop high IL and get it certified. To circumvent the high cost of a task with a high IL, the task can be decomposed into two redundant tasks with lower ILs in the same way SIL is decomposed, see Table 2.3 [TSP13]. A decomposed IL would not affect the CL, i.e. the two new decomposed tasks will inherit the original CL. By decomposing a task, the number of tasks in the system increases.

This can potentially reduce the schedulability, due to the extra tasks that have to be placed in the schedule table.

An IL can always be elevated to a higher IL, if it is not at the highest level yet. A high IL costs more, but can be necessary to obtain a schedulable solution. Two tasks of different IL (or CL) cannot share a partition, and tasks with low IL may need elevation in order share a partition with task with higher IL.

#### 2.3.2 Security Level

There are no standards for the number of levels in CL. Various levels of confidentiality can be applied to a system. A common toy-example is using three levels: Unclassified (UC), Secret (S) and Top-Secret (TS). I will use these three levels in the further description of CL in this paper. Comparable, but not equivalent to the concept of SIL for safety, the security has a concept known as Evaluation Assurance Level (EAL) [LRNT06]. The EAL is a standard for certifying security functions considering all the security properties, i.e. including integrity and confidentiality. There are seven EAL levels and they correspond to assurance levels [CC12]: (1) Functionally tested, (2) Structurally tested, (3) Methodically tested and checked, (4) Methodically designed, tested and reviewed, (5) Semiformally designed and tested, (6) Semiformally verified design and tested and (7) Formally verified design and tested.

Where a safety function can be certified to a SIL, the security function can be certified at an EAL, i.e. a particular level in EAL only tells us how much a security function has been tested and how much we can trust it to be as secure as it claims, but not how secure the function really is. Therefore I will not use the EAL as a guaranty for the security in the CL. Another difference between IL and CL is that a CL cannot be decomposed nor elevated as the IL.

#### 2.4 Application Examples

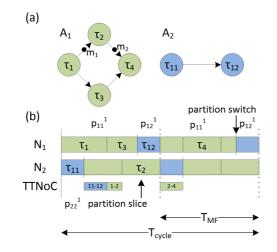

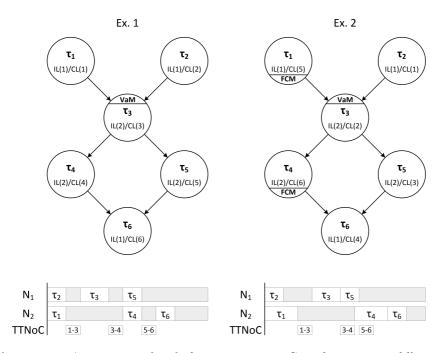

The application model is illustrated in Figure 2.1. Here are shown two application subsystems  $\mathcal{A}_1$  and  $\mathcal{A}_2$  and their dependencies. Tasks communicate by sending messages along the edges. A message has exactly one sender, but can have several receivers. In (a)  $\tau_1$  sends messages to  $\tau_2$  and  $\tau_3$ . The message from  $\tau_1$  can be a multicast message from one sender to two receiving tasks. It can also be two different messages sent at different time from one sender to one receiver.

Figure 2.1: The graph in (a) shows two flows. A flow in  $\mathcal{A}_1$  from  $\tau_1$  to  $\tau_4$  and a flow in  $\mathcal{A}_2$  from  $\tau_{11}$  to  $\tau_{12}$ . (b) shows the tasks from (a) scheduled to partition slices and mapped on two PE.

$\tau_4$  receives two individual messages at different point in time. A task that take input from other tasks cannot execute before all inputs are received.

The mapping assign one task  $\tau_i$  to one partition slice  $p_{ij}^k$ . The schedule is shown in (b) with two PEs  $N_1$  and  $N_2$ .  $\tau_1$ ,  $\tau_3$ ,  $\tau_4$  and  $\tau_{12}$  are placed on  $N_1$  while  $\tau_2$  and  $\tau_{11}$  are placed on  $N_2$ . Unused partition slices are greyed out. The message from  $\tau_1$  to  $\tau_2$  and  $\tau_3$  is multicast at the same timeslot, but as  $\tau_1$  and  $\tau_3$  are placed on same PE, only the message to  $\tau_2$  is going through the TTNoC.  $\tau_4$  receives input from  $\tau_2$  and  $\tau_3$ . As  $\tau_3$  shares the PE with  $\tau_4$ , only the message from  $\tau_2$  is going through the TTNoC. If the three tasks was placed on three different PEs,  $\tau_2$  and  $\tau_3$  would need two different timeslots to send their messages to  $\tau_4$ .  $\tau_4$ cannot start its execution before it has received all input messages.

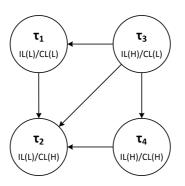

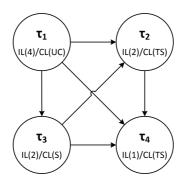

The possible information flows outlined in Table 2.1 is illustrated as a graph in Figure 2.2. It is easy to see that the configuration of high integrity level and low confidentiality level in  $\tau_3$  has a free outgoing flow, while it cannot receive information from other configurations. In contrast, the configuration in  $\tau_2$  can only receive information, but not send to other configurations (other than equal configurations - not pictured).

Figure 2.2: Illustration of the possible flow between tasks with different IL and CL configurations introduced in Table 2.1. It is easy to see that information from  $\tau_3$  can flow free, while information from  $\tau_2$  has a restricted flow.

### Chapter 3

## Architecture Model

I have chosen the ACROSS MPSoC architecture to support the application model. The ACROSS MPSoC is designed as a combined safety and security architecture built on a MPSoC platform [WM12]. The architecture consists of multiple components connected together by a TTNoC. The term "component" (or " $\mu$ Component" in some articles) is used in various articles, e.g. [AFHOT06], [BDRS08], [ESOHK08] and [WESK10], to describe the part of the architecture providing the application specific services. The component consist of a *host* and the *TISS*, as I will discuss later in Section 3.1.1 and 3.1.2. None of the articles have a deep description of the application model and I interpret the use of the term "component" in the articles, as a label to talk about components in an abstract way. If we remove the label "component" we could talk about the host communicating with other hosts through the TTNoC via the TISS. I will use the term "component" in its abstract form in this thesis and consider the host of the component to be the application task.

The ACROSS MPSoC architecture is a *Multiple Independent Levels of Security* (MILS) system [AFHOT06], [BDRS08], [WESK10], where the fundamental idea is to separate subsystems. The concept of separation was introduced by Rushby[Rus81] in 1981 and ensured by a trusted separation kernel. The architecture consists of three parts: the hardware layer with the separation kernel, a trusted part and an untrusted part. The trusted part ensures the core services and cannot be changed by the application specific services. The untrusted part performs the application specific services and can incorporate middleware to relax the strict information flow.

The security in the ACROSS MPSoC architecture only covers the integrity, with a limited aspect of confidentiality. The architecture's limitation is that it will only support confidentiality in form of cryptographic algorithms, but does not support an upward information flow, i.e. the information flow would be downward (integrity) and thereby excludes an upward flow (confidentiality). An upward flow was described in [WESK10], but the downward flow was neglected.

#### 3.1 The Architecture

The lowest layer in the architecture is the hardware and the Seperation Kernel (SK) as mentioned in section 1.3. The hardware is out of the scope of this thesis and will not be covered. The SK is the core concept in the ACROSS MPSoC architecture and isolates processes in separate partitions on a shared processor [WESK10], [Rus81]. The partitioning, which is both spatial and temporal, enforces (1) data separation, (2) the information flow by using interpartition communication, (3) sanitisation by cleaning any shared resources and (4) damage limitation, as a fault in one partition would not affect other partitions [AFHOT06].

Each component is assigned to a partition slice and has assigned exactly one level of safety and exactly one level of security. The partition slices are scheduled on PEs using *Static-Cyclic Scheduling* (SCS). In contrast [WESK10] writes: "Each partition is mapped to exactly one component and each component hosts at most one partition." By doing so, a task in a component is separated from other tasks and a failure in one partition will not propagate to another partition. The information flow is also ensured, as information cannot flow outside the partition from one task to another. But the scheduling would be hard to optimise, if partitions cannot be shared and I choose to apply the tasks to partition slices instead of partitions. There are some precautions to consider. Information can flow inside a partition and tasks sharing a partition must therefore be configured with the same IL and CL. Some tasks may not share partitions and is connected through an edge in  $\Pi$  as described in Section 2.1.

To function it is required that the SK is always available and invoked, tamperproof, non-bypassable and free of design faults. To ensure that, the SK must be easy to certify and is thereby kept as small and simple as possible. The SK is the *Trusted Computing Base* (TCB) of the system. Lampson [LABW92] is often quoted for describing the TCB as a "small amount of software and hardware that

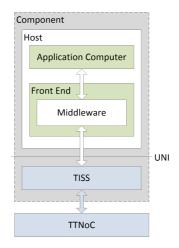

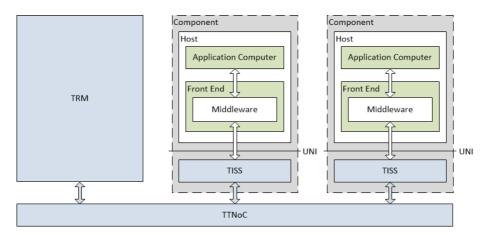

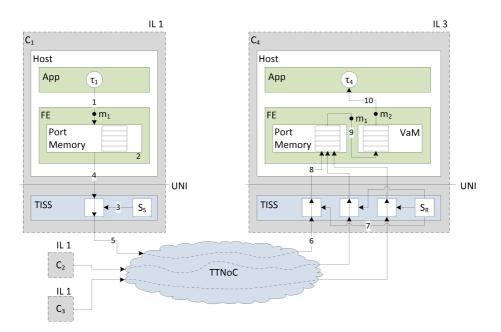

Figure 3.1: The architecture of a component. It consists of two architecture elements: the TISS which also is part of the TSS and the host in which the application specific services are placed. Via the UNI have the host a transparent interface through the TSS to other hosts.

security depends on and that we distinguish from a much larger amount that can misbehave without affecting security."

#### 3.1.1 The Trusted Architectural Layer

The application specific services are carried out by architectural elements called *components* (or  $\mu$ *Components*) as introduced in Section 3, and are connected through a *Time-Triggered Network-on-a-Chip* (TTNoC). Figure 3.1 shows the component and its elements.

The TTNoC is a part of a *Trusted Subsystem* (TSS). TSS is composed of: the TTNoC, a *Trusted Interface Subsystem* (TISS) and the *Trusted Resource Manager* (TRM). Together they form a black box for the components and is assumed to be free from design faults. All communication is carried out by the TSS, transparent to the component. By using the TTNoC as the internal communication network provides us with some fundamental security functionalities [WESK10] such as: data isolation, a controlled information flow and damage limitation. For further descriptions on how the TTNoC works, I recommend reading [Sch07].

The message routes in the TSS are called Encapsulated Communication Chan-

nels and are unidirectional communication channels with one sender and one or several receivers, which transport the message in a priori known point in time. The endpoints of the encapsulated communication channels are called *ports* and are located in the TISS. Ports leading out of the SoC to another SoC are called *gateways*. Due to security reasons communication through gateways is encrypted, as specified later on in Section 3.1.2.2, and gateways are therefore limited to special IO-components, i.e. ordinary components cannot contain gateways and can thereby not connect to an external network.

The routes and ports are managed by the TRM according to a *Time-Division* Multiple Access (TDMA) scheme [OH11]. Only the TRM can re-/configure the routes and ports, and acts as a guardian for reconfiguration. In earlier articles the TRM is often called Trusted Network Authority (TNA) and is often co-operating with a *Resource Management Authority* (RMA), where the RMA reconfigures the communication and the TNA guards the activities of the RMA [PPES09]. In ACROSS MPSoC the TNA and RMA are combined into TRM. A component cannot change the encapsulated communication channels (this is exclusive managed by the TRM), but a component can suggest a reconfiguration to the TRM. To manage and reconfigure the encapsulated communication channels, the TRM knows the TDMA, the components configuration, the components safety and security level and the configuration of the TTNoC. The TRM makes sure that no safety or security policy is violated during a reconfiguration. The TRM has the communication channels under constant surveillance, preventing unauthorised alternations. The TRM is also checking the identity of the component and allows only authorised components to communicate. With TTNoC, TRM and TISS combined in the TSS, the TSS ensures a time-triggered communication, a common time among the system and integrated resource management.

The TISS forms one part of a component, as shown in Figure 3.1, and act as a guardian, by only accepting messages to be sent or received according to the TDMA. This prevents a faulty component from being a "babbling idiot"<sup>1</sup>. Even though the TISS is placed in the component, the TISS can only be reconfigured by the TRM. The other part of a component is called the *host*, see Figure 3.1. Where the TISS are part of the TSS and certified as the highest level of the system, the host is part of the untrusted area and must be individual certified. The TISS provides a *Uniform Network Interface* (UNI) to the host, so when a task in the host want to communicate with other tasks it connects to the UNI and the transportation of the message(s) are transparent to the task.

<sup>&</sup>lt;sup>1</sup>A babbling idiot is a faulting node, flooding the communication network and taking up resources. It can potentially prevent correct functional nodes in receiving and sending messages or making the node repeatedly executing its application service inappropriately many times.

#### 3.1.2 The Top-Layer

The designer of tasks is restricted from altering the TSS, but has access to the host which is composed by an *Application Computer* (AC) and by *Front End* (FE). As described in the introduction to Section 3, I consider the host to be the application task. A task contains therefore both the AC and the FE. The AC performs the application specific services and the FE services as an extension to the communication services, i.e. the application specific parts of the task are performed by the AC in the architecture, while parts of the task extending the communication service are performed by the architectural FE.

*Middleware* services are extensions in the FE, which provide high level communication services to e.g. circumvent the unidirectional flow. The partitioning of tasks will therefore include both the application specific services and the serviced performed by the middleware in one partition slice. That also means that the WCET for a task increases by using middleware. Even though I consider the host as a task when mapping tasks to partition slices, I will refer to tasks as just the AC. The reason for this is to better explain the behaviour of the system and focus on the application specific part of the task.

A dual-ported memory denoted as *Port Memory* [PPES09] is also located in the FE. Messages from the task have to be written into the Port Memory and forwarded by the TISS onto the TTNoC at an a priori known point in time. A component is applied the same IL and CL configuration as the tasks, with the same restrictions, as described in Section 2.3.

#### 3.1.2.1 Middleware

Middleware is used to provide an extra layer to the communication services provided by TSS and does not affect the application. The extra layer is used to relax the rigid information flow (downward for integrity and upward for confidentiality), by allowing a reverse flow, i.e. middleware allows us to create an upward integrity flow and a downward confidentiality flow.

As discussed in Section 1.2, we need to be able to upgrade information. E.g. three redundant braking sensors in a car has usually a low IL, but have great consequences if not working properly. In a safety integrity manner a sensor is "likely" to fail to output a value. In the perspective of security integrity, the value produced may not be accurate, it might even be a false measurement or could be produced by a deliberate action caused by a malicious intruder.

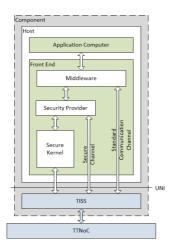

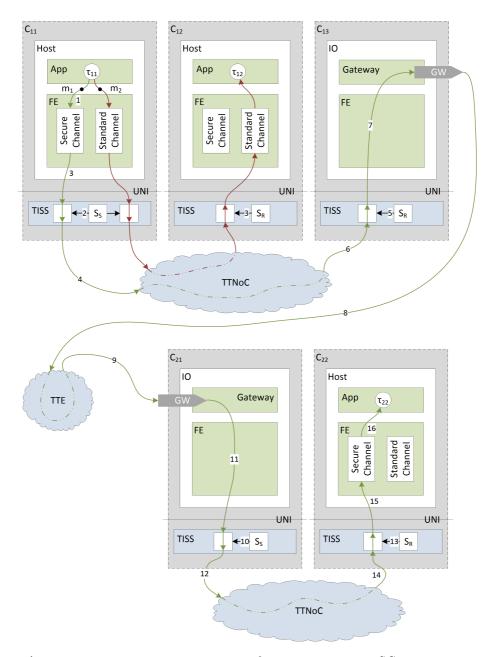

Figure 3.2: Here the SC is implemented along with a piece of middleware. Both the SC and the middelware are placed in the FE, such that SC is placed between the network and the middleware. The middelware is placed with SC and AC on each side.

To ensure a trustworthy measurement with a higher IL, we need to gather information of several redundant or diverse sources. A *Validation Middleware* (VaM) [WM12] gathers the redundant low IL input and runs a voting algorithm among the values to output a single trustworthy high IL value. The VaM is located at the receiving component and certified at the same IL as the host component.

The confidentiality flow can be circumvent by a *Flow Control Middleware* (FCM) [WESK10]. Not all information in a component with a high CL may be sensitive and can apply to a lower CL as well. As an example, only the information to identify a person on his patient journal is sensitive, while the diagnose and treatment are not of a sensitive nature and rather useless without the identification of the patient. The FCM provides a filter to remove sensitive confidential information and lets insensitive information through. In this way a downward information flow can be accepted. The FCM are located at the sending component, allowing it to send information with a lower CL than the original CL of the host component.

#### 3.1.2.2 Secure Channel

A Secure Channel (SC) [IW13] is a common design pattern that ensures the secrecy in the information flow to external communication. The message is sent through the TTNoC to a special IO-component with a gateway to the external network and SoC. The SC ensures the secrecy if the message is eavesdropped and is placed in the FE and is a piece of middleware. If other middleware services are assigned to the component, SC is placed between the middleware and the TISS as shown in Figure 3.2.

A Secure Kernel manages and generates the cryptographic keys used by SC. The key generation demands heavy computation, which could be a problem in a resource limited MPSoC. For that reason it is hardware implemented to ensure faster and resource-saving computation. The Secure Kernel must ensure that a key is ready to use, at the point in time a message needs it. The Secure Kernel is not to be confused with the Separation Kernel (SK) of the ACROSS MPSoC architecture. It is not part of the TSS, but is the TCB for the SC.

A Secure Provider executes the encryption and decryption and provides the task (or middleware if implemented) with a transparent channel with security properties. The architecture also provides a standard communication channel to bypass the SC for on-chip communication where encryption is not needed.

The SC encrypts information going through the TTNoC, but is used for off-chip communication to ensure confidentiality on an unsecured external network. A special IO-component with gateways to the external network, e.g. *TTEthernet*, must be used for this case. Then messages must travel through the TTNoC, to the IO-component, further to the external network and arrive at the destination SoC. More detail description is given in description of the behaviour in Section 3.5.2.

The cryptographic algorithm used must be implementable in hardware. A hardware implementation ensures fast computations, offloads the resources and ensures better security, as hardware is harder to attack than pure software. A simple XOR encryption<sup>2</sup> is light and easy to implemented in hardware. It is fast and messages will be encrypted in the same clock cycle [WES08]. Though, XOR offers not much protection, as it is vulnerable to known-plaintext attacks<sup>3</sup>. AES is a strong symmetric algorithm, provides a strong protection and can be implemented in hardware as well [HAHH06]. The downside of encryption, and

$<sup>^{2}</sup>$ XOR encrypt a binary plain-text by xor it with a repeating binary key, e.g. by XOR the key 1010 on the plaintext 1101 0011, we get the ciphertext 0111 1001.

<sup>&</sup>lt;sup>3</sup>In known-plaintext attacks the intruder knows the ciphertext and some part of the plaintext. He can then reverse the XOR and get the key.

special strong encryption, is the increased computation time. By outsourcing the key creation to special hardware components with dedicated partitions and by ensure that a key will be available at the point in time a message has to be encrypted. In the software component, the message only has to be encrypted and sent (without concern of key generation or key management), and the increased computation time would be minimal. So even though an increased WCET must be taken into account, the limitation of a hard real-time behaviour will not be affected. Due to the strong protection of the AES algorithm and the minimal increasing in the WCET, as the keys are created and managed by hardware, I recommend AES for the encryption in the SC.

#### 3.1.2.3 Crypto Component

If long lasting encryption is needed, a special *Crypto Component* can be implemented in the design as a supplement or addition to the SC. The Crypto Component will provide both the encryption and decryption and is designed as an ordinary component with TISS and host. The cryptographic services are carried out in the application computer. Where the SC only encrypt the message in the transport and decrypt the message at end-destination, a Crypto Component can apply cryptographic algorithms to information that is going to be stored in other tasks, i.e. a low CL task can obtain encrypted information without getting knowledge of its content.

To encrypt information, the Crypto Component receives a message from another task. It encrypts the message and forwards the encrypted message to a receiving task. The receiving task can be the same task that requested the encryption. The same procedure applies for decryption. After encryption the information are applied the lowest possible CL, regarding the original CL, and the IL is remain unchanged. It is important to note that the original CL and IL of the information must be restored after decryption. The CL at the receiving task must be higher or at the same level as the original CL of the information.

The Crypto Component can be designed similar to the SC with special hardware components to compute and manage the cryptographic keys. The encryption and decryption will take longer time than the SC, as the Crypto Component is a separate component and must have its own timeslot in the schedule.

Figure 3.3: A simple version of the ACROSS MPSoC architecture. The two components is connected through the TTNoC network and the TRM are managing the communication routes. The TSS consisting of the TRM, the TTNoC and the TISS are coloured blue.

### **3.2** Architecture Examples

I will give tree simple examples of the architecture, the validation middleware (VaM) and the partitioning by a system of mixed criticality.

#### 3.2.1 The ACROSS MPSoC Architecture

Figure 3.3 shows the ACROSS MPSoC architecture with two components. The figure is colour coded for easy recognition and the elements of the TSS are shown with blue colour. The components are of a gray colour and with a dashed frame. The hosts are in white and contains of AC and FE. Middleware are placed in both FEs. The task in the components communicates via the TTNoC by sending messages. The UNI will provide a transparent interface through the TSS. The component cannot change the time schedule in the TISS, but can suggest the TRM to reconfigure the time schedule and routes. If the change does not conflict with the safety and security restrictions, the TRM can change the configuration of the TISS. The middleware can be implemented in the FE and contain additional security functions for sending or receiving messages and function as an extension to the TISS. The FE also provides a *Port Memory* which houses the ports of the encapsulated communication channels [PPES09]. The port memory is not pictured.

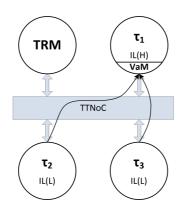

Figure 3.4: The VaM is placed together with a task  $\tau_1$  with a high IL. The VaM require input from redundant or diverse tasks,  $\tau_2$  and  $\tau_3$ , with lower IL. A voting algorithm among the input in the VaM produces a high IL output to  $\tau_1$ .

#### 3.2.2 Simple VaM Example

Figure 3.4 illustrates a simplified version of the system containing two redundant task,  $\tau_2$  and  $\tau_3$ , with a low integrity level, sending messages to the high level task  $\tau_1$ . To allow an upward integrity flow a VaM is placed in  $\tau_1$  to collect the redundant low level input. The VaM runs a voting algorithm among the two input and produces a output with a high level value to  $\tau_1$ .

#### 3.2.3 The Partitioning

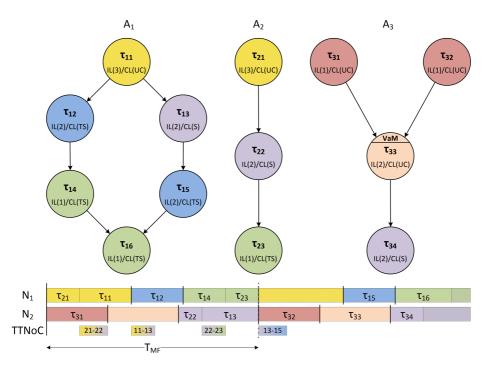

An example of partitioning of a system of three applications,  $\mathcal{A}_1$ ,  $\mathcal{A}_2$  and  $\mathcal{A}_3$ , with 13 tasks is illustrated in Figure 3.5. The tasks are mapped to on two PEs;  $N_1$  and  $N_2$  and are colour coded by their IL and CL configuration (see Table 3.1), e.g.  $\tau_{13}$ ,  $\tau_{22}$  and  $\tau_{34}$  have the same purple colour.

As discussed in Section 3.1, tasks of same configuration, i.e. same colour in this figure, can be placed into the same partition. This is done by  $\tau_{13}$  and  $\tau_{22}$ , and  $\tau_{14}$  and  $\tau_{23}$ . An exception is the two redundant tasks  $\tau_{31}$  and  $\tau_{32}$ , as they share an edge in the protection requirement graph, II. The middleware is a part of the task and  $\tau_{33}$  contains therefore both the application specific services and the VaM. Parts with gray shading are not occupied by a partition slice and remain unused. Tasks cannot start until they have received all its input information, e.g.  $\tau_{16}$  need the information from  $\tau_{14}$  and  $\tau_{15}$  before it can start. A task output

| $IL(\tau_i)$ | $CL(\tau_i)$ | Colour                 |

|--------------|--------------|------------------------|

| 1            | UC           | Red                    |

| 2            | UC           | Salmon                 |

| 3            | UC           | Yellow                 |

| 2            | $\mathbf{S}$ | Purple                 |

| 1            | TS           | $\operatorname{Green}$ |

| 2            | TS           | Blue                   |

**Figure 3.5:** Partitioning of three subsystems;  $\mathcal{A}_1$ ,  $\mathcal{A}_2$  and  $\mathcal{A}_3$ . The partitioning is not optimised, but reached the deadline before the period ends. The colouring indicated the same configurations of IL and CL and tasks of same configuration can share a partition. An exception is  $\tau_{31}$  and  $\tau_{31}$ , which has the same configuration, but are redundant tasks and prohibited to spare partitions.  $\tau_{31}$  and  $\tau_{31}$  share an edge in II. The messages is colour coded by the configuration of the sending and receiving task for easy visual identifying.

Table 3.1: The colour coding of the tasks in Figure 3.5.

information after it is terminated.

Both the downward integrity flow and the upright confidentiality flow are met. In  $\mathcal{A}_2$  the information flow is clear and information flows from  $\tau_{21}$  with a high IL and a low CL to  $\tau_{23}$  with a low IL and high CL. In  $\mathcal{A}_3$ , the two redundant tasks  $\tau_{31}$  and  $\tau_{32}$  have a upward integrity flow to  $\tau_{33}$ . A VaM is implemented in  $\tau_{33}$  and runs a voting algorithm among the two input and produce an output of a higher IL.

### 3.3 Safety Mechanism

The ACROSS MPSoC architecture is developed to support integrity and to be easily certified. A lot of mechanisms are build into the system to ensure integrity. I have made no extension to the model to increase safety.

#### 3.3.1 Separation and Partitioning

A safety system must guarantee the safety ability through validation. Without certification the system cannot claim to be safe. In complex system the certification can be a hassle. The separation of subsystems [Rus81] makes the certifications easier, as the subsystems can be certified separate and not as one. The separation also enforces the safety in the partition layer. The SK separates the partitions both in the spatial and temporal domain. This prevent information in one partition from flowing unintended to another partition and thereby enforcing the information flow, as discussed later on in Section 3.3.4.

The partitions are sanitised by the SK. This means that no old information would be left in the partition to be revealed from one task to another, i.e. information cannot flow from one task to another, just because they are using the same partition at different time.

Partitioning also provides damage limitation, so fault in one partition will not affect other partitions. The safety aspect of this is immediate, as a fault in e.g. a sensor would not affect the safety of the system other than the missing or faulty output from the sensor. As it is possible for tasks of same configuration to share a partition and thereby be affected of the same damage in a partition, it is important for the designer to consider if some tasks should be prohibited to share a partition. In Section 3.1 there is a discussion about the requirements for separation.

### 3.3.2 Redundancy / Diversity

Allowing a flow from low integrity tasks to high integrity task, is the premise for including redundant tasks. Redundancy enforces safety in two ways: (1) it makes the system fault-tolerant, as if one redundant device fails, the other device(s) would probably not fail of the same reason. For that reason it is important redundant tasks does not share a partition. (2) the redundancy relaxes the rigid information flow, as redundant tasks can be validated to a higher level and redundancy makes the system easier and cheaper to certify, because redundant tasks have a lower level than one single task. Redundancy is often carried out by hardware components. Diversity, where the same functionality is computed using different algorithms and likely by different development teams, is often preferred in software. This minimises the risk of a software bug in one task to occur in another diverse task.

#### 3.3.3 Time-Triggered Architecture

The ACROSS MPSoC is a *Time-Triggered Architecture* (TTA) and ensures reliable and trustworthy hard real-time communication. It guaranties a sending slot to all tasks in a cyclic period and at an a priori known time. Only in that timeslot a given task can send its message. At the same time, the receiving task knows it has to receive a message. This prevent a flood of information in the system that could potentiality make the system to malfunction in a non-safety manner. The TTA enforces the properties of the SK and can be considered as a realisation of the SK [WESK10].

#### 3.3.4 Trusted Subsystem

The TSS ensures safety by transparently manage the communication between the tasks. A task cannot change the TSS but has to suggest a reconfiguration. Only if the safety is still guaranteed, the change will apply. This makes the TSS quite robust for unauthorized changes that could lower the safety of the system.

The encapsulated communication channels are unidirectional channels with a single sender and one or more receivers. The channels with its endpoints and it temporal presence, are known a priori and constantly checked by the TRM [WESK10]. The encapsulated communication channels and TRM are both part of the TSS. The encapsulation guaranties the information flow, i.e. there can be no flow from a low IL task to a high IL task (unless it runs through a validation

middleware). This prevents unsafe elements to be unintended promoted.

### 3.4 Security Mechanism