# A Time-Composable Operating System for the Patmos Processor

Marco Ziccardi

Kongens Lyngby 2013 M.Sc.-2013-73

Technical University of Denmark Applied Mathematics and Computer Science Matematiktorvet, building 303B, DK-2800 Kongens Lyngby, Denmark Phone +45 4525 3031, Fax +45 4588 1399 compute@compute.dtu.dk www.compute.dtu.dk M.Sc.-2013-73

# Summary

The aim of this thesis is to port the TiCOS operating system to the Patmos processor. TiCOS is a light-weight operating system developed to obtain composability and analyzability and targeting single-processors. Patmos is a time-predictable single-processor developed in the framework of the T-CREST project. The aim of the T-CREST project is to develop a time-predictable multi-processor able to meet both the requirements of safety and processing capacity for modern real-time and embedded systems. <u>ii</u>\_\_\_\_\_

# Preface

This thesis was carried out at the department of Applied Mathematics and Computer Science, at the Technical University of Denmark, in fulfilment of the requirements for acquiring an M.Sc. in Informatics.

The thesis was developed in the framework of the Time-Predictable Multi-Core Architecture for Embedded Systems (T-CREST) project, a Specific Targeted Research Project (STREP) of the European Union's 7th Framework Programme, whose goal is the creation of a time-predictable multi-core architecture for embedded systems. In order to do so the T-CREST group is developing, amongst other things, the processor, the Network on Chip (NoC) and the compiler. The T-CREST project is a collaboration of many industrial and research organizations and the architecture, as a research project, is continuously evolving. The research and dynamic nature of T-CREST architecture made of my master thesis project a challenging and meaningful experience. On the other hand my thesis aided in identifying industrial requirements that the architecture was missing, which caused me to further my understanding of the T-CREST architecture itself, extending it with the needed features.

The thesis consists of the adaptation of an existing time-composable operating system for the T-CREST processor (Patmos). In order to make this possible the need for extensions to the processor architecture was identified and the relevant features implemented in the software simulator.

Lyngby, 31-July-2013

Morro Wiccordi

Marco Ziccardi

iv

# Acknowledgements

I would like to thank my supervisor Martin Schoeberl for driving my project work in the right direction. I would also like to thank all the T-CREST group at the Technical University of Denmark and Stefan Hepp from the Vienna University of Technology, special thanks go to Florian Brandner for helping me every time I needed. Finally, I would like to thank Andrea Baldovin, Enrico Mezzetti and Tullio Vardanega for the endless amount of valuable advices.

# Contents

| Summary  |        |                             |   |  |  |  |

|----------|--------|-----------------------------|---|--|--|--|

| Pı       | reface | e ii                        | i |  |  |  |

| A        | cknov  | vledgements                 | V |  |  |  |

| 1        | Intr   | oduction                    | L |  |  |  |

|          | 1.1    | Real-time Systems           | - |  |  |  |

|          |        | 1.1.1 Task Models           | 3 |  |  |  |

|          | 1.2    | Timing Analysis             | 1 |  |  |  |

|          | 1.3    | Time composability          | 5 |  |  |  |

|          | 1.4    | Real-time Operating Systems | 5 |  |  |  |

|          |        | 1.4.1 Memory Management     | 7 |  |  |  |

|          |        | 1.4.2 Scheduling Algorithms | 3 |  |  |  |

|          |        | 1.4.3 PikeOS                | ) |  |  |  |

|          |        | 1.4.4 INTEGRITY 11          | L |  |  |  |

|          |        | 1.4.5 LynxOS-178 12         | 2 |  |  |  |

|          |        | 1.4.6 CompOS                | 2 |  |  |  |

|          |        | 1.4.7 TiCOS 14              | 1 |  |  |  |

|          | 1.5    | The T-CREST Project         | 1 |  |  |  |

|          | 1.6    | Thesis Structure            | 5 |  |  |  |

| <b>2</b> | The    | Patmos Processor 17         | 7 |  |  |  |

|          | 2.1    | Memory                      | 3 |  |  |  |

|          |        | 2.1.1 Method Cache          | 3 |  |  |  |

|          |        | 2.1.2 Data Cache            | ) |  |  |  |

|          |        | 2.1.3 Stack Cache           | ) |  |  |  |

|          |        | 2.1.4 Data Scratchpad       | 1 |  |  |  |

|          | 2.2    | Registers                   | 1 |  |  |  |

|   | 2.3 | Patmos ISA (Instruction Set Architecture)                                                                                                 |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.3.1 Binary Arithmetic                                                                                                                   |

|   |     | 2.3.2 Multiply                                                                                                                            |

|   |     | 2.3.3 Compare                                                                                                                             |

|   |     | 2.3.4 Predicate                                                                                                                           |

|   |     | 2.3.5 NOP                                                                                                                                 |

|   |     | 2.3.6 Wait                                                                                                                                |

|   |     | 2.3.7 Move To/From Special                                                                                                                |

|   |     | 2.3.8 Load/Store Typed                                                                                                                    |

|   |     | 2.3.9 Stack control                                                                                                                       |

|   |     | 2.3.10 Call and Branch                                                                                                                    |

|   |     | 2.3.11 Call and Branch Indirect                                                                                                           |

|   |     | 2.3.12 Return                                                                                                                             |

| 3 | The | Operating System 33                                                                                                                       |

|   | 3.1 | Гhe Kernel Layer                                                                                                                          |

|   | 3.2 | ARINC653 Entities                                                                                                                         |

|   |     | 3.2.1 Partitions and Processes                                                                                                            |

|   |     | $3.2.2  \text{Events}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   |

|   |     | $3.2.3  \text{Semaphores}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                               |

|   |     | 3.2.4 Blackboards                                                                                                                         |

|   |     | $3.2.5  \text{Buffers} \dots \dots$ |

|   |     | 3.2.6 Sampling and Queueing Ports                                                                                                         |

|   | 3.3 | The Library Layer                                                                                                                         |

|   |     | 3.3.1 Core Library                                                                                                                        |

|   |     | 3.3.2 Middleware Library                                                                                                                  |

|   |     | 3.3.3 ARINC Library                                                                                                                       |

|   | 3.4 | ΓiCOS Time-composability 4ξ                                                                                                               |

|   |     | 3.4.1 Time Management                                                                                                                     |

|   |     | 3.4.2 Scheduling                                                                                                                          |

|   |     | 3.4.3 IO Communication                                                                                                                    |

|   | 3.5 | Build Chain                                                                                                                               |

|   |     | 3.5.1 Kernel Compilation                                                                                                                  |

|   |     | 3.5.2 Partitions Compilation                                                                                                              |

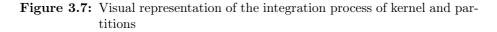

|   |     | 3.5.3 Integration of Kernel and Partitions                                                                                                |

| 4 | Pro | essor Extensions 51                                                                                                                       |

|   | 4.1 | Interrupts $\dots \dots \dots$            |

|   |     | 4.1.1 Simulator Implementation                                                                                                            |

|   | 4.2 | Stack Cache Manipulation                                                                                                                  |

|   | 4.3 | $Memory Protection \dots \dots$     |

|   | 4.4 | Explicit Supervisor Mode and Cache Invalidation 60                                                                                        |

#### CONTENTS

| <b>5</b>     | $\operatorname{TiC}$ | OS Extensions                            | 63  |  |  |  |  |

|--------------|----------------------|------------------------------------------|-----|--|--|--|--|

|              | 5.1                  | Architectural Changes                    | 64  |  |  |  |  |

|              |                      | 5.1.1 Clock                              | 64  |  |  |  |  |

|              |                      | 5.1.2 Thread's Context                   | 66  |  |  |  |  |

|              |                      | 5.1.3 Memory Management                  | 68  |  |  |  |  |

|              | 5.2                  | Core Changes                             | 71  |  |  |  |  |

|              |                      | 5.2.1 Bootloader                         | 71  |  |  |  |  |

|              | 5.3                  | Library Changes                          | 77  |  |  |  |  |

|              |                      | 5.3.1 System Calls Implementation        | 77  |  |  |  |  |

|              | 5.4                  | Context Switch                           | 81  |  |  |  |  |

|              |                      | 5.4.1 Interrupt-driven Context Switching | 81  |  |  |  |  |

|              |                      | 5.4.2 Explicit Context Switching         | 88  |  |  |  |  |

| 6            | Sou                  | rce Code Access                          | 91  |  |  |  |  |

|              | 6.1                  | Running an Example                       | 92  |  |  |  |  |

| 7            | Con                  | clusions                                 | 95  |  |  |  |  |

|              | 7.1                  | Personal Knowledge                       | 95  |  |  |  |  |

|              | 7.2                  | Main Contributions                       | 96  |  |  |  |  |

|              | 7.3                  | Suggested Future Works                   | 97  |  |  |  |  |

| $\mathbf{A}$ | Soft                 | ware Simulator of Patmos                 | 99  |  |  |  |  |

|              | A.1                  | Instruction Simulation                   | 01  |  |  |  |  |

|              | A.2                  | Memory and Cache Simulation              | .02 |  |  |  |  |

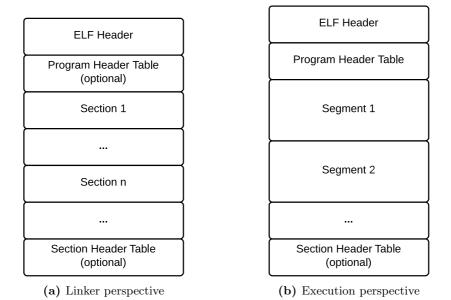

| в            | ELF                  | File Structure 1                         | 03  |  |  |  |  |

|              | B.1                  | File Structure                           | 03  |  |  |  |  |

|              |                      |                                          | 04  |  |  |  |  |

|              |                      | B.1.2 Program Header                     | 05  |  |  |  |  |

|              |                      | B.1.3 Section Header                     |     |  |  |  |  |

| Bi           | Bibliography 10      |                                          |     |  |  |  |  |

## CHAPTER 1

# Introduction

In this chapter we introduce some key aspects of Real-Time Systems (RTS), starting from the computational model. We then discuss *timing analysis* and Worst-Case Execution Time (WCET) calculation. After that we introduce *time-composability* and how important that property is. In Section 1.4 the role of a Real-Time Operating System (RTOS) is described and some examples are presented. In the end the T-CREST project and platform are briefly described.

### 1.1 Real-time Systems

A real-time system receives inputs and sends outputs to the hardware, working under strict constraints on its response time [Ben06]. Real-time systems (RTS) are almost everywhere in our everyday life, applications of real-time systems can be found in [Mal09]:

- *Industrial applications*: key industrial systems often require a RTS, for example process control and automation are usually RTS-managed

- Medical: a RTS is hidden behind almost all medical diagnostic machines

- *Peripherals*: devices like laser printers or digital cameras contain embedded real-time systems

- Automotive and Transportation: automotive assistant systems such as automated pedestrian detection are implemented through real-time systems. Likewise the safety system of a train is a RTS

- *Telecommunication applications*: real-time systems are used in modern cellular systems

- *Aerospace*: real-time systems in aerospace industry have to deal with the big amount of fresh data collected from the environment and the scarce downlink bandwidth

- Avionics: several systems on an aircraft perform real-time operations and have to be coordinated. Examples are the communication and the navigation systems

- $\bullet$  Defence

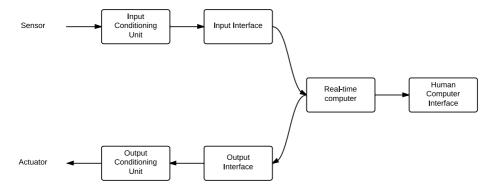

A simplified model for a RTS is shown in figure 1.1. A **sensor** has to convert environmental inputs to electrical signals while an **actuator** is a device that takes an electric signal and converts it to physical action on the environment. **Conditioning units** are responsible for translating the electric signal coming from a sensor to an electric signal that could be used by a computer and likewise they translate computer electric signal to something understandable by an actuator. An **interface unit** translates signals between the two talking ends (CPU and conditioning unit) and eventually takes care of buffering [Mal09].

Figure 1.1: A real-time system model (from [Mal09])

#### 1.1.1 Task Models

A real-time application can also be viewed as a *taskset*  $\tau$ , a static set of tasks [DB11]. Each real-time task is characterized by a set of attributes specifying its timing behaviour [Ben06]:

- *Release time*: time when the task is ready to be executed

- Worst case execution time  $C_i$

- Response time  $R_i$ : amount of time between the task release time and the end of its execution

- *Deadline*  $D_i$ : maximum allowed response time

In the literature two simple task models are mainly used [DB11]:

- Periodic task model [LL73]: tasks perform an ideally infinite sequence of invocations (*jobs*). Jobs arrival time is periodical: between two invocations always occurs the same amount of time, we call this amount period  $T_i$

- Sporadic task model [Mok83]: each task's invocation may occur at any time once a fixed interval  $T_i$  since the last invocation passed

In the above task models intra-task parallelism is not allowed: only a single job of a task can be active at a time.

$T_i$  indicates the period in the periodic model and the minimum inter-arrival time in the sporadic one. There are three different types of deadlines  $D_i$  with respect to the value of  $T_i$ :

- Implicit deadlines: deadlines correspond to the periods,  $D_i = T_i$

- Constrained deadlines: deadlines are less than or equal to the periods  $D_i \leq T_i$

- Arbitrary deadlines: deadlines can be less than equal to or greater than the periods

Tasks and therefore real-time systems can be classified according to the consequences of a deadline miss [Mal09] into:

- *hard*: the task has to produce a result within its deadline otherwise the whole system is considered to have failed

- *firm*: the task is required to produce a result within its deadline. Eventual late results are discarded

- *soft*: the task has an associated deadline which, however, is not absolute but expressed as an average response time required

The developed real-time operating system is targeting hard real-time systems.

### 1.2 Timing Analysis

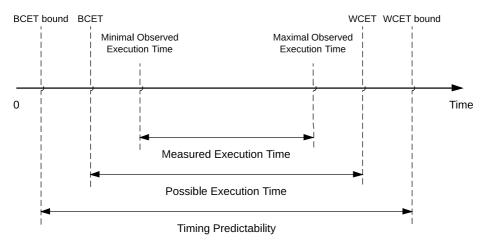

The maximum execution time is a key attribute of a task and it is commonly called Worst Case Execution Time (WCET) [WEE<sup>+</sup>08]. The calculation of the WCET is crucial in the development and validation of a real-time systems. *Timing analysis* is the process of computing execution time bounds [WEE<sup>+</sup>08], which not necessarily correspond to the WCET, as shown in figure 1.2.

Figure 1.2: Relationship between measured execution times, WCET and WCET bound

*Timing analysis* has to face several problems when computing the WCET for a task. It has to consider each path of the control flow through the task and its time to be executed on the specified hardware. The computation of the execution time of a path is harder when the underlying hardware makes use of history-dependent components such as caches.

### 1.3 Time composability

Complex systems are often built integrating independent components. A composable architecture assures that the components can be integrated together without changing their behaviour [KO02]. In real-time systems we refer to *time-composability* as the property of being composable in the time domain; that is, the timing characteristics of a component do not change upon composition of that component in a larger system.

Modern real-time systems development relies on the assumption that the timing behaviour of the whole system can be obtained by composing the WCET of its components [BMV13]. When developing a system, assuming composability has an innate characteristic is not always correct: several issues arise from modern hardware which affects not only single component's timing behaviour but even time-composability. As a non-time-composable hardware feature we can think about the use a cache when two functions are executed: each function's timing behaviour is probably not going to be preserved [LRL10]; the same reasoning can be made for bigger components such as tasks. Moreover, not only hardware can interfere with time-composability but even the execution of the operating system's services has an influence on the execution of application's tasks. Using a time-composable operating system is highly desirable when developing systems with strict timing-behaviour constraints [BMV13].

### 1.4 Real-time Operating Systems

An Operating System (OS) is a software working as an interface between computer hardware and application programs, controlling the execution of other applications [Sta08]. An OS tries to hide hardware complexity from the programmer and in order to do so it provides several services [Sta08], like:

- *Executing a program.* That is, performing several operation like loading program's code or initializing hardware

- Accessing I/O devices. Each hardware resource may need dedicated instructions, the OS tries to provide a uniform interface avoiding the programmer from dealing with these details (*drivers*)

*Providing core functionalities.* In order to avoid each programmer from implementing them, assuring that these functionalities are correctly implemented

Controlling accesses to the system

Controlling accesses to data

Detecting errors and handling them

An OS is usually developed relying on a hardware interface called Instruction Set Architecture (ISA), which is the set of instructions the underlying hardware is able to execute. The OS uses these instructions (some of them are reserved to the OS itself and not accessible by user programs) to provide its services. Likewise the operating systems offers two other interfaces:

- Application Binary Interface (ABI): the ABI is the system call interface to the OS and it defines the rules for applications portability

- Application Programming Interface (API): the API offers higher level functions to perform system calls. Developing applications around an API ensures their portability to systems supporting the same API

A computer system is a set of resources (like CPU and memory), therefore the OS can be seen as a program developed to manage these resources. An OS is usually made of several components. The key part of an operating system is called *kernel*. The kernel contains the most used services of the OS and is permanently placed in memory during system's execution. An OS uses an abstract representation of a computer program, usually called process. The role of the OS as a resource manager is to assign resources to processes so that they can execute. In order to correctly manage resources, operating systems implement several features:

- Interrupts handling: interrupts provide the operating system a way to react to external events. Interrupts are used to manage I/O devices. An interrupt makes the computer suspend the current execution and jump to an operating system's routine called Interrupt Service Routine (ISR) responsible for handling the exception associated to the interrupt

- *Memory management*: each process needs some memory for its execution. The OS has to grant each process an adequate amount of memory and has to grant also that every process accesses this memory correctly: for example a process should not access other processes memory. *Memory protection* allows the OS kernel to avoid any illegitimate access

• *Multitasking*: on modern computers several programs are executed at the same time. The OS has to grant each program to proceed in its execution arbitrating a possibly single CPU. A component of the kernel is called *scheduler* and is responsible for allocating the CPU to processes. In order to perform this allocation, the OS must be able to take control over a running process. This may happen after a process explicit request or due to an external event (interrupt). When gaining control of the CPU the OS has to save the current execution state of the process in order to restore it later (we call this execution state *context*). After having saved the context the scheduler has to select the next process to execute, whose context is going to be restored. The just explained process is called *context switch* and is a key feature implemented by an OS

A real-time system consists of one or more applications, each containing one or more communicating tasks. In order to manage the complexity of such systems a Real-Time Operating System (RTOS) is used. As a normal OS, a RTOS has to handle resource arbitration, and more precisely: time sharing, (virtual) memory allocation and inter-task communication. However, the real-time nature of the OS imposes more requirements. First of all a RTOS has to consider time as a key parameter [Tan07]. More features of a RTOS are listed in [SBWT87]:

- A RTOS must support different types of task, from small and high rate tasks to larger and less frequently executed ones

- A RTOS should not rely on a simplified task model and therefore it should be able to handle both periodic and sporadic tasks

- Inter-task communication is time-critical and different tasks may assume different models of communication

- Different systems may have different requirements on the operating system. Some systems may need full RTOS functionalities such as complex scheduling policies or space partitioning while others may need a more lightweight OS, so an RTOS should be configurable according to the system's needs

#### 1.4.1 Memory Management

As previously stated memory management and inter-task communication are key features offered by a RTOS. Both memory allocation and inter-task communication mechanisms implemented by a RTOS have to assure that tasks timing constraints are not going to be violated due to other task's interference. More precisely, in the case of memory allocation a good and widely adopted way of guaranteeing no interference between tasks is not allowing shared memory using tasks space partitioning, which can be implemented through memory virtualization or memory protection. Moreover a RTOS has to provide to tasks ways of communicating between each other without violating deadlines constraints, not allowing shared memory means that communication services have to be implemented by the RTOS.

#### 1.4.2 Scheduling Algorithms

Several scheduling algorithms have been developed to share a single-processor between tasks. Scheduling algorithms can be classified in different ways. Scheduling may be:

Static: based on offline information

Dynamic: based on run-time information

A scheduling algorithm can also be classified as:

- *Preemptive*: a task computes for a certain amount of time then the control comes back to the operating system which selects an other task to be assigned the processor

- Non-preemptive: a task executes until completion or until it yields control to another task

We call a scheduler *work-conserving* if it never lets the processor idle when there is a task ready to run.

Several algorithms have been developed for scheduling tasks on a single-processor, both static and dynamic. *Rate-monotonic* [LL73] is a static priority algorithm assigning each task a priority proportional to its *request rate* (defined as the reciprocal of its period). On the other hand Earliest-Deadline-First (EDF), presented in [LL73], is a dynamic priority scheduling algorithm. EDF assigns the highest priority to the task whose current request has the nearest deadline. EDF is proved to be optimal for tasksets with implicit deadlines; that is, it reaches a processor utilization factor of 1. Scheduling on multi-processors systems attempts to solve two problems [DB11]: allocation problem (decide to which processor allocating a task) and priority problem (decide in which order the jobs of all tasks should execute). In the last years two main approaches to multi-processor scheduling have been investigated: partitioning and global scheduling [CFH<sup>+</sup>04]. With partitioned scheduling each task is permanently assigned to a processor and then each processor is scheduled independently. On the other hand, global scheduling enqueues all the tasks in a priority queue from which highest priority tasks are then selected for the execution. Unfortunately, optimal solutions found for the scheduling problem on single-processors like EDF result in non-optimal schedules with very low processor utilization [DL78]. Partitioning approaches reduce the problem of multi-processor scheduling to a set of single-processor ones.

#### 1.4.2.1 Partitioning

A well known approach to the scheduling in systems where multiple applications share one processor is the partitioned one: static non-work-conserving schedulers, such as time division multiplexing, assign applications to the processor according to a pre-defined offline order. Since scheduling decisions do not rely on the run-time behaviour, such schedulers provide time isolation (timecomposability between tasks or *partitioning*): the actual behavior of an application is independent of others.

It is also desirable to have different applications follow different computational models. In order to do so a two-level scheduling is required: *inter-application* and *intra-application*. Preemptive *intra-application* schedulers promise to reach better processor's utilization than non-preemptive approaches but at the cost of more overhead.

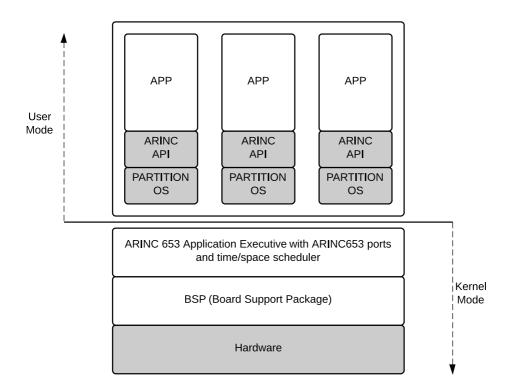

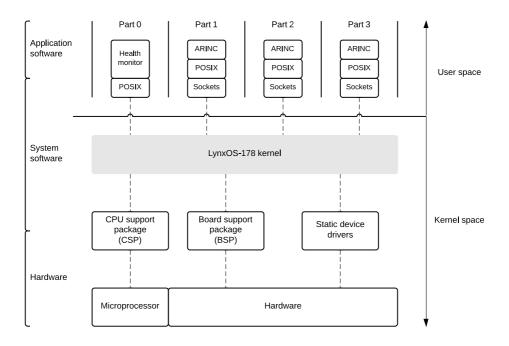

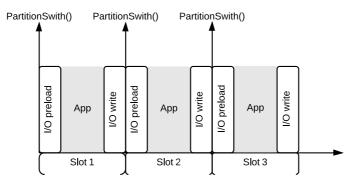

ARINC653 [Gro03] is a standard specification for time and space partitioning in safety-critical avionics real-time operating systems. According to ARINC, time is divided in a number of slots called partitions, each of which is assigned an application. In each partition a second-level scheduler can be used to allocate the CPU to the partition's tasks, see figure 1.3 for a sample of architecture for an ARINC653 RTOS [Inc08].

Just a few real-time operating systems implement partitioning with two-level scheduling, *inter-application* and *intra-application*. CompOSe [HEM<sup>+</sup>11], PikeOS [Pik], INTEGRITY [INT] and LynxOS-178 [Lyn] implement both partitioning and two-level scheduling.

Figure 1.3: Architecture's structure of an ARINC653 system (from [Inc08])

#### 1.4.3 PikeOS

PikeOS [Pik] is a commercial micro-kernel RTOS targeting safety-critical embedded real-time systems and supporting the ARINC653 standard. PikeOS is able to run different applications, whether real-time or not, in different virtual machines on a single underlying hardware. For real-time applications PikeOS is able to guarantee spacial and temporal constraints.

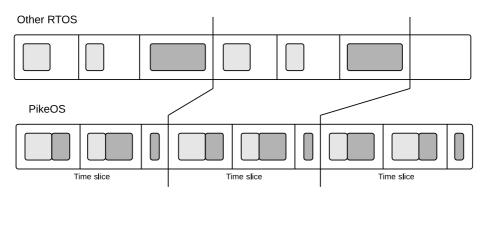

PikeOS executes applications with different timing requirements: hard realtime, soft real-time and non real-time. In order to support all these kinds of applications PikeOS implements both a priority-driven and time-driven scheduler. Such a scheduler allows to re-allocate computing times not used by hard real-time tasks. In figure 1.4 the difference between PikeOS scheduler and a normal RTOS scheduler is shown.

Real-time task Non-real-time task

A time slice is assigned to each virtual machine, each virtual machine receives a fixed amount of time and is able to schedule real-time tasks itself. As previously stated, PikeOS scheduler is able to exploit the *slack time* (not used computing time) and allocate it to non real-time tasks. We can see in figure 1.4 how it reduces the time exclusively allocated to these tasks, with respect to a standard scheduler.

#### 1.4.4 INTEGRITY

never masks or disables interrupts.

INTEGRITY [INT] is a partitioning RTOS aiming to provide reliability, security, and maximum performance to embedded systems. INTEGRITY uses memory protection to separate each application execution from other applications. Partitioning ensures that a task is granted enough resources to execute correctly and does not affect other application's and OS execution. INTEGRITY exploits the Memory-Management Unit (MMU) hardware and therefore offers memory protection without sacrificing performances. INTEGRITY is implemented to react to interrupts as fast as possible and in order to do so it

One of INTEGRITY's goals is a safe handling of memory: in order to always guarantee enough memory to the kernel, kernel's objects are never placed in ker-

Figure 1.4: Comparison between PikeOS and a normal RTOS scheduler (from [Pik])

nel's memory. RTOS services always use resources owned by the calling task. Moreover these services are executed on a dedicated kernel's stack in order to prevent stack overflow and to allow user's tasks to precisely specify their stack size.

#### 1.4.5 LynxOS-178

LynxOS-178 [Lyn] is a commercial hard real-time operating system that supports both POSIX and ARINC653 standards. LynxOS-178 targets safety-critical real-time systems and guarantees time and space-partitioning relying on virtual machines, which lead system events happening in a partition not to interfere with events in another. Each RTOS partition behaves just like a single, independent RTOS. LynxOS-178's partitioning grants three types of exclusive access: time, space and resources.

Time is divided according to ARINC653 specification in fixed-size time slices, each of which is assigned to a partition.

Memory partition is accomplished by dividing it in blocks of different address spaces. Each partition is assigned one and only one block.

Partitioning of resources means that every resource is associated to one and only one partition at any time so that a fault can be handled in a single partition, without affecting the others. For example each partition uses a RAM-based file system which is private to the partition and never shared.

LynxOS-178 structure is depicted in figure 1.5. The *CPU support package* contains all processor family-specific routines. The *Board support package* contains all the routines needed for booting and controlling the hardware. The *Static device drivers* are components isolating specific hardware details from application code and are statically compiled with the kernel. *LynxOS-178 kernel* offers partitioning functionalities.

#### 1.4.6 CompOS

CompOSe [HEM<sup>+</sup>11] is a composable, light weight real-time operating system targeting Multi-Processor Systems on Chip (MPSoC). Each processor executes an independent instance of CompOSe which has no idea of the existence of the other processors, therefore each scheduler performs local decisions. CompOSe scheduler's aim is to ensure that every task executes without any interference, in order to do so some requirements need to be fulfilled:

Figure 1.5: Architecture's structure of LynxOS-178 RTOS (from [Lyn])

- Preemption-based CPU sharing, so that system correctness does not rely on tasks well-behaviour

- Context-switch mechanism not interfering with user tasks; that is, running in constant time

- Scheduling between applications with adequate cache management

CompOSe implements a two-level scheduler in order to have different intraapplication schedulers. Moreover a slack manager allows to exploit all unused capacity.

CompOSe uses C-HEAP [NKG<sup>+</sup>02] as a communication API. C-HEAP does not use atomic operations (therefore no need for locks and semaphores) or interrupts, all communication takes place on a buffer through explicit calls to *acquire* and *release*. A C-HEAP FIFO is a circular buffer placed in shared memory. FIFO read and write pointers are hold in producer and consumer local memory in order not to make a task suffer from remote access latency. If there is enough space in the task's local memory even FIFO's communication buffers are placed there to avoid accessing remote memory. When communication buffers are placed in the local memory, before starting the execution of a task data has to be copied from remote locations to local buffers.

#### 1.4.7 TiCOS

Time-Composable Operating System (TiCOS) [BMV12] is an open-source timecomposable real-time operating system implementing a two-level partitioned scheduler and conforming to the ARINC653 standard. TiCOS is based on POK [DL11] a light weight ARINC653 operating system released under the BSD license. Details of TiCOS operating system can be found in Chapter 3.

### 1.5 The T-CREST Project

Real-time embedded systems are everywhere in our daily life. Examples can be found in the most different fields like space systems, avionics, automotive and consumer electronics. Those fields are constantly evolving and improving, so real-time embedded systems should improve too [DB11]. Real-time embedded systems evolution takes place on two different sides, one regards systems analyzability while the other regards system performances.

The modern technological progress causes software complexity to grow and along with this complexity growth even processing demand is increasing [DB11]. This increase of processing demand made hardware producers try to create more powerful processors. The first trial was miniaturization, following the Moore's law, which says that every two years the density of transistors on an integrated circuit doubles (that is: every two years processor speed doubles). But this was no longer possible due to problems of heat dissipation and high power consumption. The second and still used trial was putting more than one processor on a single chip: this gave birth to multi-processors.

Even for real-time embedded systems there is the need for more powerful processors and thus a big effort has been spent in the last years finding ways of creating time-predictable real-time systems on modern multi-processors. Timepredictability is a key feature of safety-critical systems (systems whose failure can result in the loss of life). In such systems the worst case execution time has to be known in order to assure a certain behaviour (response time) when critical events happen. However, multi-processors vendors focus their attention on end-user needs and so they try to give best performances in the average case, leading to bad results in the worst case execution and making those processors hardly analyzable [DB11].

The aim of T-CREST is to create a time-predictable chip multi-processor, developing the processor, memories and the interconnect optimized for minimizing the WCET. Moreover, through time-predictable caches the system aims to fulfill the increased needs of processing power. Patmos [SSP+11] is the single-processor used to build T-CREST architecture. The final goal of T-CREST is creating an architecture capable of high performances but still easily analyzable.

### 1.6 Thesis Structure

The thesis is structured as follows:

- 1. First we present Patmos and TiCOS:

- Chapter 2: The Patmos processor: a detailed description of the processor's instruction set and memories

- Chapter 3: The Operating System: a description of the OS kernel's architecture and library

- 2. In order enable on the T-CREST architecture a computational model more complex than the direct mapping of threads to processors; that is: executing an operating system on each Patmos core, some extensions to the processor itself were needed:

- Chapter 4: Processor extensions: presents a set of extensions performed to the Patmos processor and a set of useful possible extensions

- 3. Finally we present the extensions made to TiCOS to port it to Patmos:

- Chapter 5: TiCOS extensions: details the main changes performed to TiCOS starting from the architectural-dependent layer up to the application library

Some details about Patmos simulator and ELF file format can be found in Appendix A: Software Simulator of Patmos and Appendix B: ELF file structure.

# Chapter 2

# The Patmos Processor

Patmos [SSP<sup>+</sup>11] is a time-predictable, reduced instruction set (RISC) processor targeting real-time systems aiming to reduce the complexity of WCET analysis. The Patmos pipeline is made of 5 stages:

- FE: instruction fetch

- DEC: instruction decode

- EX: execute

- MEM: memory access

- WB: register write back

In the following, Patmos is described. The aim is to clearly define the architecture, highlighting the main points in its technical report [SBH<sup>+</sup>] which influence the development of an operating system.

### 2.1 Memory

Patmos uses several local memories in order to reduce memory operations latency. Four types of local memories are used:

- Method cache

- Stack cache

- Data cache

- Scratchpad memory

Memory access instructions which deal only with local memory (that is: scratchpad or stack cache) are guaranteed to never stall the pipeline while other memory instructions (accessing data cache or global memory) define opcodes that either stall the pipeline or perform decoupled operations.

#### 2.1.1 Method Cache

The Patmos processor implements the idea of a method cache [Sch04]. With today's performance requirements caches cannot be avoided due to their important role in filling the gap between processors speed and memory access delays, however caches focus on the average case performance, making the system hardly analyzable from a WCET point of view.

A standard instruction cache makes each instruction's WCET potentially suffer from the penalties of a cache miss and subsequent refill. The method cache is structured in order to free all instructions from cache miss penalties, these penalties are relegated to the function calls and returns.

The basic idea is that functions do not usually have big sizes and that an instruction cache could be divided in blocks that can possibly hold an entire function. The whole replacement mechanism is so performed on blocks of instructions not on single instructions: the instructions of a functions are in this case guaranteed to be cache hits while eventual cache misses can happen on function calls (called function miss) and function returns (caller function miss).

No way for loading single instructions is provided: cache can only be manipulated through blocks. Since the size of a block is fixed and functions bigger than this size can exist functions are allowed to be split into several blocks.

Some limitations caused by the method cache structure do exist:

- The size of the code sequence that can be loaded is bounded by the size of the method cache. However, as said, functions can be split in more segments

- Since call instruction does not carry any information regarding the function's size this information has to be saved in memory just before the first function's instruction

- Due to block-oriented manipulation of the cache more code than the function's one could be loaded into the cache

Just like other caches, different replacement policies can be implemented for the method cache: both FIFO and LRU are being investigated in the Patmos development.

#### 2.1.1.1 FIFO

When working with the FIFO policy the method cache allocates to each segment of code a number of adjacent blocks. The first block assigned to the segment is labeled with the base address of the code segment it is holding, the other blocks labels are empty. The method cache is extended with a pointer, pointing to the location where a new loaded block will be placed and updated according to the FIFO semantics.

#### 2.1.1.2 LRU

[SBH<sup>+</sup>] suggest that LRU replacement can be implemented in Patmos. This implementation needs more memory to work: a segment of code is no longer placed in adjacent blocks but its blocks can be split in the whole cache according to LRU semantics. Each block must be therefore extended with its real memory address and it LRU timestamp.

When an instruction has to be fetched all the cache blocks have to be looked for, if one of the blocks address contains the searched instruction then it is not loaded (already in the cache). If the instruction is not in the cache then its code segment has to be loaded.

A method cache may not have enough space to hold a new code segment, in this case some older segment has to be removed from the cache: note that the replacement mechanism removes all the blocks of a segment, not single blocks (for doing this a data structure is needed to keep track of which blocks make up a segment. LRU implementation clearly need more hardware than the FIFO one and may also result in an additional pipeline stage in order to perform the lookup needed at each instruction fetch.

#### 2.1.2 Data Cache

The data cache, as a normal cache, is used to speed up memory accesses. Patmos data cache uses a write-through policy, every store instruction writes changes to the data cache and to the main memory. Write-through policy leads to a higher number of memory accesses but results in a more analyzable system from a WCET perspective (less cache states to be taken into account).

Different opcodes for memory access instructions are provided by the Patmos instruction set allowing not only access different types of value (8, 16 and 32 bits) but also to perform blocking memory operations (stalling the pipeline) or decoupled ones.

Operations accessing directly the global memory are provided in order to bypass the data cache.

#### 2.1.3 Stack Cache

The stack cache presented in [ABS13] is a dedicated cache meant to hold stack allocated values. The idea of having more than a cache holding different types of values (data cache, stack cache and instruction cache) is intended to help simplify the WCET analysis.

The stack area holds return address, callee saved registers, and function local variables. This data has a high access frequency and so it will greatly benefit of caching. Moreover stack data is always function local and therefore some optimizations can be done: due to its locality stack cache data does not need to be consistent with the main memory and when a function returns this data can simply be discarded with no need to write back the content. The stack cache has a fixed size so when some of its content has to be replaced it is written back to memory.

The stack cache is managed by the compiler: when a function is called a stack frame of the required size is reserved on the top of the stack and when a function returns this space is freed. When a function returns to a caller the frame of the caller must be ensured to be in the stack cache (due to the function call chain it may have been split to the main memory). Doing so each memory access in the body of the function is guaranteed to be a hit while a stack cache miss can only happen when reserving or ensuring a stack frame. In order to manipulate the stack as just described the Patmos ISA defines the following instructions:

- reserve sres: reserves space in the stack cache and may spill data to the main memory if there is no enough free space

- ensure sens: when returning from a function call sens ensures that the stack frame of the calling function is available. May need to fill the cache with previously spilled data

- free sfree: frees the reserved space on the stack

These instructions specify as an immediate parameter the size of the frame to be reserved/ensure so that the interaction with stack in the function calls tree can be easily analyzed (easy WCET calculation).

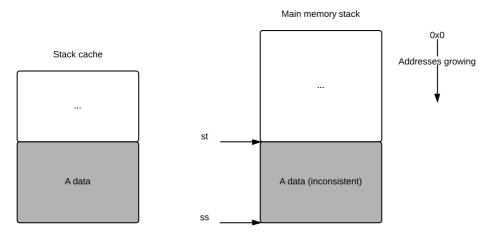

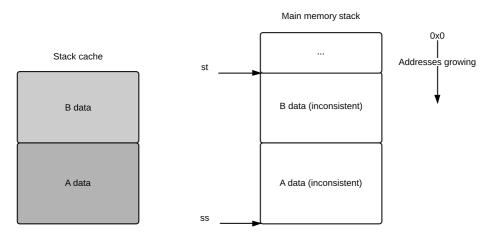

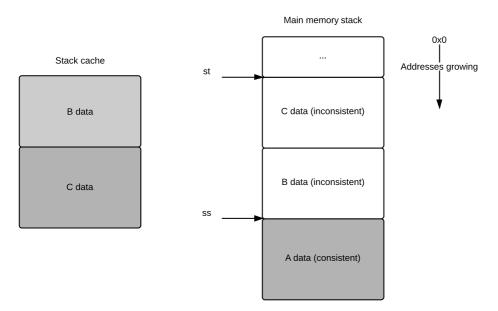

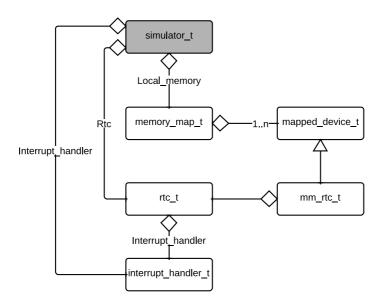

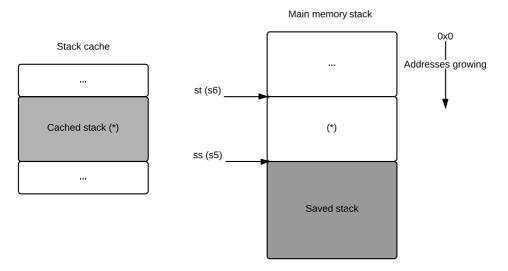

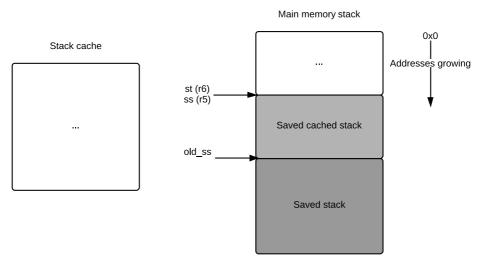

In the Patmos implementation the stack cache is a data structure placed in the local memory holding values from the actual global memory stack. Consistency with the global memory is managed through 2 pointers:

- st: pointer to the top of the stack

- ss: pointer to the last element of the stack cache spilled to main memory

The code in listing 2.1 represents a simple example used to show the stack cache behaviour. Assuming each function reserves (and ensures after each function call) 16B and the whole stack cache size is 32B, the evolution of stack and stack cache will be the one in figures 2.1, 2.2 and 2.3.

```

Listing 2.1: Code snippet to show the stack cache behaviour

void C() {

// ...

}

void B() {

// ...

C();

// ...

C();

// ...

X

C();

// ...

X

Void A() {

```

Figure 2.1: Stack cache status after the call A(). Space for A is reserved on the stack and the stack cache. The main memory is not consistent with the cache

14 // ... 15 B(); 16 // ... 17 } 18 19 A();

The organization of the stack cache has some drawbacks:

- At any moment the program cannot access more stack data than the stack cache size. To solve this problem the stack frame can be split or the shadow stack can be used, an extra stack placed in main memory

- When a pointer to data placed on the stack cache is passed to another function it has to be ensured that the pointed data will not be split to main memory as long as it is needed. Otherwise this kind of aliased data can be placed on the shadow stack

- Reserve and ensure instructions only accept constant size immediate arguments, therefore dynamic size data has to be placed on the shadow stack

Figure 2.2: Stack cache status after the call B(). Space for B is reserved on the stack and the stack cache. The stack cache becomes full, main memory is still not consistent with the cache

Figure 2.3: Stack cache status after the call C(). The data for A is spilled to main memory and replaced with C data

#### 2.1.4 Data Scratchpad

Patmos provides a local memory called data scratchpad. The Patmos ISA has instructions that allow accessing this local memory. These instructions do not stall the pipeline.

The address space of the local memory is the same as that of global one but the used range is different. Instructions to access the data scratchpad are detailed in Section 2.3.8.

### 2.2 Registers

Patmos provides three distinct register files:

- R: 32 general-purpose registers (32 bit), shown in figure 2.5

- S: 16 special-purpose registers (32 bit), shown in figure 2.6

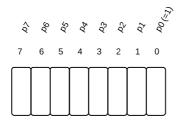

- P: 8 predicate registers (1 bit), by convention p0 is set to true (1), shown in figure 2.4

Figure 2.4: Predicate registers (P)

r0 is always set to 0 and read-only. The other general-purpose registers are used, according to a compiler convention, as follows:

- r1 and r2: contain the result of a function (up to 64 bits)

- r3-r8: contain the arguments of a function

- r27: temporary register

- r28: frame pointer

| Zero                    | r0  |

|-------------------------|-----|

|                         | r1  |

| Function result         | r2  |

|                         | r3  |

|                         | r4  |

|                         | r5  |

| Arguments               | r6  |

|                         | r7  |

|                         | r8  |

| C                       | r9  |

|                         | r10 |

|                         | r11 |

|                         | r12 |

|                         | r13 |

|                         | r14 |

|                         | r15 |

|                         | r16 |

|                         | r17 |

|                         | r18 |

|                         | r19 |

|                         | r20 |

|                         | r21 |

|                         | r22 |

|                         | r23 |

|                         | r24 |

|                         | r25 |

| _                       | r26 |

| Temp register           | r27 |

| Frame pointer           | r28 |

| Shadow stack pointer    | r29 |

| Function pointer        | r30 |

| Function offset pointer | r31 |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Figure 2.5: General-purpose registers (R)

- r29: shadow stack pointer

- r30: address of the return function (function base)

- r31: offset of the return instruction in the return function (function offset)

Special-purpose registers are dedicated to hold special values:

Unused p7 - p0 Load result sm Multiplication result (low) s Multiplication result (high) sh s4 Stack cache spill pointer SS Stack top st s7 s8 9 s10 s11 s12 s13 s14 s15

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Figure 2.6: Special-purpose registers (S)

- s0: lower 8 bits are used to save and restore P, the other bits are reserved and not yet used

- s1 (also named sm): contains the result of a decoupled load operation. The contained value can be signed or unsigned depending on the load's type

- s2 (also named s1): lower 32-bits of the result of a multiplication

- s3 (also named sh): upper 32-bits of the result of a multiplication

- s5 (also named ss): stack cache spill pointer, point to the top element of the stack that is saved in the main memory

- s6 (also named st): point to the top of the stack

## 2.3 Patmos ISA (Instruction Set Architecture)

Patmos allows bundles made of one or two instructions. Since instructions are 32 bits long bundles can be 32 or 64 bits. The most significant bit allows to distinguish between short and long bundles:

- 0: 32 bits long bundle

- 1: 64 bits long bundle

Several instruction's formats have been defined, each instruction respects a format; a single format can be used for several operations (with assigned opcodes). In the following all the Patmos instructions and operations are described.

#### 2.3.1 Binary Arithmetic

In this section opcodes for binary arithmetic with registers (ALUr), immediate operands (ALUi) and long immediate operands (ALU1) are going to be examined. In table 2.1 opcodes semantics are described, Op2 stands for immediate operand for ALUi, long immediate operand for ALU1 and register operand for ALUr.

#### 2.3.2 Multiply

Multiplications follow the ALUm format. Two opcodes are defined for this formats defining multiplication of normal integers and multiplication of unsigned integers, as shown in table 2.2. Multiplication are carried on in parallel with the normal pipeline and always terminate in constant number of cycles.

| Opcode              | Semantics             |

|---------------------|-----------------------|

| add                 | Rd = Rs1 + Op2        |

| sub                 | Rd = Rs1 - Op2        |

| xor                 | $Rd = Op2^Rs1$        |

| sl                  | Rd = Rs1 << Op2[0:4]  |

| $\operatorname{sr}$ | Rd = Rs1 >>> Op2[0:4] |

| sra                 | Rd = Rs1 >> Op2[0:4]  |

| or                  | Rd = Rs1 Op2          |

| and                 | Rd = Rs1&Op2          |

| nor                 | Rd = (Rs1 Op2)        |

| shadd               | Rd = (Rs1 << 1) + Op2 |

| shadd2              | Rd = (Rs1 << 2) + Op2 |

Table 2.1: ISA: binary arithmetic

| Opcode | Semantics                                                                                                              |

|--------|------------------------------------------------------------------------------------------------------------------------|

| mul    | $\begin{array}{l} sl = Rs1*Rs2\\ sh = (Rs1*Rs2) >>> 32 \end{array}$                                                    |

| mulu   | $ \begin{array}{l} sl = (uint32\_t)Rs1 * (uint32\_t)Rs2 \\ sh = ((uint32\_t)Rs1 * (uint32\_t)Rs2) >>> 32 \end{array} $ |

Table 2.2: ISA: multiplication

#### 2.3.3 Compare

Compare instruction follows the ALUc format. Operations perform comparisons between integers and unsigned integers putting the result in a predicate register.

#### 2.3.4 Predicate

Predicate instruction follow the ALUpformat and offer basic binary operations on predicate registers storing the result in a predicate register, opcodes and semantics are shown in table 2.4.

| Opcode | Semantics                 |

|--------|---------------------------|

| cmpeq  | Pd = Rs1 == Rs2           |

| cmpneq | Pd = Rs1! = Rs2           |

| cmplt  | Pd = Rs1 < Rs2            |

| cmple  | $Pd = Rs1 \le Rs2$        |

| cmpult | Pd = Rs1 < Rs2, unsigned  |

| cmpule | Pd = Rs1 <= Rs2, unsigned |

Table 2.3: ISA: compare opcodes

| Opcode | Semantics               |

|--------|-------------------------|

| por    | Pd = Ps1 Ps2            |

| pand   | Pd = Ps1&Ps2            |

| pxor   | $Pd = Ps1 \uparrow Ps2$ |

Table 2.4: ISA: predicate manipulation opcodes

#### 2.3.5 NOP

A single cycle no-operation instruction.

#### 2.3.6 Wait

The wait instruction format is called SPCw. These instructions wait for a multiplication or a memory access to end stalling the pipeline. One single opcode is defined (wait.mem), it makes the pipeline stall until a memory operation ends.

| Opcode   | Semantics                       |

|----------|---------------------------------|

| wait.mem | Wait the end of a memory access |

### 2.3.7 Move To/From Special

SPCt format is defined for its only opcode mts which moves the content of a general purpose register to a special purpose register. SPCf format is specified

for the opcode **mfs** which moves the content of a special purpose register to a general purpose register. Semantics are shown in table 2.5.

| Opcode | Semantics |

|--------|-----------|

| mts    | Sd = Rs   |

| mfs    | Rd = Ss   |

Table 2.5: ISA: move to/from special opcodes

#### 2.3.8 Load/Store Typed

Operations to access to the stack cache (sc), to the local scratchpad memory (lm), to the data cache (dc) and to the global shared memory (gm) are available. Load operations, in table 2.6, follow the LDT format while store operations, in table 2.7, follow the STT format. Load and store operations to the stack cache and the local memory do not stall the pipeline while the others do. However, when accessing the local memory, if the address maps some I/O device the operation may stall the pipeline.

Decoupled loads are also implemented which do not stall the pipeline and allow the execution to continue. These instructions put the loaded value into the special register sm. A wait instruction can be used to explicitly stall the pipeline. When a decoupled is tried to be executed while a previous one is still being processed the pipeline is automatically stalled so that the result of the first load will be available for at least one processor's cycle. A *use-delay* must be respected before accessing the destination register of a load operation.

Stores to the data cache use the *write-through* strategy with no *write allocate*, that is: when writing to data not present in the cache this data is fetched into the cache, if the data is present it is updated.

Loads to the stack cache are relative to the st pointer and can be performed on both slots of an instruction bundle. The other loads can only be issued on the first slot.

#### 2.3.9 Stack control

Stack control operation all refer to the STC format and allow to manipulate the stack cache. STC instruction immediate argument is always interpreted in word size. Opcodes referring to the operations detailed in Section 2.1.3 are shown in table 2.8.

| Opcode       | Semantics                                |

|--------------|------------------------------------------|

| lws          | $Rd = sc[Ra + Imm << 2]_{32}$            |

| lwl          | $Rd = lm[Ra + Imm << 2]_{32}$            |

| lwc          | $Rd = dc[Ra + Imm << 2]_{32}$            |

| lwm          | $Rd = gm[Ra + Imm << 2]_{32}$            |

| lhs          | $Rd = (int32\_t)sc[Ra + Imm << 1]_{16}$  |

| lhl          | $Rd = (int32\_t)lm[Ra + Imm << 1]_{16}$  |

| lhc          | $Rd = (int32\_t)dc[Ra + Imm << 1]_{16}$  |

| $^{\rm lhm}$ | $Rd = (int32\_t)gm[Ra + Imm << 1]_{16}$  |

| lbs          | $Rd = (int32\_t)sc[Ra + Imm]_8$          |

| lbl          | $Rd = (int32\_t)lm[Ra + Imm]_8$          |

| lbc          | $Rd = (int32\_t)dc[Ra + Imm]_8$          |

| lbm          | $Rd = (int32\_t)gm[Ra + Imm]_8$          |

| lhus         | $Rd = (uint32\_t)sc[Ra + Imm << 1]_{16}$ |

| lhul         | $Rd = (uint32\_t)lm[Ra + Imm << 1]_{16}$ |

| lhuc         | $Rd = (uint32\_t)dc[Ra + Imm << 1]_{16}$ |

| lhum         | $Rd = (uint32\_t)gm[Ra + Imm << 1]_{16}$ |

| lbus         | $Rd = (uint32\_t)sc[Ra + Imm]_8$         |

| lbul         | $Rd = (uint32\_t)lm[Ra + Imm]_8$         |

| lbuc         | $Rd = (uint32\_t)dc[Ra + Imm]_8$         |

| lbum         | $Rd = (uint32\_t)gm[Ra + Imm]_8$         |

| dlwc         | $sm = sc[Ra + Imm << 2]_{32}$            |

| dlwm         | $sm = gm[Ra + Imm << 2]_{32}$            |

| dlhc         | $sm = (int32\_t)dc[Ra + Imm << 1]_{16}$  |

| dlhm         | $sm = (int32\_t)gm[Ra + Imm << 1]_{16}$  |

| dlhuc        | $sm = (uint32\_t)sc[Ra + Imm << 1]_{16}$ |

| dlhum        | $sm = (uint32\_t)gm[Ra + Imm << 1]_{16}$ |

| dlbuc        | $sm = (uint32\_t)dc[Ra + Imm]_8$         |

| dlbum        | $sm = (uint32_t)gm[Ra + Imm]_8$          |

Table 2.6: ISA: load typed operations

The **sres** and **sens** operations are blocking operations.

#### 2.3.10 Call and Branch

These instructions apply to the CFLb format and supports different opcodes allowing to perform function calls (call), branches (brcf) and local branches (br) within the method cache.

A call instruction performs a function call and therefore stores the current

| Opcode               | Semantics                           |

|----------------------|-------------------------------------|

| sws                  | $  sc[Ra + Imm << 2]_{32} = Rs$     |

| swl                  | $  lm[Ra + Imm << 2]_{32} = Rs$     |

| swc                  | $  dc[Ra + Imm << 2]_{32} = Rs$     |

| swm                  | $\mid gm[Ra + Imm << 2]_{32} = Rs$  |

| shs                  | $sc[Ra + Imm << 1]_{16} = Rs[15:0]$ |

| shl                  | $lm[Ra + Imm << 1]_{16} = Rs[15:0]$ |

| shc                  | $dc[Ra + Imm << 1]_{16} = Rs[15:0]$ |

| shm                  | $gm[Ra + Imm << 1]_{16} = Rs[15:0]$ |

| sbs                  | $ sc[Ra + Imm]_8 = Rs[7:0]$         |

| sbl                  | $lm[Ra + Imm]_8 = Rs[7:0]$          |

| sbc                  | $dc[Ra + Imm]_8 = Rs[7:0]$          |

| $\operatorname{sbm}$ | $\mid gm[Ra + Imm]_8 = Rs[7:0]$     |

Table 2.7: ISA: store typed operations

| Opcode | Semantics                                                                          |

|--------|------------------------------------------------------------------------------------|

| sres   | Reserves space on the stack<br>(eventually spilling other frames to main memory)   |

| sens   | Ensures that a stack frame is entirely loaded<br>otherwise refills the stack cache |

| sfree  | Frees space on the stack frame<br>(no spill/fill)                                  |

Table 2.8: ISA: stack control operations

function offset into register r31 (function address has to be saved manually by the programmer/compiler) in order to return from the call itself.

Since both call and brcf opcodes perform non local jumps they can result in a method cache miss and a subsequent refill. On the contrary a br is always guaranteed to be a cache hit.

call is an absolute operation so the immediate operand is interpreted as an *unsigned int* while **br** and **brcf** are PC-relative and therefore the operand is considered to be *signed*. In both cases the operand is assumed to be word size.

Call and branch instructions are executed in the EX stage of the pipeline, the instructions fetched during the decode and the execution step of a branch are

| call          | Function call, absolute, with cache fill   |

|---------------|--------------------------------------------|

| $\mathbf{br}$ | Local branch, PC relative, always hit      |

| brcf          | Local branch, PC relative, with cache fill |

Table 2.9: ISA: immediate Call and Branch

still executed, this results in a delay of 2 instructions which has to be taken into account be the compiler/programmer (branch-delay slots).

All call and branch instructions can only be placed in the first position of the bundle.

#### 2.3.11 Call and Branch Indirect

This instruction is just like the call and branch one but takes a register operand rather than an immediate operand. A new format, called CFLi is therefore defined. As for the call and branch the three opcodes call, brcf and br are provided. Everything that was said in Section 2.3.10 regarding method cache interaction, parameter interpretation, and branch delay is also true for call and branch indirect.

| call          | Function call, absolute, with cache fill   |

|---------------|--------------------------------------------|

| $\mathbf{br}$ | Local branch, PC relative, always hit      |

| brcf          | Local branch, PC relative, with cache fill |

Table 2.10: ISA: register Call and Branch

#### 2.3.12 Return

Transfer control back to the calling function or return from an interrupt. **ret** may cause a cache miss and subsequent cache refill to load the target code.

# Chapter 3

# The Operating System

TiCOS [BMV12] is a time-composable real-time operating system developed within the framework of the Probabilistically Analysable Real-Time Systems (PROARTIS) project (www.proartis-project.eu) supporting the ARINC653 software specification and originally targeting the PPC architecture. TiCOS is based on POK [DL11], a light weight operating system implementing the AR-INC653 standard and distributed under the BSD license.

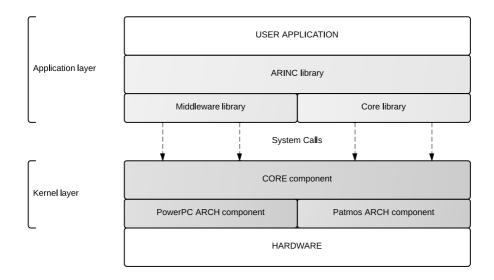

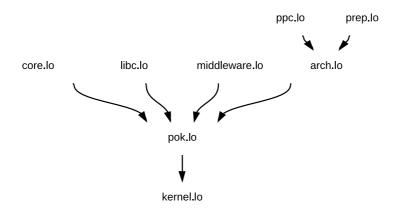

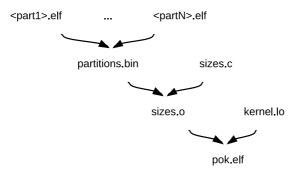

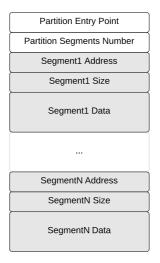

The high level architecture of TiCOS is shown in figure 3.1. It is made of two basic layers: the kernel layer and the application layer. The kernel layer is responsible for implementing the OS services while the application layer is composed by the user application, a core library layer, the ARINC library layer and the middleware library layer. The ARINC library offers a simple set of ARINC services. Those services are implemented (just like the core library functionalities) through the system call mechanism to the middleware layer. That mechanism makes the systems start executing in supervisor mode and call the proper kernel layer services.

Figure 3.1: High level structure of the OS (from [BMV12])

## 3.1 The Kernel Layer

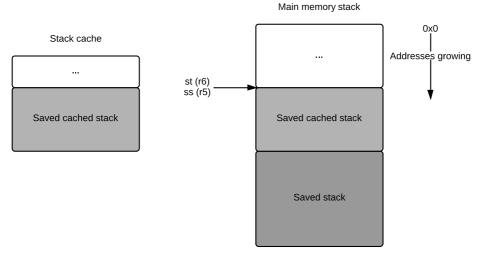

This layer is made of two fundamental components: an architectural dependent part (called *arch component*) and an architectural independent part (called *core component*), both parts implement kernel services but while the first one accesses directly architectural functionalities (to implement for example: timer, context switch, memory management, etc.) the *core component* does not need to directly use the underneath architecture. This kind of structure makes it possible to target an architecture different from PPC focusing only on changing the *arch component* and eventually adjusting the *core component*. Adjustments to the core component may be needed, as in the case of Patmos porting, for operating systems not supporting memory virtualization or for changing the loading mechanism of applications.

The kernel layer as a whole provides the following services:

- Partitions support. Partition is the name used by ARINC to indicate an application made by one or more threads. TiCOS wants to provide time-composability and for doing so it implements time and space isolation among partitions. Each partition is granted its own space and no shared memory is allowed

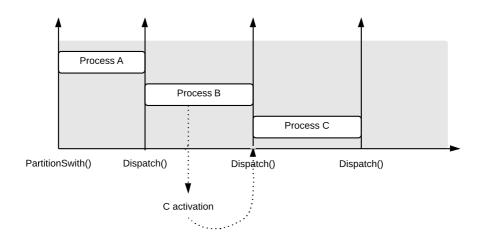

- Scheduling. A two-level scheduling algorithm is implemented. First a

partition is selected for execution according to a cyclic strategy then a selected partition's thread is chosen according to a fixed priority policy

- Lock objects management. Lock objects are used by the middleware layer to implement events and thus providing synchronization for buffers and blackboards (ARINC communication mechanisms). TiCOS works in a run-to-completion semantics which assures there's no need to worry about mutual exclusion; therefore locks are not used for that purpose. A lock object memorizes threads which are waiting for it to be free, at the moment priority policies are not used to select the next thread to be unlocked

- Ports support. Ports are the ARINC way of communicating between partitions, since partitions do not share memory the kernel is responsible for copying messages from source ports to destination ports

### 3.2 ARINC653 Entities

The ARINC specification defines several entities; some of these entities represent active components of a real-time systems, such as partitions and processes, while others represent communication mechanisms such as events, semaphores, blackboards, buffers and ports.

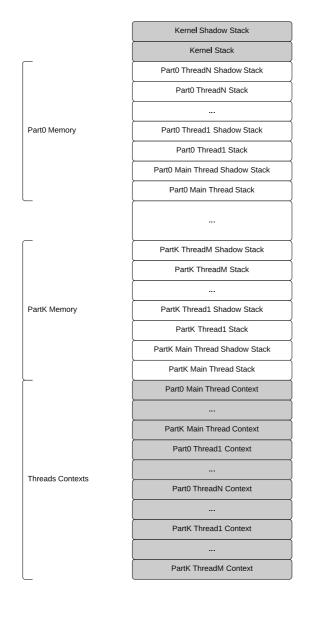

#### 3.2.1 Partitions and Processes

An application is usually made of an ARINC partition (the equivalent of a POSIX process) and each partition is made of threads. Each partition has a main thread which runs only once and creates all other partition's threads. Each partition is allocated a fixed time slot and is not allowed to share memory with other partitions. ARINC processes are the way the ARINC653 specification names tasks or POSIX threads. Processes have defined priorities and are allowed to share memory. In TiCOS the scheduling of processes inside a partition is made by a fixed-priority constant time scheduler, called O(1) scheduler and detailed in Section 3.4.2.

#### 3.2.2 Events

ARINC events can assume one between two states: *set* ("up") and *reset* ("down"). When an event is in *set* state it allows all the waiting processes to continue.

When an event is in *reset* state all processes waiting for the event are blocked [TBV10]. In TiCOS ARINC events are implemented through kernel locks; each middle-ware event is associated to one and only one kernel lock (and has the same identifier).

#### 3.2.3 Semaphores

The aim of ARINC semaphores, just like normal semaphores, is to provide mutual exclusion in accessing a shared resource. Shared resources can only exist between processes of the same partition, however, as said, TiCOS assumes runto-completion semantic between the processes of the same partition, this means that there is no need to worry about mutual exclusion. ARINC semaphores are implemented as nothing more than stubs since a semaphore lock is always granted by construction.

#### 3.2.4 Blackboards

Blackboards are one of the mechanisms used to make processes of a partition communicate. A blackboard holds only one message at once, so if a process displays a new message in a non-empty blackboard the previously shown message gets lost. Events are used to allow more processes use the same blackboard: an event is associated to each blackboard, when a process tries to read from an empty blackboard the event is set to "down" and the process is suspended. When a process displays a message the event is set to "up" and all processes waiting for that event become runnable again.

#### 3.2.5 Buffers

Buffers are another mechanism used to make processes of the same partition communicate. More than a message can be stored in a non-empty buffer, processes are not allowed to write to a full buffer and when a message is read it is removed from the buffer. When a process tries to receive a message from an empty buffer the associated event is set to "down". When a message is sent to an empty buffer the event is set to "up". Moreover, an associated event is used to handle the buffer's fullness: the event is set to "down" when a process tries to write to a full buffer and when a message is read from a full buffer the event is set to "up", making runnable all the waiting processes.

### 3.2.6 Sampling and Queueing Ports

Ports are used to make different partitions communicate. A queueing port is a communication channel which allows to enqueue tokens and read in the exact order they have been inserted and is the inter-partition equivalent to a buffer [TBV10]. A sampling port allows to read only the last inserted value, so writing to a sampling port means updating its content. Sampling ports are the equivalent to blackboards with the difference that writing and reading from a sampling port is never blocking [TBV10].

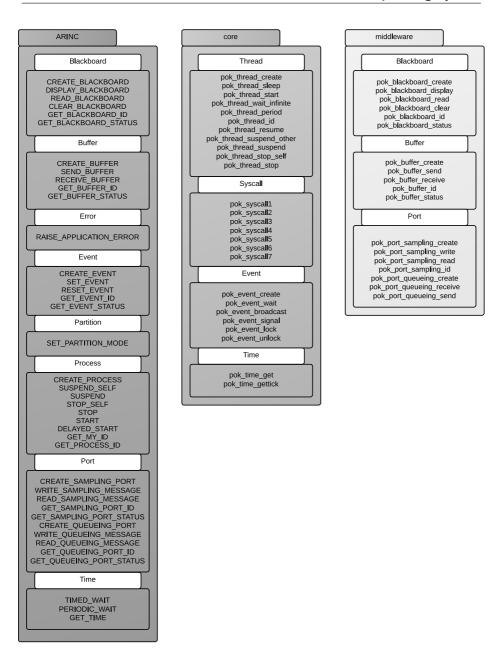

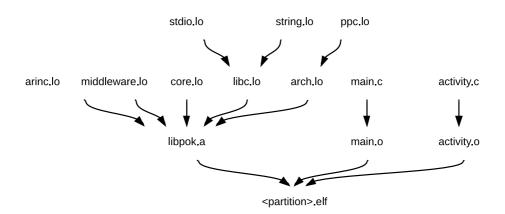

## 3.3 The Library Layer

The operating system library layer allows the user application to access TiCOS services through user-level functions. These functions are implemented through system calls to kernel services. The library is structured as shown in figure 3.2.

#### 3.3.1 Core Library

The contained functions offer the operating system's core functionalities. Some of these functions are used to implement the ARINC library. Application error codes are also defined. These functions are not part of the ARINC653 specification, using them in the user code results in a non-portable application. The functions in the core and middleware library are the only part of the POK operating system ([DL11]) kept unmodified, this is the reason why their names start with the pok\_ prefix.

- Event: is implemented through a kernel lock

- pok\_event\_create: performs a system call to create a kernel lock

- pok\_event\_wait: performs a system call to wait for the event associated to the lock, with a specified timeout

- pok\_event\_broadcast: performs a system call to wake up all the threads waiting for the event associated to the lock

- pok\_event\_signal: performs a system call to notify the first thread waiting for the event

- pok\_event\_lock: performs a system call to lock the kernel lock corresponding to the event (event set to "down")

Figure 3.2: Structure of the OS library for user applications

- pok\_event\_unlock: performs a system call to unlock the kernel lock corresponding to the event (event set to "up")

- **Syscall**: An identifier for each system call is defined as depicted in table 3.1. The following functions realize the system calls for different number of parameters.

| System call                   | ID  |

|-------------------------------|-----|

| CONSWRITE                     |     |

| GETTICK                       |     |

| GET_TIME                      |     |

| THREAD_CREATE                 | 50  |

| THREAD_SUSPEND                | 52  |

| THREAD_STOP                   | 55  |

| THREAD_PERIOD                 | 56  |

| THREAD_STOPSELF               | 57  |

| THREAD_ID                     | 58  |

| THREAD_SUSPEND_OTHER          | 67  |

| THREAD_RESUME                 | 68  |

| THREAD_START                  | 69  |

| THREAD_DELAYED_START          | 70  |

| MIDDLEWARE_SAMPLING_ID        | 101 |

| MIDDLEWARE_SAMPLING_READ      | 102 |

| MIDDLEWARE_SAMPLING_WRITE     | 104 |

| MIDDLEWARE_SAMPLING_CREATE    | 105 |

| MIDDLEWARE_QUEUEING_CREATE    | 110 |

| MIDDLEWARE_QUEUEING_SEND      | 111 |

| MIDDLEWARE_QUEUEING_RECEIVE   | 112 |

| LOCKOBJ_CREATE                | 201 |

| LOCKOBJ_OPERATION             | 202 |

| ERROR_HANDLER_CREATE          | 301 |

| ERROR_HANDLER_SET_READY       | 302 |

| ERROR_RAISE_APPLICATION_ERROR |     |

| ERROR_GET                     |     |

| PARTITION_SET_MODE            | 404 |

Table 3.1: System call IDs

- pok\_syscall1

- pok\_syscall2

- pok\_syscall3

- pok\_syscall4

- pok\_syscall5

- pok\_syscall6

- pok\_syscall7

- Thread:

- pok\_thread\_create: performs the THREAD\_CREATE system call which creates a thread with the specified identifier

- pok\_thread\_sleep: performs the THREAD\_SLEEP system call which makes the thread sleep for the specified amount of time

- pok\_thread\_start: performs the THREAD\_START system call which starts the specified thread

- pok\_thread\_wait\_infinite: alternative name for pok\_thread\_suspend

- pok\_thread\_period: performs the THREAD\_PERIOD system call which ends the current thread's period

- pok\_thread\_id: performs the THREAD\_ID system call which sets a value at a given location to the current thread identifier

- pok\_thread\_resume: performs the THREAD\_RESUME system call which resumes a thread given an id

- pok\_thread\_suspend\_other: performs the THREAD\_SUSPEND\_OTHER system call which suspends the specified thread

- pok\_thread\_suspend: performs the THREAD\_SUSPEND system call which suspends the current thread

- pok\_thread\_stop\_self: performs the THREAD\_STOP\_SELF system

call which stops the current thread

- pok\_thread\_stop: performs the THREAD\_STOP system call which stops the specified thread

- Time:

- pok\_time\_get: performs the GET\_TIME system call which returns a 64 bit value containing the current time

- pok\_time\_gettick: performs the GETTICK system call which returns the number of ticks since the system started

#### 3.3.2 Middleware Library

The functions contained in this layer implement most of the functionalities offered by the ARINC library but are not part of the ARINC653 specification. These functionalities should be used through ARINC library functions, accessing them directly results in a non-portable application.

#### • Blackboard:

- pok\_blackboard\_create: creates a blackboard data structure and associates an event to it

- pok\_blackboard\_read: reads a message from the blackboard, if the blackboard is empty the associated event is locked and the caller waits the specified timeout. When a message arrives or the timeout expires the event is unlocked

- pok\_blackboard\_display: displays a message in the blackboard and unlocks the associated event

- pok\_blackboard\_clear: empties the blackboard

- pok\_blackboard\_id: returns blackboard's identifier

- pok\_blackboard\_status: returns blackboard's status

- Buffer:

- pok\_buffer\_create: creates a buffer data structure and the associated events

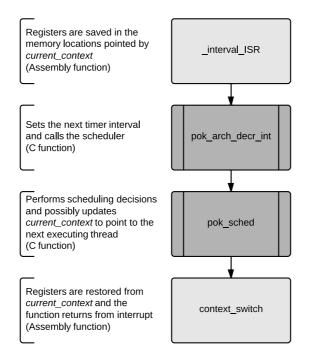

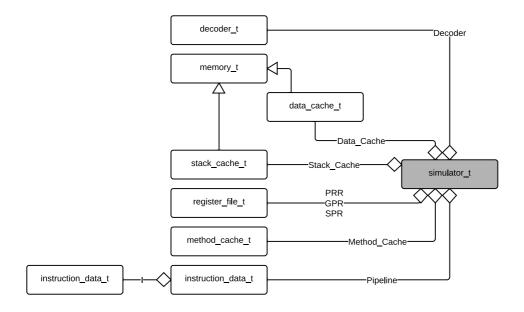

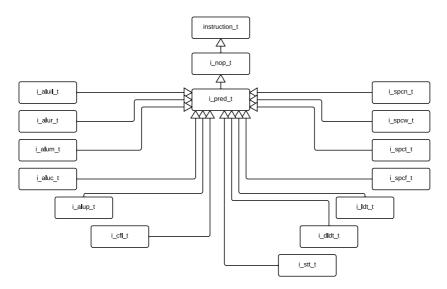

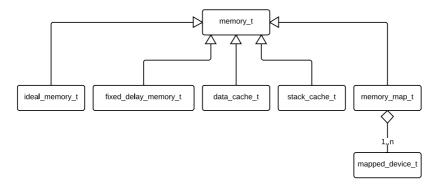

- pok\_buffer\_receive: reads a message from the buffer, if the buffer is empty the associated event is locked and the caller waits the specified timeout. If the buffer becomes empty the event is locked, if it becomes non-full the event is unlocked