# Programming of the T-CREST real-time multi-processor platform

Rasmus Bo Sørensen

Kongens Lyngby 2013 IMM-MSc-2013-5

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk IMM-MSc-2013-5

# Abstract (English)

The goal of this thesis is to integrate the T-CREST components into a tool chain for programming a multi-processor real-time platform. We present our view of the T-CREST tool chain, and we implement an initial tool chain, restricted by the current state of the T-CREST project. The T-CREST project is an ongoing research project supported by the European Union's 7th Framework Programme, aiming to develop a homogeneous time-predictable multi-processor platform. To integrate the components into a common tool chain, we define the interfaces between the components of the tool chain, and extend the components to implement the specified interfaces. With the intuition gain from integrating the components we propose extensions to improve performance or reduce cost. ii

# Resumé (Danish)

Målet for denne afhandling er at integrere T-CREST komponenterne ind i en værktøjskæde til programmering af en multi-processor sandtids platform. Vi præsenterer vores blik på T-CREST værktøjskæden, og vi implementerer en foreløbig værktøjskæde, begrænset af den nuværende tilstand af T-CREST projektet. T-CREST projektet er et igangværende forsknings projekt støttet af den Europæiske Unions 7. rammeprogram, hvis mål er at udvikle en homogen tidsforudsigelig multi-processor platform. For at integrere komponenterne ind i en fælles værktøjskæde, definerer vi grænsefladerne mellem komponenterne i værktøjskæden. Vi udvider komponenterne til at implementere de specificerede grænseflader. Med udgangspunkt i den intuition vi har vundet ved at integrere komponenterne, foreslår vi udvidelser for at forbedre ydeevne eller reducere omkostningerne.

iv

# Preface

This thesis was carried out at the Department of Informatics and Mathematical Modelling, at the Technical University of Denmark, in fulfillment of the requirements for acquiring an M.Sc. (Hons.) in Informatics.

During my master studies I was enrolled in the Honors program, at the Technical University of Denmark. The objective of the Honors program is to familiarize the student with research projects on an international level. During the main part of my studies, I have been participating in the early stages of the time-predictable multi-core architecture for embedded systems project (T-CREST), supported by the European Union's 7th Framework Programme. I have been taking part in the weekly project meetings, and most of the projects I have worked on during my master studies have been related to the T-CREST project. This thesis deals with the programming of the T-CREST platform. As a whole the thesis presents a first attempt at developing a coherent tool chain for software programming and hardware configuration of the T-CREST platform. The tool chain draws upon, and extends, several of the projects I have worked on during my master studies.

This thesis should be seen as a stand alone report on the early and first iteration of the tool chain for the T-CREST platform. The T-CREST processor and the T-CREST worst-case execution time (WCET) compiler are under development, and are not yet stable for integration. These components in the tool chain are therefore replaced with a stable processor and compiler. This compiler is not optimizing for WCET, and the thesis will therefore not go into details with WCET-aware compilation. I have concentrated on integrating the tools into the tool chain, to enable the developers of the T-CREST platform to test various ideas. vi

My work for this thesis has been carried out simultaneously with the first iteration of the T-CREST project. The uncertainty of when and which hardware components will become available, has proved an additional unforeseen challenge. I spent the first month of my thesis working on the S4NoC platform, before the T-CREST NoC platform was available. The work I did on the S4NoC platform is published in [1]. The S4NoC is only mentioned briefly in the thesis.

Lyngby, 07-December-2012

Rasmus Bo Sørensen

# Acknowledgements

I would like to thank my supervisor Jens Sparsø for all his great input to my work and my report, and my co-supervisor Martin Schoeberl for his comments and his advice on the JOP processor. Also I would like to thank the rest of the T-CREST members at the Technical University of Denmark for the good discussions we have had about the T-CREST project. Finally I would like to thank Mark Ruvald Pedersen, Lars Bo Sørensen, Tabita Niemann Kristensen and Madava Dilshan Vithanage for their sparring. viii

# Contents

| Al       | Abstract (English) |                                                   |          |  |  |

|----------|--------------------|---------------------------------------------------|----------|--|--|

| Re       | esum               | é (Danish)                                        | iii      |  |  |

| Pr       | Preface v          |                                                   |          |  |  |

| Ac       | cknov              | wledgements                                       | vii      |  |  |

| 1        | Intr               | oduction                                          | 1        |  |  |

| <b>2</b> | Bac                | kground                                           | <b>5</b> |  |  |

|          | 2.1                | Real-time systems                                 | 5        |  |  |

|          | 2.2                | Network-on-Chip                                   | 7        |  |  |

|          |                    | 2.2.1 Static routing in real-time Network-on-Chip | 9        |  |  |

|          |                    | 2.2.2 Source routing $\ldots$                     | 9        |  |  |

|          |                    | 2.2.3 Distributed routing                         | 9        |  |  |

|          | 2.3                | Message passing                                   | 10       |  |  |

| 3        | Тоо                | l chain                                           | 13       |  |  |

|          | 3.1                | Our tool chain                                    | 14       |  |  |

|          | 3.2                | The T-CREST tool chain                            | 16       |  |  |

| 4        | Har                | dware platforms                                   | 19       |  |  |

|          | 4.1                | Related work                                      | 19       |  |  |

|          | 4.2                | The S4NoC platform                                | 20       |  |  |

|          |                    | 4.2.1 Programming the platform                    | 21       |  |  |

|          | 4.3                | The T-CREST NoC platform                          | 22       |  |  |

|          |                    | 4.3.1 Configuration interface                     | 23       |  |  |

|          |                    | 4.3.2 Integration of the hardware platform        | 25       |  |  |

|              | $4.4 \\ 4.5$ | Storage of static routing information26Discussion30        |

|--------------|--------------|------------------------------------------------------------|

|              | 1.0          | 4.5.1Scheduling limitations304.5.2Backwards flow control31 |

| <b>5</b>     | TD           | M scheduler 33                                             |

|              | 5.1          | Related work                                               |

|              | 5.2          | Static routing                                             |

|              | 5.3          | All-to-all scheduling 35                                   |

|              | 5.4          | Application specific scheduling                            |

|              | 5.5          | Schedule converter                                         |

|              | 5.6          | WCET-aware compiler                                        |

|              | 5.7          | Discussion                                                 |

| 6            | Mes          | ssage passing interface 41                                 |

|              | 6.1          | Related work 41                                            |

|              | 6.2          | Communication primitives                                   |

|              | 6.3          | MPI in the T-CREST platform                                |

|              |              | 6.3.1 Address space                                        |

|              |              | 6.3.2 Communication primitives                             |

|              | 6.4          | Discussion                                                 |

|              |              | 6.4.1 Dynamic allocation of buffering space                |

|              |              | 6.4.2 Compiler optimizations                               |

| <b>7</b>     | Test         | t 49                                                       |

|              | 7.1          | Hello World! 49                                            |

|              | 7.2          | Microbenchmarks                                            |

| 8            | Cor          | nclusion 57                                                |

|              | 8.1          | Summary of findings                                        |

|              | 8.2          | Project contribution                                       |

|              | 8.3          | Future work                                                |

| $\mathbf{A}$ | S4N          | NoC paper 61                                               |

| в            | T-C          | CREST NoC source code 69                                   |

| $\mathbf{C}$ | JOI          | P infrastructure 93                                        |

| D            | тD           | M scheduler source code 111                                |

|              |              | I source code 133                                          |

|              |              |                                                            |

| H.           | Les          | t and benchmark source code 141                            |

### Bibliography

xi

### Chapter 1

# Introduction

This thesis is concerned with programming the T-CREST[2] real-time multi-processor platform.

The T-CREST research project is supported by the European Union and the goal of the T-CREST project is to develop a real-time multi-processor hardware platform in which all components (processors, interconnection network, and compiler) are designed to facilitate a predictable worst case execution time of the application executing on the platform. The T-CREST project creates a novel hard real-time multi-processor platform.

To program the T-CREST platform four tasks need to be performed in order:

- 1. Creation of a static schedule for the time-predictable interconnect.

- 2. Compilation of the source code.

- 3. Calculation of the worst-case execution time (WCET) of the application,

- 4. Configuration of the hardware platform.

The work of this thesis is carried out in close interaction with the T-CREST project. As we often need to describe details of the T-CREST work, it can be

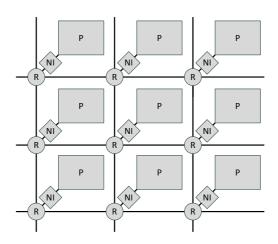

Figure 1.1: Conceptual view of the homogeneous multi-processor T-CREST platform with the three components, a processor (P), a network interface (NI) and a router (R).

confusing to the reader to distinguish our work from the work of T-CREST. We will refer to the work done in this thesis as "our *something*" or "we have *done*". The work of the T-CREST project will be referred to as "the T-CREST *component name*". When referring to this thesis we mean both the report and the work behind it.

In this thesis we integrate the T-CREST tools into a coherent tool chain. Our goal is to provide a tool chain that allows developers to investigate architectural features and flaws in the system. Our tool chain can help the developer to gain insight into the challenges of developing the T-CREST platform, and to improve the platform. Our tool chain will be a modular design, enabling individual testing of the modules and testing of the evolving T-CREST platform. Even though our tool chain is not the final T-CREST tool chain it can help avoid flaws in the final T-CREST platform. To support portability of applications between hardware revisions, a message passing interface (MPI) is needed.

A conceptual view of the homogeneous T-CREST hardware platform is shown in Figure 1.1; A regular grid of identical processors connected by a networkon-chip. The interconnect in the T-CREST platform is statically scheduled to achieve time-predictability. The static schedule is created by a scheduler at compile time. Each processor has a local memory to support message passing between processors. An application calls the MPI when it needs to communicate to another processor. The T-CREST platform was under development during the work of this thesis, so the requirement to align our work with the availability of the T-CREST components, had an impact on the topics to which we have contributed to. The following points describe the decisions we took to limit the scope of our work in this thesis.

- Allocation and mapping The bandwidth allocation and hardware mapping of an application could be found doing static analysis on the source code. In this thesis we assume the bandwidth allocation and hardware mapping for an application is supplied to the tool chain along with the application source code. The bandwidth allocation depends on the hardware mapping.

- **Code generation** The T-CREST processor Patmos[3] and its compiler is at the time of writing still unstable. In this project we use the stable JOP[4] processor with a compiler. As the processor we use is not the final T-CREST processor, we will in this thesis not be concerned with code generation for this processor. The final compiler should optimize worst-case paths and not average case paths as regular compilers do.

- Worst-case execution time analysis Analyzing the worst-case execution time (WCET) of an application is very dependent of the processor architecture. In this thesis we do not integrate WCET analysis in the tool chain, but we will make the tool chain ready for it.

- **Evaluation** The tool chain should enable the designers of the T-CREST tools and the hardware platform to evaluate them. It is difficult to evaluate each component in the tool chain without the whole tool chain. We create a modular tool chain where each module can be evaluated and optimized while decoupled from the other components. In this thesis we concentrate on functional evaluation.

**Contributions** In this thesis we have worked in three main areas of research; A time-predictable multi-processor platform, a time division multiplexing scheduler for routing traffic statically and a message passing interface. The contributions of this thesis are described in the following bullet points, along with an indication of in which chapter the given contribution is described.

- Proposal of interfaces between the T-CREST tools. [Chapter 3]

- An implementation and publication of the minimalistic time-predictable S4NoC[1] platform. [Chapter 4, Appendix A]

- Integration of the T-CREST NoC platform and the JOP processor. [Chapter 4]

- A theoretical comparison of the demand for storage bits in source routing and in distributed routing. [Chapter 4]

- Proposals of extensions to the T-CREST NoC platform. [Chapter 4]

- Extension of the TDM scheduler to integrate it into our tool chain. [Chapter 5]

- Proposal of an extension to the TDM scheduler reducing the worst-case latency in the static schedule. [Chapter 5]

- Implementation of an MPI for the T-CREST platform in Java. [Chapter 6]

- Proposal of improvements to the MPI to reduce the buffering space. [Chapter 6]

- The first working tool chain for programming our homogeneous multiprocessor platform. [Chapter 7]

This thesis consists of: An explanation of the main terms and concepts related to the T-CREST platform in Chapter 2. The tool chain and its components are outlined in Chapter 3. In Chapter 4 we present two hardware platforms, the S4NoC platform and the T-CREST Network-on-Chip platform and discuss improvements to the latter. In Chapter 5, a time division multiplexing (TDM) scheduler is presented and the implementations of its interaction with the WCET-aware compiler is described. Chapter 6 contains a discussion of which communication primitives to implement in the MPI library and a description of the implementation. A test of our tool chain and hardware platform is presented in Chapter 7. A conclusion of the project is given in Chapter 8. The related work is presented in the beginning of the chapters it relates to. The source code we have written or changed is shown in the appendices, and in the beginning of each appendix we have written a short explanation of what we have done. The source files are also available online at http://rbscloud.dk/sourcecode.zip. We reference the appendices from where it is relevant.

## Chapter 2

# Background

In this chapter we introduce the main topics of our project: real-time systems, network-on-chip and message passing.

### 2.1 Real-time systems

There are basically two different kinds of real-time systems; soft real-time and hard real-time. Soft real-time systems may miss a deadline once in a while and is typically applied in non-safety critical systems, such as TV set-top boxes or other streaming applications. Hard real-time requires all timing requirements to be met at all times, and is typically applied in safety-critical systems, such as aviation and train-control systems. The systems addressed in this thesis belong to the hard real-time category. Implementing hardware for real-time systems requires that the hardware is time-predictable and analyzable.

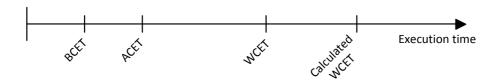

In Figure 2.1 we show how the different run times of a program relate to each other on the time axis. Due to different inputs to the program, the execution time can vary. Also a varying system state before and during the execution can vary the execution time of the program. A varying system state can be the state of the caches and the state of other programs running in parallel. The

Figure 2.1: Relating the best-case execution time (BCET), the avaragecase execution time (ACET), the worst-case execution time (WCET)and the calculated WCET.

shortest possible execution time is called the best-case execution time (BCET), which is generally not interesting in any kind of computer systems. The average execution time when the program is executed multiple times is called the average-case execution time (ACET), which in general purpose systems is regarded as the performance of a program. The longest possible execution time of the program is called the worst-case execution time (WCET). The WCET is reached when the system receives the worst-case input in the worst-case system state. The performance of a real-time system is equal to the WCET of the given application.

The WCET is found by analyzing the application together with the hardware platform. To find the actual WCET all possible inputs and systems states must be analyzed. An exhaustive analysis is usually not feasible, and in that case a pessimistic estimate of the WCET can be calculated. Depending on the complexity of the systems, the calculated WCET might be far from the actual WCET. The gap between the calculated WCET and the actual WCET can be minimized by using a more accurate model or by making the hardware easier to predict. A more accurate model results in a more complicated WCET analysis. The calculated WCET is regarded as the system performance in realtime systems. More accurate WCET models may result in tighter and lower WCET bounds, but will increase the complexity of the calculation. In parallel real-time systems the WCET analysis is known to be difficult, maybe even impossible. The T-CREST project addresses analysability in parallel real-time systems. The hardware for real-time systems must be deterministic. If the hardware is non-deterministic the analysis must always rely on worst-case latencies. The worst-case in non-deterministic systems might not even be bounded making the analysis impossible.

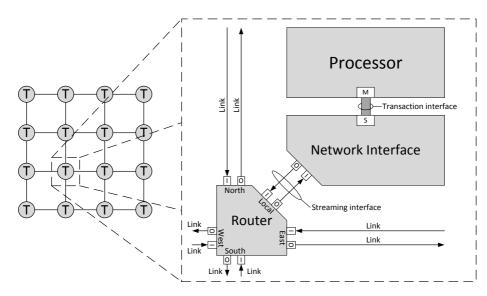

Figure 2.2: The basic Network-on-Chip component a tile (T) contains: A router, a network interface and a processor. The interface between the processor and the network interface is a transaction based master slave interface, and the interface between the network interface and the router is a streaming interface.

### 2.2 Network-on-Chip

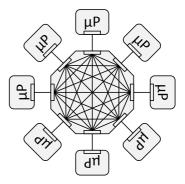

A Network-on-Chip (NoC) is a type of interconnect supporting many communicating nodes. The basic component of a multi-processor platform with a NoC interconnect is illustrated in Figure 2.2. There are two main types of components in a NoC: routers and network interfaces. The processing cores connected to a NoC are each connected through a network interface to the network of routers. In this structured design we group a processor, a network interface and a router into a Tile. The connections between routers are called links. To ease the understanding when describing the ports of a router the ports are usually named after the corners of the world. So the north port of one router is connected to the south port of the router "above".

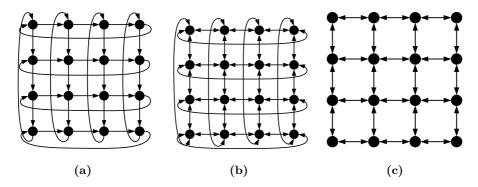

These routers can be connected in many different topologies. In this thesis we will only concentrate on grid topologies, such as torus, bidirectional-torus (bitorus) and mesh shown in Figure 2.3. In network-on-chip there are no general restrictions on the topology of the network of routers. The network of routers consists of the routers and the links between them. The links are just wires, but as the wires can be very long they can infer a considerable latency in the path.

Figure 2.3: The grid topologies relevant to this thesis: (a) a torus network, (b) a bidirectional-torus network and (c) a mesh network.

To increase the clock frequency the links can be pipelined, which increases the amount of buffering in the network. When packets are sent through the network they are chopped into smaller pieces. The smallest amount of data that the network enforces flow control on is called a flit and each flit can be divided into smaller chunks called phits. The phits are the smallest physical data units transmitted over a link, usually equal to the link width.

The basic functionality of the router is very simple. When the router receives a flit on an input port, the router decides to which output port it is sent. Implementing the logic to make routing decisions dynamically can be a complex problem, because the hardware has to ensure that no deadlocks can happen, and that all packets are routed to their destination. Dynamic routing can be implemented in many different ways. In the T-CREST project all routing decisions are made statically. This simplifies the hardware as well as the WCET analysis, because the latency is known in advance. The router implementation scales quite well, as the number of ports stay constant when the size of the whole systems grows.

The basic functionality of the NI, is to convert the transactional requests from a processing core, to the streaming interface of the network. The detailed functionality of the NI depends very much on the routing scheme in the network. The scalability issues of Network-on-Chip are most dominant in the NI. This is where the hardware needs to consider all cores that it is communicating with.

#### 2.2.1 Static routing in real-time Network-on-Chip

Static routing is applied and enforced in such a way that the communication behavior of one processor cannot affect the communication of other processors. Making the scheduler responsible of avoiding colliding flits, allows the hardware to be very simple and efficient. Deciding the routes statically is done by dividing access to the transmission medium in time. This approach is called time division multiplexing (TDM). Only one communication channel must be scheduled on a link in a given time slot. The scheduling of communication channels in the network is done at compile time, before the WCET analysis.

If the communication behavior of one processor can affect the communication behavior of another processor, the WCET will increase dramatically. If for example a real-time system runs on a general purpose platform, the communication between one pair of communicating processors can interfere with the communication of another pair of communication processors. In this case the WCET analysis will have to assume the worst-case of interfering communication, this will increase the WCET estimate by orders of magnitude.

#### 2.2.2 Source routing

The static route of a flit is stored in the flit header. The route in the flit header is read on its way through the network. The sending NI needs to store a route for each time slot and the destination ID of that route. When a flit reaches a router, the router reads the header to determine whereto the incoming flit should be routed. The receiving NI can see the origin of a flit in its header.

#### 2.2.3 Distributed routing

In distributed routing the static routing information is distributed to the routers where it is needed. This implies that the flits does not need a header, which increases the bandwidth. The sending NI stores an entry table with the destination ID of the flit that is allowed to enter the network in the given time slot. The router stores how its input ports are connected to its output ports in each time slot. The receiving NI stores an exit table with the source ID of the flits which can arrive from the network in the given time slot.

### 2.3 Message passing

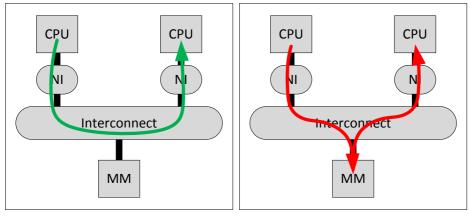

Message passing is a way of communicating between tasks, as opposed to shared memory communication. The conceptual difference of communicating with message passing and shared memory in multi-processor systems is illustrated in Figure 2.4.

Figure 2.4: Conceptual illustration of message passing and shared memory communication. (a) With message passing the processors (CPU) communicate directly through the network interface (NI) and the interconnect. (b) With shared memory communication the communication goes through the main memory (MM).

Message passing is when a packet of data is sent directly from one processing core to another. When tasks are being executed on different processors, which have no locally shared memory, a message can be sent to the other processor through the interconnect. Data that is transported via message passing must only reside in the local memory of the processor or the internal registers of the processor. Message passing is a benefit when the data is transferred directly from one local memory to another local memory. It is only allowed to write the data to the main memory once, when it should not be used any longer. Thus applications with a high level of interprocessor communication, such as streaming applications, are well suited for message passing architectures.

Shared memory is widely used in many kinds of computer systems today. Communicating between processing cores using shared memory the data will go through the main memory, or a lower level cache, which adds additional complexity due to cache coherency. Message passing can increase the bandwidth and lower the latency of interprocessor communication compared to shared memory communication. Some systems will have both the possibility of message passing and shared memory communication. When the local on-chip memory is no longer sufficient, the off-chip main memory will come in to play.

### Chapter 3

# **Tool chain**

In this chapter we present two tool chains. The first tool chain is the tool chain we have implemented, we refer to this tool chain as our tool chain. The second tool chain is how we imagine the final version of the T-CREST tools will work together, we refer to this tool chain simply as the T-CREST tool chain. Our tool chain is slightly different from the T-CREST tool chain because not all the T-CREST tools are at a stable state.

The component based structure of the tool chains helps the integration and testing of new components. Each component can be replaced, by a component with the same interfaces. The T-CREST project dictates that the tool chain should be compatible with multi-processor platforms using TDM in the interconnect.

In the T-CREST platform, the interprocessor communication and the communication to the main memory are decoupled because there is a dedicated interconnect for each of the two communication types. The NoC is only used for interprocessor communication, in the form of message passing. Managing the main memory and the caches is all done by the compiler, therefore we have not focused on main memory access, as the compiler is out of the scope of this thesis. In the following section, we describe how our tool chain is implemented, and in the next section we describe how the implementation the T-CREST tool chain differs.

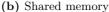

Figure 3.1: An illustration of our tool chain programmed in Java.

### **3.1** Our tool chain

A block diagram of our tool chain is shown in Figure 3.1. The arrows between blocks are the flow of data, and the labels on the arrows are the file formats of the interfaces. The diamond shapes are inputs to the tool chain, describing the application and its requirements. The elliptic shape is a platform specific library, mapping an abstract application interface to the given hardware platform. The rectangular shapes are the tools in the tool chain. The tool chain takes source code and a bandwidth graph as inputs. The source code describes the desired application, and the bandwidth graph describes the bandwidth requirements between all processing cores and the topology of the NoC.

First, the schedule is generated by the TDM scheduler. Then the schedule converter converts the schedule to either hardware or software tables, depending on the hardware platform. The compiler then compiles the application source code along with the MPI (message passing interface) and possibly the software tables. In the end the application is loaded on to the hardware platform. Loading the application onto the hardware, can be done before or after synthesis depending on the hardware platform. Since we use the Java programmed JOP processor,

we also use the JOP compiler.

The mapping between processes and processors are done by the application programmer. The mapping is specified in the source code and in the input to the TDM scheduler. The input to the TDM scheduler is an XML formated file, describing the topology of the network-on-chip and the communication pattern of the application. We use XML because it is human readable, flexible and expendable. An example of the XML input format can be seen in Listing 3.1. In the example a **bitorus** topology is specified, other possible topology types are the **mesh** type and **arbitrary** type. If a **arbitrary** topology is specified, each link in the topology must be specified inside the **graph** tag using a link tag. When **bitorus** or **mesh** is specified the **link** tags are ignored. The TDM scheduler schedules the specified traffic in the topology graph. The amount of traffic scheduled between two nodes in the NoC is specified in the **bandwidth** attribute of the **channel** tag in the input XML file.

Besides the schedule, the TDM scheduler also calculates the worst-case latency (WCL) of each communication channel. The WCL of a communication channel is the worst-case time separation in time slots between access to two communication paths. If the scheduled latencies are not sufficient to meet a given real-time deadline, re-scheduling with a different bandwidth specification could decrease the WCL. The output of the scheduler is an XML file. This XML file describes how the router and network interface of each tile should be configured in every time slot and the WCL of each communication channel. An example of the output XML file can be seen in Listing 3.2, specifying a schedule of length 9. The data is separated into tiles, and in a tile each time slot describes the NI and the router. In each tile the WCL for each destination is specified.

Our MPI implements the communication primitives. The MPI hides all the

**Listing 3.2:** XML example of the scheduled communication channels in a 3 by 3 bitorus.

```

<?xml version="1.0"?>

<schedule length="9">

<tile id="(2,0)">

3

<timeslot value="0">

<ni rx="(2,1)" tx="(1,1)" />

<router>

<output id="N" input="D" />

7

<output id="S" input="D"</pre>

/>

<output id="E" input="L"</pre>

/>

9

<output id="W" input="D" />

<output id="L" input="S" />

</router>

</timeslot>

<latency>

<destination id="(0,0)" WCL="8"

/>

<destination id="(1,0)" WCI="8" />

<destination id="(0,2)" WCL="8" />

19

</latency>

</tile>

</schedule>

```

hardware specific implementation details of the communication primitives from the application programmer. In this case of embedded real-time systems, the MPI could just as well be called the communication driver. If the hardware is changed, the driver also needs to be changed, but the application source code will not have to be changed. The WCET-aware compiler compiles and analyzes the application source code, along with the MPI library, and the timing information from the TDM scheduler.

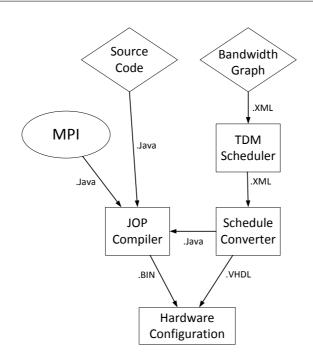

### 3.2 The T-CREST tool chain

A block diagram of the T-CREST tool chain is shown in Figure 3.2. The difference from our tool chain is the programming language and the WCET-aware compiler. The T-CREST platform is programmed in C and the WCET-aware compiler optimizes the worst-case execution path in the control flow graph (CFG) instead of the average-case execution path. The WCET-aware compiler uses the information from the TDM scheduler to find the worst-case execution path.

Figure 3.2: An illustration of how we imagine the T-CREST tool chain.

### Chapter 4

### Hardware platforms

In this chapter we present two hardware platforms and a theoretical comparison of methods to store static routing information. The current state-of-the-art real-time NoC platforms, presented in the related work section, are complex hardware devices. The first platform we present is the S4NoC platform, it is an attempt to design a minimalistic hardware platform. We made this minimalistic NoC to gain intuition on how simple a NoC can be, and as the first hardware platform for our tool chain. The second hardware platform is the first version of the T-CREST platform.

### 4.1 Related work

Network-on-chip has been an active research area for many years, in this project we need time-predictability to enforce real-time. The following NoC platforms provide time-predictability.

Æthereal lite The Æthereal[5] NoC was developed at Philips. Æthereal provides guaranteed service and best-effort traffic. Guaranteed service is provided using TDM. A lite version of Æthereal called aelite has been developed only

providing guaranteed service. aelite is an application specific NoC, which can be instantiated in a topology that fits to the application. The Æthereal design flow is proprietary and application specific. The hardware generation and mapping is carried out in one step. Several versions of Æthereal has been made, some using source routing and others using distributed routing.

**Mango** The MANGO[6] NoC was developed at the Technical University of Denmark. MANGO is an asynchronous NoC with delay insensitive links. MANGO provides both best effort traffic and guaranteed service. The guaranteed service is provided using virtual channels and rate control, opposed to TDM.

**Nostrum** The Nostrum[7] NoC was developed at the Royal Institute of Technology in Sweden. Nostrum implements guaranteed service with their concept of looped container, which are statically scheduled containers looping in the network. A flit can be sent via a looped container to its destination.

### 4.2 The S4NoC platform

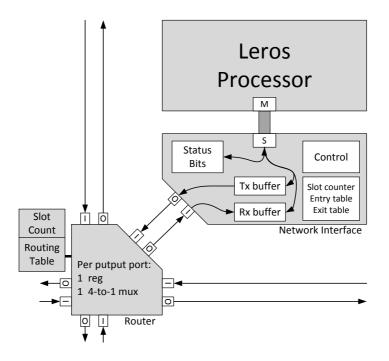

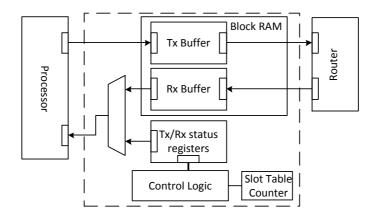

The S4NoC<sup>1</sup> [8, 1] is a light-weight time-predictable NoC using distributed routing. The paper we wrote about the S4NoC is presented in Appendix A. To enable time-predictability the S4NoC implements TDM. The S4NoC consists of a very simple router and network interface(NI). We show a 64 core FPGA implementation of the S4NoC connected to Leros processors in [1]. The Leros processor is presented in [9]. Leros is an accumulator machine programmed in assembler or in Java. A block diagram of an S4NoC tile is shown in Figure 4.1. The router is very simple, containing one slot counter, one slot table and 5 output ports. One output port is a register and a 4-to-1 multiplexer. The NI has one word queues for each communication channel in and out of the node. These are placed in the RX and TX buffers, implemented in block RAM. The processor can read and write single words to the RX and TX buffers. Status registers indicate when words are sent and received, these status registers can also be accessed by the processor. The limited buffering makes this platform hard to program in such that the full bandwidth is utilized for all communication channels.

$<sup>^1{\</sup>rm The~S4NoC}$  is open source and is publicly available at <code>https://github.com/t-crest/s4noc</code>.

Figure 4.1: Block diagram of the S4NoC. The Leros processor can read the status bits, write the Tx buffer and read the Rx buffer.

#### 4.2.1 Programming the platform

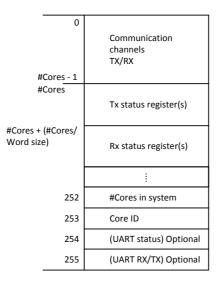

The Leros processors run from a local instruction ROM, no code can be loaded into it at run time. The NI is connected through the 8 bit I/O address space of Leros. Figure 4.2 shows the address space of the NI connected to Leros. The communication channel to and from each other processor in the system is mapped to the address matching its core ID. Writing to that address sends a data word to the given core, reading from the address receives a data word from the given core. The status registers indicate the receive and transmit status of each communication channel, on a word level. Flow control on a higher level than single data words needs to be implemented by the processor. The upper addresses of the address space are for the UART, the CPU ID and the total number of cores in the system.

To synchronize with the TDM slots, the NI has a counter, an entry table and an exit table, dictating when and which packets enter or exit the network. The router has a routing table dictating which input port should be routed to which

Figure 4.2: The address space of the S4NoC NI connected to the I/O address space of the Leros processor.

output ports. The tables in the NI and the router are ROMs, which in an FPGA implementation can be implemented in look-up-tables (LUTs). These tables are generated at design time, and the whole design has to be re-synthesized to change the tables. The S4NoC tables can be generated by our application specific TDM scheduler.

### 4.3 The T-CREST NoC platform

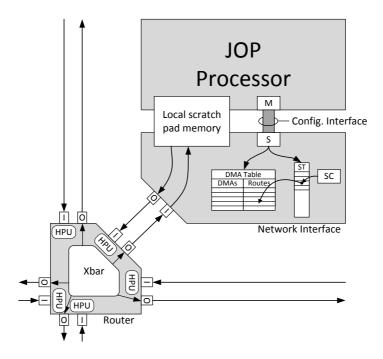

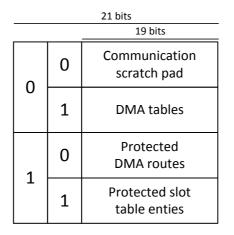

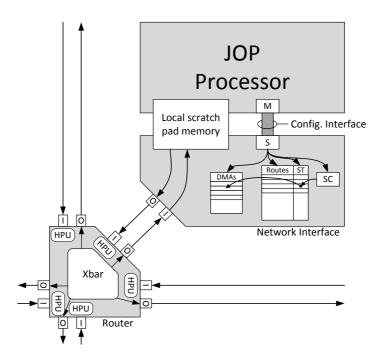

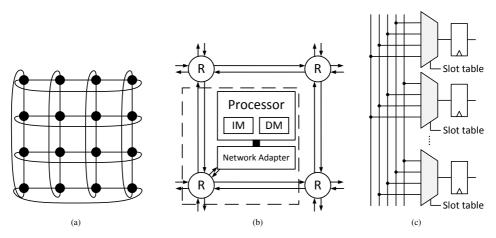

The T-CREST NoC, presented in [10], is a time-predictable interconnect using source routing. A block diagram of the T-CREST NI and router connected to the JOP processor can be seen in Figure 4.3. The T-CREST NoC uses direct memory accesses (DMA) to move data form one processor the another. To utilize as much of the bandwidth as possible several DMAs can be interleaved, each waiting for their time slot. This enables utilization of time slots from different communication channels at the same time. Controlling these interleaved DMAs is the core function of the NI. The interleaved DMA controller moves data from its local scratch pad to the local scratch pads of other processors. The local scratch pad memory is a dual ported memory, with one port connected to the processor, and one port connected to the NI. The individual DMA transfers are stored in a DMA table along with the route to the destination. To keep the

Figure 4.3: A block diagram of the DMA NoC. In the router, each input port is connected to a header parsing unit (HPU), each output port is connected to the crossbar (Xbar). The JOP processor can access the data in the local scratch pad memory and configure the slot tables (ST) and the DMA table in the NI.

synchronization with the TDM slots, a slot table is indexed by the slot counter. The slot table indexes into the DMA table. When a flit is sent from the NI, its route is stored in the flit header, along with the write pointer. The router needs to decode the header of a flit before it routes the flit to a output port. The decoding of the flit header is done in the header parsing unit (HPU) in the router. The flits are sent to the crossbar and multiplexed to the output port.

#### 4.3.1 Configuration interface

The configuration of the DMA table, and the slot table, is carried out by the processor. Before the processor can send any packets through the NoC, the processor has to configure the slot table and the routes in the DMA table. The first operation is to write the routes of each DMA entry to the DMA table.

Figure 4.4: The local address space for each processor in the system. The 21 st bit is the protection bit, indicating whether to access the protected part of the local address space or not. The protected part of the address space is only for configuration of the TDM schedule.

Then it is written in each entry of the slot table, which DMA is allowed to send in that given time slot.

There are 4 segments in the local address space of each processor, the scratch pad, the DMA tables, the protected DMA routes, and the protected slot table. The number of accessible addresses in the 4 segments of the address space are not constant, nor is the ratio between them, this is because they vary depending on the current system configuration. We decide to make the simple division of the address space as seen in Figure 4.4. This is a flexible solution, but it wasts address space. The most significant bit of the 21 bits of the address space is the protection bit. The part of the address space addressed with the protection bit, should only be changed during the configuration phase of the NI.

The task of configuring the NI is done in software. Each processor needs access to the configuration data for the TDM schedule. To give access, we write the configuration data in static arrays, and compile it along with the application source code.

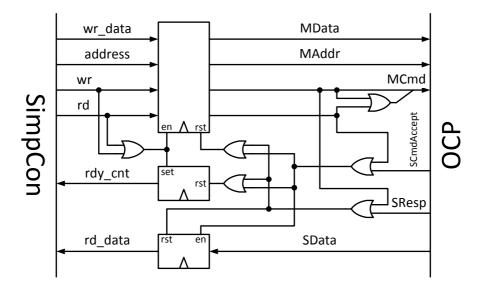

Figure 4.5: Conversion from SimpCon to OCP. The reset (rst), set and enable (en) are all synchronous signals. The circuit adds 2 clock cycles of latency to a request. The latency can be removed by adding multiplexers to bypass the registers, delivering stable signals one clock cycle earlier in each direction.

#### 4.3.2 Integration of the hardware platform

The T-CREST processor Patmos[3] was not in a stable state at the time we were ready for integration into our tool chain. To ease our work of integrating all these alpha state components, we decided to use the well tested JOP[4] processor, with good support. The JOP processor has a SimpCon[11] interface, whereas the T-CREST NoC has a simple subset of the open core protocol (OCP)[12] interface, thus some conversion is needed. To integrate the JOP<sup>2</sup> processors and the T-CREST NoC<sup>3</sup> platform we have wrapped the NoC in an array of SimpCon interfaces. The wrapped NoC is then instantiated in the JOP top level and connected to the JOP processors. The source files we have written and changed for wrapping the T-CREST NoC platform in SimpCon interfaces can be seen in Appendix B. These files also include a testbench for the NoC wrapped in SimpCon interfaces. The source files we have changed to connect the JOP processors and the T-CREST NoC platform can be seen in Appendix C.

<sup>&</sup>lt;sup>2</sup>The JOP processor is open source and is publicly available at https://github.com/jop-devel/jop.

<sup>&</sup>lt;sup>3</sup>The T-CREST NoC platform is open source and is publicly available at https://github.com/t-crest/t-crest-noc.

A diagram of the conversion between the SimpCon and the OCP interfaces can be seen in Figure 4.5. The SimpCon interface supports pipelined accesses, it holds the master signals stable for one clock cycle and waits for the rdy\_cnt to be 0. The reply data of the SimpCon interface is expected to be stable until the next request is started. The OCP interface needs the master signals to be stable until the slave acknowledges the request. The reply data of the OCP interface is high in one clock cycle. The incompatibilities of the SimpCon interface and the OCP interface adds 2 clock cycles of extra latency to a request. The latency can be removed by adding multiplexers to bypass the registers. These bypass multiplexers should be controlled by the enable signals, and would deliver stable signal one clock cycle earlier. Since the final T-CREST processor has an OCP interface we have focused on getting this preliminary platform to work, and not to optimize it.

### 4.4 Storage of static routing information

Through our work with the hardware platforms described in this chapter and the TDM scheduler, we have made two observations:

- Storage of the static routing information is a considerable part of the total resource consumption, this can be seen in [1] for the S4NoC and in [10] for the T-CREST NoC platform.

- The port configurations of the router in distributed routing stores redundant information.

The first observation has made us interested in optimizing the second observation. The following comparison, has not been verified in an implementation, but is a theoretical comparison, which could be the target for future T-CREST experiments. In the literature there are several methods to compress routing tables, such as [13] and [14]. These methods does not work in TDM NoCs. In [14] it is described how static routing tables are compressed, this kind of static routing means that the path of a flit is static, but not the arrival time as in our TDM NoCs. We have not found any compression methods in the literature that works for TDM NoCs. We compare the required storage bits for source routing, distributed routing and compressed distributed routing. A summary of the storage bits for each routing method is shown in Table 4.1

**Storage bits in source routing** In source routing one node in the network needs to store a route and a destination ID in each time slot. The number

of storage bits for storing a route depends on the size of the network, in the T-CREST platform 2 bits are used for each hop in the network. The route can be stored in  $\lceil \log_2(2 \times H) \rceil$  bits, where H is the maximum number of hops between two processors in the network.

Storage bits in distributed routing In distributed routing one node in the network needs to store a destination ID, a source ID and the router configuration in each time slot. An ID of a processor can be stored in  $\lceil \log_2(N) \rceil$  bits, where N is the number of CPUs in the system. The common way of storing the router configuration in a time slot is to store 2 bits for each output port per time slot. The 2 bits describe which one of the 4 possible input ports is connected to the given output port. With 5 ports this is 10 bits, which is 1024 possible combinations, not all these combinations are valid.

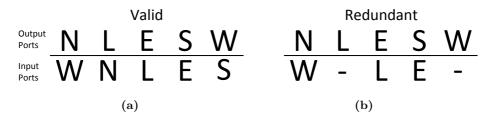

**Compressing the distributed routing tables** The distributed routing tables can be compressed because there are not 1024 possible router configurations. A router configuration can be perceived as a permutation of the 5 input ports, connected to the 5 output ports. An example of a port permutation is shown in Figure 4.6a. The sequence of the output ports is static and the sequence of the input ports change. In the following we calculate the number of valid port permutations.

In the actual system there are 3 restrictions on the router configurations:

- 1. No output port must be connected to multiple input ports.

- 2. No input port must be connected to multiple output ports.

- 3. No incoming flit must be routed out the same direction that it arrived, e.g., a flit arriving at the south input port must not depart from the south output port.

The first and second restriction implies that a valid router configuration must be a permutation of the 5 distinct input ports, such a valid router configuration can be seen in Figure 4.6a. We call a router configuration a port permutation.

The third restriction implies that if an input port is connected to the output port in the same direction it is considered as unconnected.

A port permutation where two or more ports are unconnected is is redundant because it can be represented by a permutation where the ports are swapped, i.e.,

Figure 4.6: Router configurations, perceived as permutations of the 5 input ports. (a) is a valid port permutations and (b) is a redundant port permutation because it can be represented by (b)

the port permutation in Figure 4.6b can be represented by the port permutation in Figure 4.6a. The static schedule guarantees that no flit is routed through the ports that are swapped.

In combinatorics a port permutation with no unconnected ports is called a derangement, and a permutation with one unconnected port is called a partial derangement with one fixed point. We call the number of all valid port permutations V. V can be stored in  $\lceil \log_2(V) \rceil$  bits. V is found using equation 4.1, the general formula is shown in [15].

$$V = D_{5,0} + D_{5,1} = \left[\frac{5!}{e}\right] + {\binom{5}{1}} \cdot \left[\frac{4!}{e}\right] = 89$$

(4.1)

Where  $D_{5,0}$  is the number of derangements of 5 elements, and  $D_{5,1}$  is the number of derangements of 5 elements with one fixed point. The number of bits to store the router configuration in one time slot is:

$$\lceil \log_2(\mathbf{V}) \rceil = \lceil \log_2(89) \rceil = 7 \tag{4.2}$$

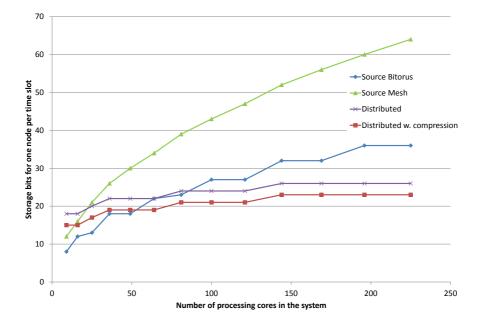

**Comparing the storage of the routing methods** A summary of the storage bits for distributed routing and source routing is shown in Table 4.1.

Table 4.1: Storage bits per time slot per core for source routing (Src), distributed routing (Dist) and distributed routing with compression (Dist w/comp).

|             | NI ID (Bit)                                 | NI Route (Bit)                     | Router (Bit) |

|-------------|---------------------------------------------|------------------------------------|--------------|

| Src         | $\lceil \log_2(N) \rceil$                   | $\lceil \log_2(2 \times H) \rceil$ | _            |

| Dist        | $2 \times \lceil \log_2(\mathbf{N}) \rceil$ | _                                  | 10           |

| Dist w/comp | $2 \times \lceil \log_2(N) \rceil$          | _                                  | 7            |

Figure 4.7: The number of storage bits for one node per time slot for source routing in a bitorus and in a mesh, and distributed routing with and without compression, as a function of network size. The storage requirements for distributed routing is the same for bitorus and mesh.

In Figure 4.7 we show the storage requirements for distributed routing and source routing as a function of the network size. The number of storage bits with source routing in a mesh network scales very poorly compared to the other routing methods. Using source routing in a bitorus scales better, due to a smaller maximum distance of two nodes in a bitorus network. The storage requirements in distributed routing is invariant for the bitorus topology and the mesh topology. The difference is in the number of time slots needed. The number of time slots when routing in a bitorus is smaller than routing the same communication pattern in a mesh topology. As can be seen in Figure 4.7, distributed routing with compression is the most efficient way in terms of storage bits for networks as small as 64 nodes. In the case of 36 and 49 nodes it can be argued that the increase in bandwidth due to distributed routing makes distributed routing with compression the most efficient routing method. This only comes at the expense of one more storage bit per time slot for each network node.

One could argue that it is not a fair comparison, because the source routing information could also be compressed. The problem with compressing the source routing information is that it adds latency through a router. The router can not start decompressing the route before the flit arrives, whereas the decompression of the router configuration with distributed routing can be pipelined.

Compressed distributed routing requires less storage bits, the decompression adds no latency to the routing, and the bandwidth is higher because no header is sent through the network.

#### 4.5 Discussion

In this section we discuss the current limitations of the T-CREST platform, and we propose possibilities to avoid these limitations.

#### 4.5.1 Scheduling limitations

We have found two limitations of the current T-CREST NoC platform that limit the schedules:

- The platform does not support TDM schedules where one communication channel can send in multiple time slots on different routes.

- The platform only allows for reconfigurable schedule period lengths, at synthesis.

The first limitation adds another restriction to the scheduler, this additional restriction can increase the TDM period. At this point the T-CREST NoC platform, together with the TDM scheduler we are using, only supports schedules where each communication channel has a bandwidth of one time slot per schedule period. The second limitation requires to re-synthesis to change the schedule period. For larger systems synthesis can be very time consuming, and in an ASIC, which is the target for the T-CREST project even impossible.

A block diagram of a redesigned version of the T-CREST hardware platform can be seen in Figure 4.8. To resolve the mentioned restrictions we propose to extend the architecture by moving the routes out of the DMA table, and into the slot table. The packets of a communication channel can be routed on different

Figure 4.8: Extended block diagram of the DMA noc NI. The JOP processor can access data in the scratch pad memory, and configure the slot counter (SC), the slot table (ST) and the routes.

paths in each time slot of a schedule period. This extension requires more configuration storage, but is more flexible and can decrease the TDM period. One slot entry and one route can be written in the same configuration write, reducing the configuration time. Also the size of the static array is reduced, because the two values can be saved in the same 32 bit integer. We propose to make the TDM period configurable in run time to support variable length TDM schedules at run time. This can be supported by extending the counter to have a variable reset, configured along with the slot table.

#### 4.5.2 Backwards flow control

In the current T-CREST NoC platform there is no backward flow control. In real-time systems where performance is analyzed, we can guarantee that tokens can be consumed at a certain rate. As long as this rate is higher than the rate at which tokens are produced there are no problems. The problem arises during application development. The developer might not want to analyze the prototype because it takes time, or might need to lower the speed with debugging info. In these cases backwards flow control can ease development. The backwards flow control can be implemented in hardware or software. In hardware the backwards flow control can be implemented by sending empty tokens back when a place in the receiving buffer is freed by software. These empty tokens can be sent back as a specially formatted package that is processed by the NI. In software the backwards flow control can be implemented by sending a normal message back to a special address that the software in the other end is polling when it tries to send. Analyzing the systems with backwards flow control might be difficult, so backwards flow control should not be used when the application is analyzed.

# Chapter 5

# **TDM** scheduler

In this chapter we describe the scheduling problem and two types of schedulers. We also describe how we integrate an application specific scheduler into our tool chain.

### 5.1 Related work

The scheduling problem that the TDM scheduler needs to solve, is known as a integer multi-commodity flow problem. This problem has been proven to be NP-hard in [16]. A scheduler for scheduling all-to-all communication in these kinds of networks is shown in [17]. The advantage of this scheduler is that the schedules are symmetric, meaning that the routing tables for each router are the same, allowing for resource sharing. A scheduler for the Æthereal is shown in [18]. This scheduler schedules in two phases, the first phase is path allocation and the second is time slot allocation to TDM slots. The Æthereal scheduler instantiates extra hardware to increase the capacity on links if needed. Our tool chain needs a scheduler for scheduling application specific communication requirements on to the homogeneous T-CREST NoC platform.

## 5.2 Static routing

In the TDM interconnect we route packets statically, to guarantee that no packets collide. This guarantee enables us to make very simple hardware, with no arbitration mechanism or buffering. We need a TDM scheduler to create virtual end-to-end circuits. The interconnect in the T-CREST platform is a timepredictable TDM NoC. Time-predictability in the TDM NoC is enforced by a static routing. In the following we define the routing terms.

A static routing is a mapping of communication channels to the TDM links fulfilling the specification. This mapping is performed by a TDM scheduler. The communication channels are specified by the application.

**Definition 5.1** The communication channel from a to b is a collection of communication paths which can route data from a to b.

The TDM scheduler finds a collection of communication paths that satisfy the specification of the communication channels. The bandwidth of a communication channel is the number of communication paths in the communication channel, divided by the schedule period.

**Definition 5.2** A communication path from a to b, is a sequence of neighboring links mapped to consecutive time slots. This sequence starts in a and ends in b.

A valid communication path is mapped to one of the shortest paths from a to b. In regular topologies the length of a valid communication path is equal to the Manhattan distance from a to b.

**Definition 5.3** The schedule period is equal to the length of the complete schedule in time slots. The complete schedule is a schedule that satisfies all communication channels given in the application requirements.

The requirements to a schedule is specified in the XML input of the TDM scheduler. It is specified which communication channels the application needs and the bandwidth for each communication channel. When the application developer needs a schedule for an application, the developer specifies the platform topology and the communication channels in the XML input. There are two types of schedules, there is the all-to-all schedule and the application specific schedule.

### 5.3 All-to-all scheduling

An all-to-all schedule is a schedule where all processors in the network can communicate directly to all other processors in the network with equal bandwidth. All-to-all schedules have advantages and disadvantages. It is an advantage that the schedule is application independent, and there is only need to configure the schedule once, and it can be implemented in hardware. For small networks the latency of an all-to-all schedule is quite small, and it is more likely that all processors need to communicate to all other processors. The all-to-all schedule is ideal in systems where the communication pattern is very uniform between all processors. It could also be an advantage to use the all-to-all schedule when prototyping a system, as long as the developer is testing functionality and not runtime requirements. An all-to-all scheduler is shown in [8], the advantage of this approach is that the schedule for each router is the same, allowing for resource sharing, and the generated all-to-all schedules are close to optimal in terms of a short schedule period.

In large networks the number of processors each processor talks to is very dependent on the application, therefore an all-to-all schedule might wast a considerable amount of bandwidth. In systems with low latency requirements or high bandwidth requirements, an application specific schedule should be calculated.

#### 5.4 Application specific scheduling

An application specific schedule is a schedule where only processors that are specified to communicate can communicate. Creating an application specific schedule can lower the schedule period compared to an all-to-all schedule. The lowered schedule period decreases the latency and increases the bandwidth.

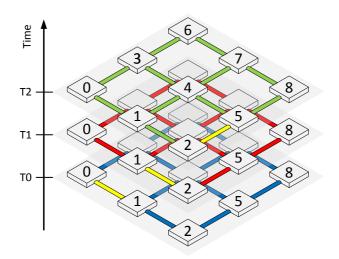

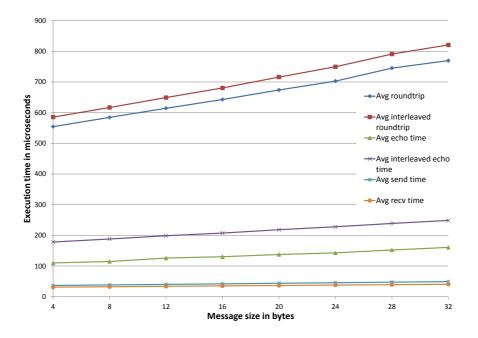

In our tool chain we used the Static NoC TDM scheduler<sup>1</sup> (SNTs)[19] to schedule the communication channels described in the XML input. The SNTs is a metaheuristic scheduler using adaptive large neighborhood search (ALNS)[20] and greedy randomized adaptive search procedures (GRASP)[21] to optimize the schedule period. The SNTs schedules the static routes in a time expanded graph of the NoC topology. A scheduled communication path in a time expanded graph of a 3 by 3 mesh is shown in Figure 5.1. The communication path marked with yellow is routed from processor 0 to processor 5. Each consecutive link of the routed communication path is routed in a consecutive time slot. The metaheuristic optimization algorithms break down part of the initial solution

<sup>&</sup>lt;sup>1</sup>The SNTs is open source and is publicly available at https://github.com/t-crest/SNTs.

Figure 5.1: Time expanded graph of a 3 by 3 mesh topology, with a communication path routed from processor 0 to processor 5.

and rebuild it trying to make the new solution shorter than the initial. The SNTs is designed to run for days, or as long as the application designer wants, continuously trying to optimize the solution.

To integrate the scheduler into the tool chain, we have made the following extension to the scheduler:

- Support of arbitrary bandwidths for any communication channel.

- Calculation of the WCL for all communication channels.

- XML formatted output of the calculated schedule and WCL.

The files we have added to the scheduler are the .cpp and .h files listed and described in Appendix D. Support for arbitrary bandwidth is given, by allowing multiple communication paths to be routed from source to destination of a communication channel. The arbitrary bandwidth is specified in the input XML file. The WCL time for a communication path of a given communication channel is calculated when the scheduler is done. When the schedule has been created, the scheduler goes through the schedule and counts the maximum space between any two consecutive communication paths belonging the the same communication channel. The scheduler writes the schedule and WCL together into an XML formated output file. The output from the scheduler is written to an XML file

with the open source pugixml[22] library. The representation of the schedule in the TDM scheduler is router centric. The schedule describes the configuration of each router in each time slot, this description aligns with distributed routing. A description that aligns with a source routing is a schedule describing the NI and the flit routes from the NI, called an NI centric schedule. To avoid multiple conversion back and forth between router centric and NI centric schedules the schedule in the XML file is router centric.

#### 5.5 Schedule converter

To keep the design modular, we have made a schedule converter that writes the platform specific details of the schedule. The source files of the schedule converter are the .java files in Appendix D. It converts the XML file into the format that is supported by the JOP processor and the T-CREST NoC platform. This conversion involves a conversion from a router centric schedule to a NI centric schedule. The conversion is performed by following the outgoing routes from each NI in each time slot. The static routing can be configured in the NoC in two ways: compile time configuration and run time configuration.

Compile time configuration is done by configuring the schedule in hardware tables at compile time. Compile time configuration is normally used in FPGA implementations. For compile time configuration we convert the schedule to VHDL tables for each node in the network, connecting it directly to the resource it is controlling. Conversion to VHDL tables is integrated into the SNTs scheduler. It prints out one VHDL entity containing a table for each router, the tables are indexed with the node ID.

Run time configuration is done by configuring the schedule by programming it from the processor at systems startup. For run time configuration we convert the schedule to a static array of integers such that each processor indexes the array with their processor ID and loads the contents of the array into the hardware configuration tables. The conversion of the XML file to a static Java array is done by a small Java program, which wraps the static array in a Table class that also defines methods for loading and verifying the schedule.

## 5.6 WCET-aware compiler

To get good real-time performance the compiler needs to optimize the WCET path in the control flow graph (CFG). Optimizing the WCET path, the compiler

knows the WCET path, thus the analysis and compilation could benefit from being performed by one tool. To find the WCET path, the compiler needs to make a pessimistic estimate of the run time of the given path. With more precise models the estimate can be less pessimistic. The estimate of the WCET path is found by assigning worst-case latencies to each instruction. The worst-case latencies might vary with the state of the system. Routing the interprocessor communication statically decouples this communication from the state of the system, reducing it to the WCL and the bandwidth between the two communication processes. For many core systems such a reduction in the state space is a great benefit and makes it possible to analyze the system. As an example, the latencies of a memory access to the communication scratch pad vary depending on the latency and bandwidth given by the scheduler. The latency does not have to be constant even for the same instruction, it can vary with the system's state. The latency of transferring a message ML in the system can be calculated as follows:

$$ML = WCL + \frac{MSG_{Size}}{Channel_{Bandwidth}}$$

(5.1)

Where WCL is the worst-case latency of waiting the a channel time slot,  $MSG_{Size}$  is the size of the message and the Channel<sub>Bandwidth</sub> is the bandwidth of the channel to the message destination. In the case where the WCET is higher than allowed the ML can be lowered by scheduling more communication paths for the given communication channel or spread out the communication paths in the schedule.

#### 5.7 Discussion

In this section we suggest two improvements to the scheduler that could decrease the latency of a communication channel in a schedule. If the bandwidth of a communication channel needs to be increased, more communication channels are routed. If the latency of a communication channel needs to be decreased, more communication paths can be added, but adding more communication paths does not guarantee this. If all the communication paths of a communication channel are routed closely together, the latency of the communication channel is worse than if the communication paths would be evenly distributed throughout the schedule. The first improvement is to make the scheduler aware of the proximity of other communication paths, when routing. A low latency channel could be specified by a low latency tag in the XML file. The second improvement will decrease the latency of a complete transaction through the network, the scheduler could be made to support reply messages. A reply message is a message sent from a to b followed by a reply from b to a. If we know the time separation of the first message arrival and the reply message departure, called the response delay, we can schedule two communication channels, such that only the departure of the first message needs to wait for its time slot. When the reply message is ready for departure it gets its time slot right away. This could be useful when slave components are accessed with known response delays, especially for a single word reads where the WCL is the largest contributer to the latency.

# Chapter 6

# Message passing interface

In this chapter we will create a message passing interface (MPI) for use with our tool chain. We will discuss the communication primitives in communicating sequential processes (CSP)[23] and Kahn process network (KPN)[24] and choose which communication type to implement. We will describe the software for transferring data from one processing core to another. This software takes care of the low level, hardware specific details of data transfers.

### 6.1 Related work

For message passing in large computer systems, the MPI [25] standard has been made. The MPI standard specifies an interface for sending and receiving messages in a large computer system without shared memory. The MPI standard defines a set of operations for communication through message passing and run time management of processes on massively parallel systems. An open source implementation of the MPI standard is the Open MPI [26]. The MPI standard is made for large computer systems made up of many computers connected together in a cluster. What we need for our tool chain at this point is a very simple MPI with only the most basic communication primitives.

#### 6.2 Communication primitives

To design a correct and efficient parallel application the parallelism should be considered from the early design phase. A specification of the application could be written in a formal language that supports message passing natively, such as CSP or KPN. Our hardware platform is designed to run one process on one processor. This design feature comes from the fact that running multiple processes on one processor will make the processes interfere, and the uncertainty of this interference will increase the WCET. When mapping an application onto the platform of this thesis, the application should be divided into different processes, to utilize multiple processing cores. The number of processors to map one application to, is determined by the timing requirements of the application and the resources available to the application.

Processes in both KPNs and CSP communicate by passing messages between each other. The CSP semantics implement synchronous message passing and the KPN semantics implement asynchronous message passing. Synchronous message passing is when the two processes synchronize when they exchange a message. The two processes are connected directly. This means that the sender and receiver returns from the execution of the send and receive function calls at the same time. In asynchronous message passing the two processes are connected by an infinite FIFO, meaning that the sender can send multiple messages without the receiver attempting to receive anything. Infinite FIFOs can of course not be implemented and in practice the FIFOs are bounded in size. Asynchronous message passing makes it possible to interleave calculation and communication. Both synchronous and asynchronous message passing can be implemented on top of each other. We chose the style of message passing with the lowest implementation overhead. The hardware implements asynchronous message passing with bounded FIFOs, so this is our choice. If needed, synchronous message passing can be implemented on top of our MPI, but this results in poor performance. The communication primitives we have chosen to implement are:

- Send() The Send() primitive sends the specified data to the specified recipient. If the bounded FIFO towards the recipient is full the Send() primitive blocks until there is room in the FIFO.

- Receive() The Receive() primitive receives data from a specified sender. If the bounded FIFO from the sender is empty the Receive() primitive blocks until there is data in the FIFO.

- RdySend() The RdySend() primitive is a way of avoiding blocking Send() calls. The RdySend() primitive checks if there is room in the bounded FIFO

towards the specified recipient. RdySend() returns true if there is room in the FIFO and false if the FIFO is full.

RdyReceive() The RdyReceive() primitive can be used to avoid blocking Receive() calls. The RdyReceive() primitive checks if there is data in the bounded FIFO from the specified sender. RdyReceive() returns true if there is data in the FIFO and false if it is empty.

#### 6.3 MPI in the T-CREST platform

As the programming language in our tool chain is Java, and the programming language in the T-CREST tool chain is C, we will only use basic Java for our MPI, which can easily be ported to C. Many of the observations we make will also be applicable in C. The source code for our MPI can be seen in Appendix E. The Tables.java file is the static array written by the schedule converter. In this embedded Java ported to JOP it is difficult to manage the location of variables and objects, this is a problem because the performance of message passing depends on placing the data for communication locally. In this JOP multiprocessor system, Garbage collect was not available, which limits the memory footprint and the run-time of the applications running on the system.

In the T-CREST platform, processors setup DMAs to transfer data from its local scratch pad to other processors' local scratch pad. The hardware platform we use in our tool chain is limited because it has to copy data in and out of the local scratch pad memory. Setting up a DMA requires a read pointer and a write pointer. The sending and receiving processors of a DMA transfer has to agree on the write pointer. One way of agreeing on the write pointer is to let the receiver send the next write pointer to the sender, each time it is ready to receive. Another way to agree is to layout the address space of which buffers are placed where. Allocating buffers statically is easy to analyze for the WCETaware compiler, and it avoids the extra latency of sending new write pointers back. The downside of allocating buffers statically, is that it might waste space in the already limited local scratch pad if not all buffers are used.

#### 6.3.1 Address space

The size of the local scratch pad of a single processor varies with the configuration of the system. Therefore the systems should be designed not to depend on a specific address space. Local scratch pad memory is very limited and accesses to main memory is very time consuming because many cores need to share the

Figure 6.1: The static DMA NI address space of the n<sup>th</sup> processor in a systems with N processors.

Figure 6.2: The address space in the local DMA NI of the buffers for one processor.

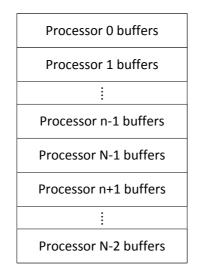

same off-chip memory. This means that address space of the local scratch pad should be compact. In this first version we support all-to-all communication by having buffers for all cores in the network in each tile. The static address space of the  $n^{\rm th}$  processor is shown in Figure 6.1

In a network with N nodes each NI has buffers for the N-1 other nodes. The nodes are zero indexed. We need to know the addresses statically, and we need to compact the address space. The buffers for the  $N - 1^{\text{th}}$  node is positioned in place of the local tile buffers. In this way all nodes can calculate their buffer address in all other cores. The address space of the buffers for one processor is shown in Figure 6.2.

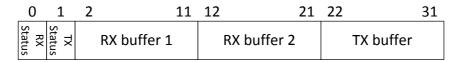

The hardware does not support any way of signaling that a DMA transfer is finished. To signal that a DMA transfer is done we wrap the data in a header and a footer phit. The header phit carries the length of the complete DMA transfer and the footer carries 0xFFFFFFF. The size of the maximum data

Listing 6.1: Pseudo code for the Send() primitive.

```

Send()

while not RdySend() do

do nothing

d od;

copy message to mem

swap receive buffer

setup DMA

```

Listing 6.2: Pseudo code for the Receive() primitive.

```

Receive()

while not RdySend() do

do nothing

od;

copy message from mem

swap receive buffer

```

message is 8 words (32 bytes).

#### 6.3.2 Communication primitives

In this section we describe how the communication primitives are implemented.

Send() The Send() primitive, setup a DMA transfer to transmit the data to the recipient. To send a packet we need to check that there is not a DMA transfer in progress. If no DMA is in progress the message is copied into the transmit buffer, and the buffer in the receiving end is swapped. To complete the send operation we need to set up the DMA transfer. The pseudo code for the Send() primitive is shown in Listing 6.1.

**Receive()** The **Receive()** primitive, waits until a DMA transfer has completed. When the transfer has completed, the message is copied out and the receive buffer is swapped. The pseudo code for the **Receive()** primitive is shown in Listing 6.2.

RdySend() The RdySend() primitive checks if the DMA is ready to setup. To check the status of the DMA, the DMA done bit is read from the NI. The pseudo

|   | Listing 0.0. I setud code for the haybena() primitiv |

|---|------------------------------------------------------|

|   | RdySend()                                            |

| 2 | read DMA done bit                                    |

|   | if done bit equals 1                                 |

| 4 | return true                                          |

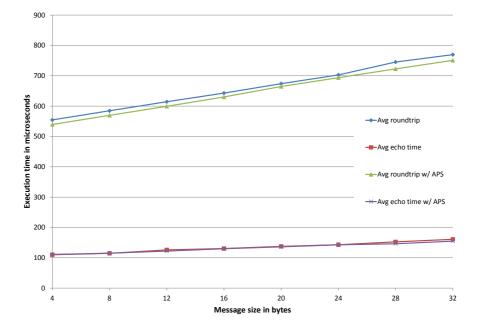

|   | fi;                                                  |