## Design of Power Efficient FPGA based Hardware Accelerators

Jonas Stenbæk Hegner s052574

Kongens Lyngby 2012 IMM-MSc-2012-133

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk IMM-MSc-2012-133

# Summary (English)

The aim of this thesis is to use an FPGA to speed up computations, and to analyse performance trade-offs with respect to latency, throughput and energy consumption.

To do this an option pricing algorithm was chosen as the test case.

The pricing algorithm was implemented in C and the latency tested on a desktop PC.

Then a soft core processor system was implemented, to run the application and to measure the number of cycles it took to do the calculations of option pricing. The third experiment involved a Application Specific Processor, designed to implement the option pricing algorithm in hardware.

The latency of these systems was measured, and the power consumption was measured for the soft core processor and the ASP.

Finally the three systems were compared with respect to their individual energy consumption. The results clearly show a speed up when comparing Application Specific processors with CPUs, both desktop CPU and soft core processors.

The energy consumption was also lower for the ASP and when using ASPs in parallel an even greater reduction is achieved.

<u>ii</u>\_\_\_\_\_

# Summary (Danish)

Formålet med det project er bruge en FPGA til at accelerere beregninger. Og derudover at analysere ulemper i forhold til latenstid og energiforbrug. Til dette formål er valgt en algoritme, som udregner optionspriser, som en test applikation. Algoritmen blev implementeret i C og latenstiden teste på PC. Herefter blev et soft core processor system implementeret, så applicationen kunne køres og antallet af clock cykler, der skal til for at køre simulationen, kunne måles. Endelig blev algoritmen implementeret i hardware på FPGA. Latenstiden samt effektforbruget blev målt for de to FPGA systemer. Til slut blev de tre systemer sammenlignet med hensyn til latenstid.

Og de to FPGA systemer blev sammenlignet med hensyn til energiforbruget. Resultaterne viser der opnå en besparelse i latenstid ved at bruge ASPen sammenlignet med de to processore. Også energiforbruget kan reduceres with brug af en ASP. Ved at benytte flere ASPer i parrallel kan energiforbruget reduceres yderligere. Samtidig med at latenstiden falder. iv

# Preface

This thesis was prepared at the department of Informatics and Mathematical Modelling at the Technical University of Denmark in fulfilment of the requirements for acquiring an M.Sc. in Informatics.

The thesis deals with power and latency in implementations in FPGAs and CPUs.

Advisor: Alberto Nannarelli, Informatics and Mathematical Modelling at the Technical University of Denmark.

Lyngby, 31-August-2012

Jonas Stenbæk Hegner s052574

vi

# Acknowledgements

I would like to thank my advisor Alberto Nannarelli, DTU for all the help and discussions of ideas, he provided during the Work on this thesis. His advice and friendly conversations has been invaluable.

I would also like to thank Edward A. Todirica, DTU for his guidance with respect to tools.

And thank to Joakim Sindholt, DTU for his contribution in form generation of some of the modules.

viii

## Contents

| Summary (English) |                |                           |     |  |  |  |  |  |

|-------------------|----------------|---------------------------|-----|--|--|--|--|--|

| Sι                | ımm            | ary (Danish)              | iii |  |  |  |  |  |

| Pı                | refac          | e                         | v   |  |  |  |  |  |

| A                 | ckno           | wledgements               | vii |  |  |  |  |  |

| 1                 | Intr           | oduction                  | 1   |  |  |  |  |  |

|                   | 1.1            | Project overview          | 2   |  |  |  |  |  |

| 2                 | Bac            | kground                   | 3   |  |  |  |  |  |

|                   | 2.1            | Accelerators              | 3   |  |  |  |  |  |

|                   | 2.2            | Power and energy          | 5   |  |  |  |  |  |

|                   | 2.3            | Power                     | 5   |  |  |  |  |  |

|                   | 2.4            | Energy                    | 7   |  |  |  |  |  |

|                   | 2.5            | FloPoCo                   | 7   |  |  |  |  |  |

|                   | 2.6            | Development board         | 8   |  |  |  |  |  |

|                   |                | 2.6.1 Power monitor       | 9   |  |  |  |  |  |

| 3                 | Application 11 |                           |     |  |  |  |  |  |

|                   | 3.1            | Option Pricing            | 11  |  |  |  |  |  |

|                   | 3.2            | Monte Carlo Simulation    | 12  |  |  |  |  |  |

| 4                 | Soft           | t core processor system   | 15  |  |  |  |  |  |

|                   | 4.1            | Design                    | 15  |  |  |  |  |  |

|                   | 4.2            | Implementation            | 16  |  |  |  |  |  |

|                   |                | 4.2.1 Soft Core Processor | 16  |  |  |  |  |  |

|                   | 4.3            | Test                      | 21  |  |  |  |  |  |

|     |       | 4.3.1 Gaussian random function                                                                              |

|-----|-------|-------------------------------------------------------------------------------------------------------------|

|     |       | 4.3.2 Cycle counter test                                                                                    |

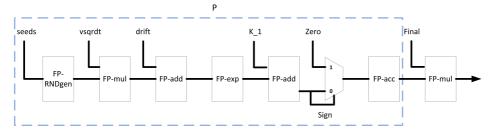

| 5   | ADI   | plication specific processor system 2'                                                                      |

|     | 5.1   | $\begin{array}{c} \text{Design} & \dots & $ |

|     | 5.2   | Implementation                                                                                              |

|     |       | 5.2.1 FPMul_binary32_100                                                                                    |

|     |       | 5.2.2 FPAdd_binary32_100                                                                                    |

|     |       | 5.2.3 FPExp binary32 100                                                                                    |

|     |       | 5.2.4 FPAdd3 binary32 100                                                                                   |

|     |       | 5.2.5 Random number generator                                                                               |

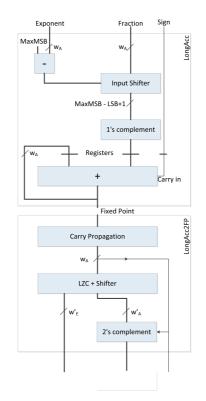

|     |       | 5.2.6 Floating Point Accumulator                                                                            |

|     |       | 5.2.7 Module Latency 3                                                                                      |

|     | 5.3   | Test                                                                                                        |

| 6   | Exp   | eriments 3                                                                                                  |

| Č   | 6.1   | Monte Carlo simulation on PC                                                                                |

|     | 0.1   | 6.1.1 Monte Carlo Simulation on PC results                                                                  |

|     | 6.2   | Monte Carlo simulation on Microblaze                                                                        |

|     |       | 6.2.1 Monte Carlo simulation on Microblaze results                                                          |

|     | 6.3   | Application Specific Processor                                                                              |

|     |       | 6.3.1 Application Specific Processor results                                                                |

|     | 6.4   | Energy consumption                                                                                          |

|     | 6.5   | Summary of Power and Energy                                                                                 |

| 7   | Cor   | clusion 4                                                                                                   |

| ÷., | 7.1   | Improvements and Further Experiments                                                                        |

|     |       |                                                                                                             |

| Bi  | bliog | graphy 50                                                                                                   |

| Α   | Hov   | v To 55                                                                                                     |

|     | A.1   | Testing with chipscope pro 55                                                                               |

|     |       | A.1.1 Example                                                                                               |

|     | A.2   | Working with XMD 55                                                                                         |

|     |       | A.2.1 Download Application Executable or Data File 6                                                        |

| в   | Sou   | rce Code 6                                                                                                  |

| _   | B.1   | Source Code for Monte Carlo Simulation                                                                      |

## CHAPTER 1

# Introduction

As financial computing and computational heavy applications become more and more common, the need for low latency solutions is increasing.

ASICs can be used to reduce the processor load and low power, but they lack flexibility, in a market that is changing rapidly. The time it takes to implement the ASIC chip means it can be obsolete, when it is ready to be deployed.

More and more companies are getting into hardware acceleration, both with graphical processing units and FPGAs. This thesis investigates implementation of a system used in financial computing, specifically to calculate profit of certain trades.

Three systems performing the same task are tested with respect to latency. And two of these are also tested with respect to the power and energy consumption and the impact of parallelization on the latency and power consumption.

During the work on this project two systems has been developed on FPGA, one system using a general purpose soft core processor, and another system as a processor designed to implement the specific calculations on the FPGA. Also a standard PC has been tested with the calculations with respect to latency. The application, a Monte Carlo simulation used in financial computing has been implemented in C and as a processor in hardware.

## 1.1 Project overview

The one system using a soft core processor runs the Monte Carlo simulation implemented in c, while executing the C program the power and execution time was measured. Then the power and energy consumption was calculated. The same was done for the hardware based Monte Carlo simulation. As for the PC testing, only the execution time was measured running the simulation.

This report describes the design, implementation and experiments of the before mentioned systems. As well as the testing. It also describes some tools needed to do the implementation and testing.

The thesis is organized as follows:

**Chapter 2** describes the power measurements in FPGAs as well as the board used to do the project. Lastly it describes a core generation tool called Flopoco, used to generate arithmetic units.

**Chapter 3** describes the Monte Carlo simulation application, and some basic background on this specific area of financial computing called option pricing.

**Chapter 4** outlines the design implementation and testing of a soft core processor system using the core provided by the vendor.

**Chapter 5** describes the application specific processor in both design, implementation and testing.

**Chapter 6** outlines the experiments done on the different systems and lastly the results of the experiments.

Project files are included on a CD, also included on the CD is application notes and manuals used for the various parts of the project. The documentation for the Xilinx ML550 board is also included.

## Chapter 2

# Background

## 2.1 Accelerators

CPUs are general purpose units which can be used for many different things, the problem with this is that not all calculations are very efficient. For example, it is common to offload computer graphics calculations to a Graphics Processing Unit, or GPU. This is one form of hardware accelerator. The purpose of this is to increase the overall performance of the system because the GPU is made specifically for the kind of operations that are used in computer graphics.

Figure 2.1: CPU to Hardware Accelerator

These hardware accelerators are faster than the general purpose units but also have a narrower field of use. They are also not flexible, when the chip is made, it is made for a very specific task, and to change it requires a whole new chip. Implementing hardware acceleration into an FPGA gives the designer the ability to change parts of the accelerator if needed. In many cases an Application Specific Processor or ASP implemented in an FPGA may lead to lower latency, but development time is not much shorter than for ASICs, but due to its ability to be reconfigured it is much more flexible and cost effective than ASICs.

There are two different approaches commonly used in financial computing, one is a hybrid approach, where the FPGA is connected to the host PC via network, the PC sends the data that are to be used in the calculations, other calculations are done on the PC. The other is pure FPGA computing, where the FPGA computes all values.

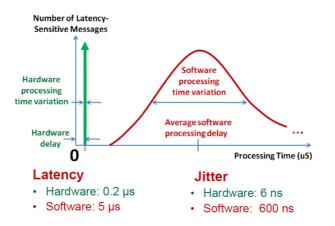

One of the biggest concerns in financial computing is the latency of the calculations and the variations in latency, also called jitter. When using a PC to do the calculations, other processes delaying calculations may cause jitter. In pure FPGA setups there is almost no jitter, and potentially lower latency [Loc12].

Figure 2.2: FPGA vs Software

As can be seen in figure 2.2 [Loc12] in software alot of things add to the jitter, like cache misses, other running processes interrupting. These factors can greatly increase the latency.

This is not the case in hardware processors with specific purposes, because they only have to do one thing.

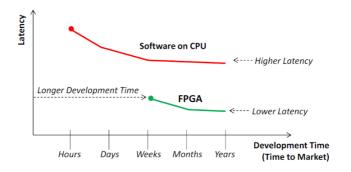

The biggest downside of doing the application specific processor is the development time. As illustrated in figure 2.3 [Loc12] the low latency FPGA solutions have considerably longer development time.

This is the advantage with software implementations, the development time can be as low as days compared to weeks with FPGAs.

Figure 2.3: Development time vs latency

## 2.2 Power and energy

This part describes the calculation of power and energy consumption in a system on FPGA boards.

### 2.3 Power

When considering power consumption in FPGAs, four parameters are important.

- Total power  $P_{tot}$  The total power consumed by the system.

- Bias power P<sub>bias</sub> The power used by to bias the FPGA(configuration, memory and interconnects).

- Static power  $P_{stat}$  The power consumed when the system is inactive.

- Dynamic power  $P_{dyn}$  The power consumed by the switching activity in the chip.

The dynamic power can be written is.

$$P_{dyn} = E_{pc(dyn)} \cdot f \tag{2.1}$$

Where  $E_{pc(dyn)}$  is the dynamic energy dissipated per cycle and f is the frequency. The FPGA configuration also contributes to the total power, this is what we call bias power  $P_{bias}$ , this is measured without downloading a bit stream to the FPGA(no configuration).

The equation for the biased total power is:

$$P_{tot(bias)} = P_{bias} + P_{stat} + E_{pc(dyn)} \cdot f \tag{2.2}$$

This means to get the total power of the system implemented on the FPGA alone, we need to unbias the total power. This will make the power figures independent of the FPGA type and size.

$$P_{tot} = P_{tot(bias)} - P_{bias} \tag{2.3}$$

As we can see from 2.2 the total power also depends on the frequency. Lets call the power measured when reset is pressed  $P_{reset}$  and the clock is stopped. So the equation for  $P_{reset}$  is:

$$P_{reset} = P_{bias} + P_{stat} \tag{2.4}$$

When measuring power on the FPGA, the total power and the power consumed when reset is pressed, is measured. If we isolate  $P_{stat}$  in the equation 2.4 we get:

$$P_{stat} = P_{reset} - P_{bias} \tag{2.5}$$

we can now write the equation for the dynamic power .

$$P_{dyn} = P_{tot} - P_{stat} \tag{2.6}$$

An example of the power calculation is shown below.

The measured values are

First we calculate the unbiased  $P_{tot}$  and the  $P_{stat}$

| Frequency | $P_{reset}$ | $P_{bias}$ | P <sub>tot(bias)</sub> |

|-----------|-------------|------------|------------------------|

| [MHz]     | [mW]        | [mW]       | [mW]                   |

| 100MHz    | 254.32      | 212.06     | 300.49                 |

Table 2.1: Example power values

$$P_{tot} = P_{tot(bias)} - P_{bias} = 300.49 - 212.06 = 88.43 \ mW \tag{2.7}$$

$$P_{stat} = P_{reset} - P_{bias} = 254.32 - 212.06 = 42.26 \ mW \tag{2.8}$$

We can now calculate the dynamic power

$$P_{dyn} = P_{tot} - P_{stat} = 88.43 - 42.26 = 46.17 \ mW \tag{2.9}$$

## 2.4 Energy

The power consumption is the power the system uses on average during operation. Another parameter is the energy used to perform the execution of a given operation.

$$E = P \cdot t_{op} \tag{2.10}$$

One system could use less power than another, but if the execution time is longer, the system is still using more energy. To determine the energy used we first need the energy per clock cycle  $E_{pc}$  and the number of cycles used in a given application. The total energy pr cycle can be written as:

$$E_{pc\_tot} = \frac{P_{tot}}{f} = P_{tot} \cdot T \tag{2.11}$$

This gives us the equation for the total energy used for a application.

$$E_{tot} = E_{pc \ tot} \cdot n_{cycles} \tag{2.12}$$

Where  $n_{cycles}$  is the total number of cycles used during execution. With cycle time  $T = \frac{1}{t}$ .

### 2.5 FloPoCo

In this project many different arithmetic units are used, to cut down on development time for standard components, an arithmetic core generation tool can be used. One tool that can be used to create these unit, is FloPoCo developed by Florent de Dinechin and his group at university of Lyon, France. This section will describe this tool and its use.

FloPoCo as a tool, is capable of producing synthesizable VHDL code especially suitable for FPGAs, using a command line interface. The tool includes options to specify target hardware and frequency. It can generate whole pipelined datapaths or single arithmetic operators.

Below is an example of the generation of a floating-point adder.

FloPoCo command for an adder is:

```

.\,/\,\,flopoco\ FPAdder\ wE\ wF

```

Where wE is the number of bit of the exponent and wF is the number of bits in the fraction. To get a 32 bit single precision floating-point adder, on a Virtex-5 at 100MHz the command would look like this:

```

./flopoco FPAdder 8 23 -frequency=100 -target=virtex5

```

This will produce the synthesizable VHDL code in a single file.

## 2.6 Development board

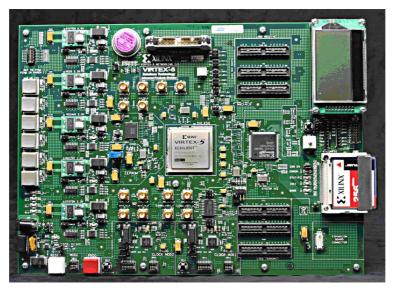

The FPGA development board used in this project is the Xilinx ML550 with a Virtex-5 FPGA chip.

Figure 2.4: Xilinx ML550 FPGA development board

This board was chosen for its physical power monitor connectors and the size of the FPGA chip. This enables measurements of power consumption through the use of a multimeter.

Some features of the board are listed below:

- Xilinx Device: XC5VLX50T-FFG1136 FPGA

- 7200 slices

- 6-input LUTs

- 48 DSP slices

- 2160 Kb block RAM

- on-board clock oscillators up to 250MHz

- Power monitor connector for powers measurements

- JTAG interface

#### 2.6.1 Power monitor

The Xilinx ML550 board features a power monitor connector for measuring the voltages of the different power supplies on the board. The power connector gives access to three voltages:

- $V_{aux}$  powers things like JTAG and DCM.

- $V_{int}$  is the core voltage, powers the chip.

- $V_{cco}$  is connected to I/O

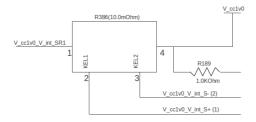

The voltage important in this project is  $V_{int}$  The schematic of the power monitor connector for the fpga chip is shown below in figure 2.5. To get the reset power  $P_{reset}$  the power is measured as above but with the reset pressed.

To measure the total biased power, first the bit stream is downloaded, so the system is running. With a multimeter measuring the voltage over pin 2 and 3 in figure 2.5, between these two is a 10.0mOhm kelvin resistor. This together with the reference voltage of  $V_{intmon}$ , gives us the power calculated by:

$$P_{tot(bias)} = V_{int(s+s-)} \cdot V_{intmon}/R \tag{2.13}$$

To measure the bias power  $P_{bias}$ , the same measurement as for the total biased power is used, but without downloading the bit stream. We can then measure the unconfigured FPGA.

Figure 2.5: Power monitor schematic

## Chapter 3

# Application

As the financial analysis becomes more and more complex, financial computing is getting more important. Financial computing often involves large models. Areas like option pricing can greatly benefit from hardware acceleration. In this chapter option pricing using Monte Carlo simulation is described. This is the application that has been used to do the power consumption experiments in fpga.

## 3.1 Option Pricing

Options are contracts between an owner of an financial asset and another party, giving the second party the right or option to trade that asset at an agreed upon price, on or before an expiration date, in Europe option can only be exercised on the expiration date. In this case we will only consider European options. The agreed upon price that is to be paid if the option is exercised is called the strike price. The price of the asset at the moment the option is bought is called the security price. The real price of the asset can fluctuate. So if at the expiration date the real price is higher than the strike price the owner of the option can make a profit, if not then he can choose not to exercise the option. The difference between the initial security price and the strike price is paid at

the point when the option is bought.

For example A has a stock priced at  $50 \in (\text{the security price at the moment})$ B can buy the option to trade that stock in 1 year, at the strike price of  $60 \in .$ Then if after a year the stock security price has increased to for example  $70 \in .$  B will exercise the option an make a profit of  $10 \in .$  If on the other hand the stock security price is decreased to  $30 \in .$  after a year, B will not exercise the option. B's loss in this case will only be the difference between the strike price and the initial security price  $10 \in .$  A makes a profit of  $10 \in .$  either way.

To try to predict the profit of an option, several methods have been used, the method described here is parametric Monte Carlo simulation.

### 3.2 Monte Carlo Simulation

The algorithm for the Monte Carlo simulation [EL04] of option pricing is done as shown in the pseudocode below:

Algorithm 1 Algorithm for Monte Carlo simulation  $S_0 =$  Security Price K = Strike Price $\mathbf{r} = \mathbf{Risk}$  free interest Rate  $\sigma =$  Security Volatility t = Time to expiration n = Number of iterations $\mathbf{r} = \mathbf{Risk}$  free interest rate sum = 0t = Time to expiration n = Number of iterationsvsqrdt =  $\sigma \sqrt{t}$ drift =  $\left(r - \frac{\sigma^2}{2}\right)t$  $\exp RT = e^{-r \cdot t}$ for  $i = 1 \rightarrow n$  do  $S_t = S_0 \cdot e^{dift + vsqrdt \cdot V_{random}}$ if  $(S_t - K) < 0$  then  $sum = sum + (S_t - K) \cdot expRT$ end if end for return sum/n

return sum  $\cdot final$

$\sigma$ , r and t are constant, this means drift, expRT and vsqrdt can be calculated in advance, before the execution of the algorithm.

Before the implementation of the algorithm a number of modification, to minimize the execution time has been made. As can be seen from the pseudo code above, the algorithm can be modified by moving some of the multiplications around, this means less cycles to get the final result. For example if K is divided by  $S_0$  so that  $K_1 = K / S_0$ , the multiplication  $S_0$  can then be removed from the for loop. similarly expRT can be removed from the loop. in the end we can have a modified algorithm shown in algorithm 2 These modifications also

| ũ ũ                                                        |  |  |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|--|--|

| Algorithm 2 Optimized Algorithm for Monte Carlo simulation |  |  |  |  |  |  |

| $S_0 = Security Price$                                     |  |  |  |  |  |  |

| $\mathbf{K} = \mathbf{Strike}$ Price                       |  |  |  |  |  |  |

| r = Risk free interest Rate                                |  |  |  |  |  |  |

| $\sigma = { m Security Volatility}$                        |  |  |  |  |  |  |

| t = Time to expiration                                     |  |  |  |  |  |  |

| n = Number of iterations                                   |  |  |  |  |  |  |

| $\mathrm{vsqrdt} = \sigma \sqrt{t}$                        |  |  |  |  |  |  |

| $	ext{drift} = \left(r - rac{\sigma^2}{2} ight)t$         |  |  |  |  |  |  |

| r = Risk free interest Rate                                |  |  |  |  |  |  |

| $\mathrm{sum}=0$                                           |  |  |  |  |  |  |

| t = Time to expiration                                     |  |  |  |  |  |  |

| n = Number of iterations                                   |  |  |  |  |  |  |

| $ m K_1 =  m Strike \ Price \ / \ S_0$                     |  |  |  |  |  |  |

| ${ m final} = { m S}_0 \cdot { m expRT} \; / \; { m n}$    |  |  |  |  |  |  |

| for $i = 1 \rightarrow n$ do                               |  |  |  |  |  |  |

| $S_t = e^{dift + vsqrdt \cdot V_{random}}$                 |  |  |  |  |  |  |

| if $(S_t - K_1) < 0$ then                                  |  |  |  |  |  |  |

| $sum = sum + (S_t - K_1)$                                  |  |  |  |  |  |  |

| end if                                                     |  |  |  |  |  |  |

| end for                                                    |  |  |  |  |  |  |

|                                                            |  |  |  |  |  |  |

makes the implementation of the algorithm simpler. The initial c implementation can be seen in appendix This algorithm uses standard gaussian distributed numbers. The standard gaussian distribution has a variance of 1 and a mean of zero.

## Chapter 4

## Soft core processor system

### 4.1 Design

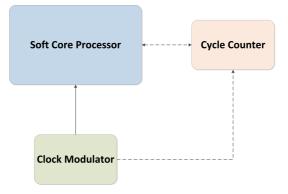

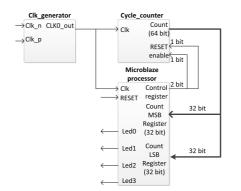

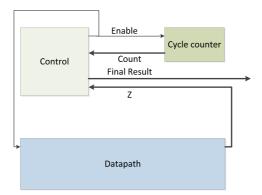

To get consistent cycle count we need to implement a CPU in the FPGA, this way we have no other processes to interfere with the execution, as would be the case with a desktop PC. To run programs written in C on a FPGA, a soft core processor is needed. To calculate the energy used by the system to run a given application, we need a cycle counter. The ML550 board used, also requires a clock modulator. The system is shown in figure 4.1.

The operations that are used in the applications for this project, are all single precision floating point.

The cycle count of the applications is unknown, assuming the execution time does not exceed 30min at 100MHz. We would need:

$$cycles = \frac{30 \cdot 60}{10^{-8}} = 180000000000 \tag{4.1}$$

$$N_{bits} = \frac{\log(18000000000)}{\log(2)} = 37.3bits \tag{4.2}$$

The cycle counter is attached with dotted wires in figure 4.1 because it is only present when cycle count experiments are done.

Figure 4.1: Soft core processor diagram

## 4.2 Implementation

#### 4.2.1 Soft Core Processor

Because the simulations in this project are all single precision, a single precision processor can be used for the C implementation. As a CPU for the C experiments on FPGA, the soft-core processor Microblaze from Xlinx was chosen. Listed below are a few features of the processor.

- 32 bit RISC architecture

- Optional hardware FPU

- Supports addition, subtraction, multiplication, division, comparison, conversion and square root

- Small area

- Expandable with custom peripherals

- Programming language C/C++

- Supports linux OS

- JTAG debug module

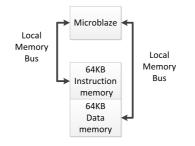

The processor is implemented with 64KB instruction and data memeory connected via the local memory bus, this is the fastest memory in Microblaze and there are no cache misses to create jitter.

Figure 4.2: Microblaze Architecture

#### 4.2.1.1 Cycle counter

Since the Microblaze uses 32bit registers, the minimum number of register we need to store 37 bits is 2, therefore makes sense to use a 64bit counter. Either way we would need 2 32bit register in the Microblaze. A simple implementation can used.

#### 4.2.1.2 Clock modulator

Because the ML550 board only has differential clock, a clock modulator is used to convert the differential to a single ended clock. The clock modulator used is an IP core from ISE design suite.

#### 4.2.1.3 Complete system

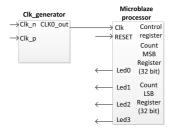

The complete system is shown in the figure 4.3

When the cycle count is measure a configuration as shown in figure 4.4 is used. In this configuration the Microblaze has 3 32 bit registers connected to the outside of the processor.

- Control register at 0xCH400000 this contains the reset and enable signal for the counter. writing 0x00000002 resets the counter. writing 0x00000001 starts the counter.

- Count MSB register at 0xCH400004 This contains the most significant bits of the counter.

Figure 4.3: Finished soft core processor system

Figure 4.4: Finished soft core processor system for cycle experiments

• Count LSB register at 0xCH400008 - This contains the least significant bits of the counter.

#### 4.2.1.4 Applications

The simulation that is run on the Microblaze is a C implementation of the algorithm in 3.2.

The body of the c code is quite straight forward, the challenging part is the gaussian floating point random number generator. Because C does not have a native function for gaussian distributed random numbers, two different methods were implemented.

#### 4.2.1.5 Random Number Generation

Two different method for random number generation were implemented and analysed. One method commonly used in C, and another method more suited for FPGA implementation. Both method approximate standard gaussian distributions.

#### 4.2.1.6 Random numbers using Box-Muller transformation

This method uses the normal random function in C rand(), the generated numbers are then transformed using the Box-Muller transforms.

$$Z_0 = \sqrt{-2\ln U} \cos\left(2\pi V\right)$$

$$Z_1 = \sqrt{-2\ln U} \sin\left(2\pi V\right)$$

(4.3)

Where U and V are uniformly distributed random numbers. This method is not suited for FPGA implementation because of the many different and slow operations, like square root, logarithm, sine and cosine. A comparison of the execution time for the two methods can be seen in the test section The source code is shown below:

```

#define PI 3.141592654

float gaussian_ra()

static float U, V;

static int phase =0;

float Z;

if (phase = 0){

//generate 2 random floats in range [0,1]

U = (rand()+1.)/(RAND_MAX+2.0);

V=rand()/(RAND MAX+1.);

//perform Box-Muller transforms

Z = s qrtf(-2.*logf(U)) * sinf(2.*PI*V);

}else

Z = \operatorname{sqrtf}(-2.*\log f(U)) * \operatorname{cosf}(2.*PI*V);

phase=1-phase;

return Z;

ł

```

Figure 4.5: C function for random number generator using Box-Muller

#### 4.2.1.7 Random numbers using LFSR

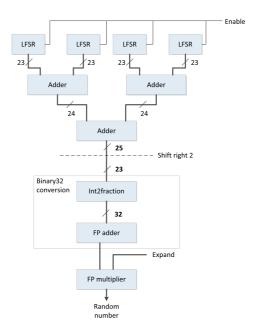

One way of generating uniformly distributed pseudo random numbers in FP-GAs, is to use linear feedback shift registers. These can be configured with a predefined word length, the period of the register is then  $P_{LFSR} = 2^n - 1$  [Alf96].

In this random number generator, the LFSR is used to generate the fraction of the floating point number, therefore an LFSR of 23 bits is needed, the period is therefore  $2^{23} - 1 = 8388607$ .

Because the LFSR is uniformly distributed, 4 generated numbers are averaged, the resulting distribution is gaussian. When generating floating point numbers centred around zero directly, the output number can be subnormal, the modules used later in the section 5 are not compatible with subnormal numbers, the generator needs to adjust for this. To do this numbers are generated initially in a positive range away from zero. To limit the range of the numbers, to a small range of positive floating point numbers, the exponent is set to a specific number in this case the exponent is set so that the range is [2.0:4.0].

The range is then offset by subtracting 3.0, which gives a range of [-1.0:1.0]. In the last stage the range is expanded to [-3.5:3.5], this is done to get a variance of approximately 1. In the test section some tests of the random number function is shown. The source code for the C implementation can be seen below:

```

uint32 t lfsr1 = 455u;

uint32 t lfsr2 = 68787u;

uint32 t lfsr3 = 8u;

uint32 t lfsr4 = 98u;

//gaussian ra generates floating numbers with gaussian distribution

float gaussian ra()

ł

uint32 t res, res2, ran temp;

float \overline{Z};

res = 0;

generate 4 random numbers from the linear feedback

//shift registers

lfsr1 = (lfsr1 >> 1) \hat{} (-(lfsr1 \& 1u) \& 0x00420000u);

\begin{array}{l} \mbox{list} & (11617 \ \& \ 10) & ((11617 \ \& \ 1u) \ \& \ 0x00420000 u); \\ \mbox{list} & 2 & = (116r2 \ >> 1) \ \land \ (-(116r2 \ \& \ 1u) \ \& \ 0x00420000 u); \\ \mbox{list} & 3 & = (116r3 \ >> 1) \ \land \ (-(116r3 \ \& \ 1u) \ \& \ 0x00420000 u); \\ \mbox{list} & 4 & = (116r4 \ >> 1) \ \land \ (-(116r4 \ \& \ 1u) \ \& \ 0x00420000 u); \\ \end{array}

// calulate the average to get gaussian distribution

res = lfsr1 + lfsr2 + lfsr3 + lfsr4;

//compile changes this to a shift operation

res2 = res/4;

//set exponent of random number, to get a range

//of [2:4]

ran temp=res2 & 0 \times 007 fffff | 0 \times 40000000;

// \overline{offset} range to [-1,1[ and then expand to [-3,5:3,5]

Z = (*(float*)\&ran temp - 3.0)*3.5;

return Z;

}

```

Figure 4.6: C code for random number generator using LFSR

### 4.3 Test

#### 4.3.1 Gaussian random function

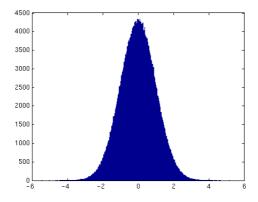

To test the mean and variance of the random number function, 1000000 random numbers are generated and the variance and mean is calculated in Matlab. Further more a histogram is produce to confirm the bell shape of the distribution. The variance should be close to 1 and the mean should be close to zero.

#### 4.3.1.1 Random numbers using Box-Muller

The histogram is shown in figure 4.8:

Figure 4.7: Histogram for Box-Muller random number generator

As can be seen the histogram is reasonably bell shaped. The mean and variance is shown in the table below: With mean close to zero and variance close to 1,

| Mean     | 0,0010 |

|----------|--------|

| Variance | 0,9987 |

Table 4.1: Mean and variance of Box-Muller random number generator

the numbers generated are close to standard gaussian distribution.

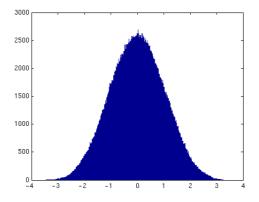

#### 4.3.1.2 Random numbers using LFSR

The histogram is shown in figure 4.8:

As can be seen the histogram is reasonably bell shaped. The mean and variance are shown in the table below: With these numbers the numbers generated are

| Mean     | 0,000011916 |  |  |

|----------|-------------|--|--|

| Variance | 1,097       |  |  |

Table 4.2: Mean and variance of LFSR random number generator

Figure 4.8: Histogram for LFSR random number generator

even closer to a standard gaussian distribution compared to the Box-Muller method. To obtain more precision more LFSRs are needed so that the average could be over more values, for example an average of 16 vaules. But because of the size restriction of the FPGA chip, this is not feasible. The other way is to generate more values from the four, but this would lower the throughput. Since system in this project is more a proof of concept, than an actual product, the random generator is using 4 LFSRs.

#### 4.3.1.3 Random generator time test

A test of the execution time was done on a desktop pc, at two different frequencies and with as little other processes running as possible, to give more consistent results. Specifications of the pc was:

- Processor: Intel Core2duo e6600

- Memory: 4Gb RAM

- OS: Xubuntu 12.04

- kernel 3.2.0-31-generic-pae

- gcc 4.6.3

Each method is run 10000000 and 100000 times, and at two different cpu frequencies, while the time is recorded. This is done 10 times and the average is taken.

|           | LFSR       |                     | BOX-Muller |                     |       |  |

|-----------|------------|---------------------|------------|---------------------|-------|--|

| Frequency | $T_{exec}$ | n <sub>cycles</sub> | $T_{exec}$ | n <sub>cycles</sub> | Ratio |  |

| [MHz]     | [ms]       | -                   | [ms]       | -                   |       |  |

| n=100000  |            |                     |            |                     |       |  |

| 1600      | 2.5        | 4000000             | 23         | 36800000            | 8.97  |  |

| 2400      | 1.6        | 3840000             | 15.4       | 36960000            | 9.16  |  |

| Average   |            | 3920000             |            | 36880000            | 9.07  |  |

| n=1000000 |            |                     |            |                     |       |  |

| 1600      | 25         | 40000000            | 229.1      | 366560000           | 9.2   |  |

| 2400      | 17         | 40800000            | 152.5      | 366000000           | 9.63  |  |

| Average   |            | 40400000            |            | 366280000           | 9.41  |  |

Table 4.3: Execution time test for the random number generators

As can be seen from table 6.1, the LFSR method is almost a factor 10 more efficient, the impact of the two methods on the Monte Carlo simulation can be seen in sections 6.2 and 6.1.1.

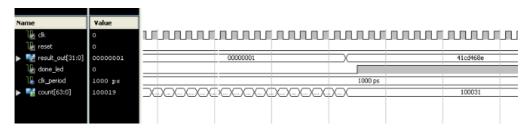

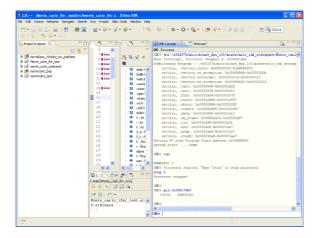

### 4.3.2 Cycle counter test

Test of the system has been done in Xilinx SDK, the software development kit for Microblaze. The test is done with a simple program that increments numbers in a for loop, this test can then be executed for a number of iterations of the for loop. The cycle count can then be read with the command mrd,followed by the register number of the counter, in the Xilinx Microprocessor Debugger XMD. Below is a table of the obtained cycle counts. As can be seen in table 4.5 as the

| Number of  | Plain for | For loop   | For loop   | For loop   |

|------------|-----------|------------|------------|------------|

| iterations | loop      | with $j++$ | with $j++$ | with $j++$ |

|            |           |            | b++        | b++ g++    |

| 10         | 140       | 190        | 240        | 290        |

| 100        | 1220      | 1720       | 2220       | 2720       |

| 1000       | 12020     | 17020      | 22020      | 27020      |

| 10000      | 120020    | 170020     | 220020     | 270020     |

| 100000     | 1200020   | 1700020    | 2200020    | 2700020    |

Table 4.4:

Cycle Counts from Microblaze cycle tests

number of iterations is increased the number of cycles is increased linearly. The same is the case when the number of calculations per cycle is increased. The numbers are consistent.

The other test performed is a test of the Monte Carlo simulation with 100000 iterations on the Microblaze. First for the Monte Carlo simulation using Box-Muller method as shown in figure 4.9 The other random generator for Monte

| 🐹 XMD Console 🛛 🗖 Welcome                             | 🖹 🗸 🗖 E |

|-------------------------------------------------------|---------|

| MD Process                                            |         |

| section, .data: 0x00005c60-0x000061bb                 |         |

| section, .eh_frame: 0x000061bc-0x000061bf             |         |

| section, .jcr: 0x000061c0-0x000061c3                  |         |

| section, .bss: 0x000061c8-0x00006257                  |         |

| section, .heap: 0x00006258-0x00006a57                 |         |

| section, .stack: 0x00006a58-0x00007257                |         |

| Setting PC with Program Start Address 0x00000000      |         |

| System Reset DONE                                     |         |

| XND% run                                              |         |

| RUNNING> 0                                            |         |

| XMD% Processor started. Type "stop" to stop processor |         |

| stop 0                                                |         |

| Processor stopped                                     |         |

| XMD %                                                 |         |

| XMD% mrd 0x00017d00                                   |         |

| 17D00: 41C6A7A2                                       |         |

| XND %                                                 | ~       |

| < III                                                 | >       |

### Figure 4.9: ChipScope test of Monte Carlo simulation using Box-Muller on Microblaze

Carlo simulation using LFSR method, the result is shown in figure 4.10 The

| XMD Console X 🔲 Welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| MD Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Section, .ccors: 0x00002000-0x0000200/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| section, .dtors: 0x00002888-0x0000288f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| section, .rodata: 0x00002890-0x000028f7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| section, .data: 0x000028f8-0x00002a53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| section, .eh_frame: 0x00002a54-0x00002a57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| section, .jcr: 0x00002a58-0x00002a5b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| section, .bss: 0x00002a60-0x00002aa7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| section, .heap: 0x00002aa8-0x000032a7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| section, .stack: 0x000032a8-0x00003aa7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| Setting PC with Program Start Address 0x00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| System Reset DONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| The second s |   |

| KMD% run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| RUNNING> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| MD% Processor started. Type "stop" to stop processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| stop 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| Processor stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| OND %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| (MD% mrd 0x00017d00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

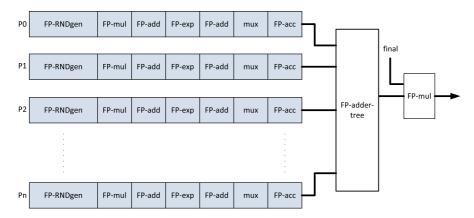

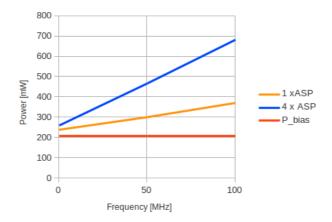

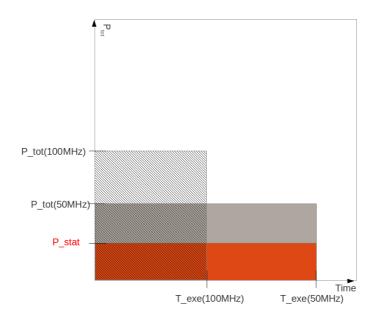

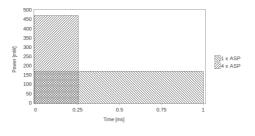

| 17D00: 41C6FCF9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |