### Reconfigurable Architectures: from Physical Implementation to Dynamic Behaviour Modelling

Kehuai Wu

Kongens Lyngby 2007 IMM-PHD-2007-180

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

# Summary

This dissertation focuses on the dynamic behavior of the reconfigurable architectures. We start with a survey of the existing work with the aim of categorizing the current research and identifying the future trends. The survey discusses the design issues of the reconfigurable architectures, the run-time management strategies and the design methodologies.

The second part of our work focuses on the study of commercial FPGAs that support the dynamic partial reconfiguration. This work grants us a better understanding of the limit and the potential of the main-stream commercial FPGA, and justifies the necessity of employing more advanced technologies in order to enable the realization of highly efficient reconfigurable architectures.

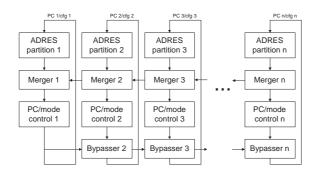

The third part of our study is carried out on ADRES, a coarse-grained datapathcoupled reconfigurable architecture. The study on ADRES shows that Multithreading not only is feasible for reconfigurable architectures, but greatly improves the architecture scalability as well.

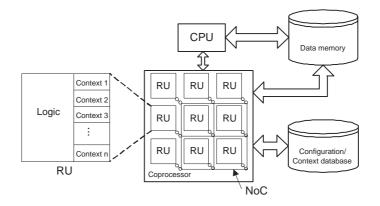

Our concluding study proposes a simulation framework for coprocessor-coupled reconfigurable architectures, namely COSMOS. The COSMOS simulation framework comprises a generic application model and an architecture model, the combination of which captures the dynamic behavior of the reconfigurable architectures. Our framework is a tool for studying the run-time management strategies and for experimenting the design space exploration of the reconfigurable architectures, and offers a means of evaluating various other works on a common ground. <u>ii \_\_\_\_\_\_</u>

# Resumé

Denne afhandling omhandler de dynamiske egenskaber ved rekongifurerbare arkitekturer. Først er der foretaget en undersøgelse af eksisterende forskning for at kategorisere denne og identificere tendenser for fremtiden. Undersøgelsen diskuterer designforhold for rekongifurerbare arkitekturer, run-time håndteringsstrategier og designmetoder.

Anden del af afhandlingen fokuserer på studier af kommercielle FPGAer, der understøtter dynamisk partiel rekongifurering. Dette danner baggrund for dybere forståelse af begrænsninger og muligheder ved generelle kommercielle FP-GAer og understreger samtidig nødvendigheden for at anvende mere avancerede teknologier for at gøre realisering af effektive rekongifurerbare arkitekturer mulig.

Den tredje del omhandler arbejdet med ADRES, en grovmasket datavejskoblet rekongifurerbar arkitektur. Studierne af ADRES viser at fler-trådet ikke blot er muligt for rekongifurerbare arkitekturer, men også forbedrer arkitekturens skalerbarhed markant.

De konkluderende studier fremviser COSMOS, et simuleringsmiljø for coprocessorkoblede rekongifurerbare arkitekturer. COSMOS simuleringsmiljøet omfatter en generel applikationsmodel og en arkitekturmodel, som tilsammen modellerer de dynamiske egenskaber ved rekongifurerbare arkitekturer. Miljøet er et værktøj til studier af run-time håndteringsstrategier og eksperimentering med udforskning af de mulige designløsninger af rekongifurerbare arkitekturer, og muliggør sammenligning af forskellige løsninger under de samme forudsætninger. iv

# Preface

This thesis was prepared at the institute of Informatics and Mathematical Modelling, at the Technical University of Denmark, in partial fulfillment of the requirements for acquiring the Ph.D. degree. The Ph.D. study was supervised by Professor Jan Madsen.

The study of the reconfigurable architecture has been a puzzling journey. One can immerse himself in the world of infinite possibilities and keep wondering what message is crucial to deliver to the others. My belief is that, at this moment, we should focus more on the run-time management study. With the goal of easing other's work, the COSMOS framework is presented. As fundamental as it is generic, the COSMOS model captures the essence of dynamic reconfigurable architectures.

The thesis consists of a summary report and a collection of chapters based on 3 research papers written during the period 2005–2007, and elsewhere published.

Lyngby, May 2007

Kehuai Wu

# Papers contributed to the thesis

- Kehuai Wu and Jan Madsen. Run-time Dynamic Reconfiguration: A Reality Check Based on FPGA Architectures from Xilinx Norchip Conference 2005. Published

- 2 Kehuai Wu, Andreas Kanstein, Jan Madsen and Mladen Berekovic MT-ADRES: Multithreading on Coarse-Grained Reconfigurable Architecture International Workshop on Applied Reconfigurable Computing 2007. Published

- 3 Kehuai Wu and Jan Madsen. COSMOS: A System-Level Modelling and Simulation Framework for Coprocessor-Coupled Reconfigurable Systems SAMOS VII: International Symposium on Systems, Architectures, Modelling and Simulation 2007. Published.

- 4 Kehuai Wu, Esben Rosenlund, and Jan Madsen. Towards Understanding the Emerging Critical Issues from the Dynamic Behavior of Run-Time Reconfigurable Architectures International Conference on Codesign and System Synthesis 2007. Submitted.

- 5 Kehuai Wu, Andreas Kanstein, Jan Madsen and Mladen Berekovic MT-ADRES: Multithreading on Coarse-Grained Reconfigurable Architecture-extended version International Journal of Electronics 2007. Accepted

# Acknowledgements

Professor Jan Madsen has been a continuous inspiration throughout my Ph.D. study. He sets a great model for me with his generosity, commitment and enthusiasm.

Knowing Andreas Kanstein from Freescale is an important event in my life. I appreciate him being there for me during the hard time.

Mladen Berekovic and Frank Bouwens made my stay in Belgium a wonderful experience. There had never been a dull moment at IMEC, Leuven, thanks to them.

Flemming Stassen has done me so many kindnesses. Living in a foreign country has been made so much easier with his help.

I own my gratitude to so many people, especially the ones working in the SoC group as I have been. ARTIST2 gave me the financial support during my more productive time, and made some of my publication possible.

Knowing that my parents love me gives me strength. They helped me countless times, and gave me more than anyone can believe.

My wife, Xia, is my home, my shepherd and my hope. Without her, nothing will be the same.

Kehuai Wu May 2007 x\_\_\_\_\_

\_

### Contents

| Summary                              |      |                                            |     |  |  |  |

|--------------------------------------|------|--------------------------------------------|-----|--|--|--|

| R                                    | esum | ié                                         | iii |  |  |  |

| Preface                              |      |                                            |     |  |  |  |

| Papers contributed to the thesis vii |      |                                            |     |  |  |  |

| Acknowledgements i                   |      |                                            |     |  |  |  |

| 1                                    | Intr | roduction                                  | 1   |  |  |  |

|                                      | 1.1  | Reconfigurable architectures in a nutshell | 1   |  |  |  |

|                                      | 1.2  | The origin, and the revival                | 2   |  |  |  |

|                                      | 1.3  | Industry practice                          | 4   |  |  |  |

|                                      | 1.4  | State-of-the-art academic research         | 5   |  |  |  |

|                                      | 1.5  | Thesis Outline                             | 7   |  |  |  |

| 2 Survey of the Dynamically Reconfigurable Systems |                                                                                                               |                                             | 9  |  |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|--|

|                                                    | 2.1                                                                                                           | Architecture                                | 10 |  |

|                                                    | 2.2                                                                                                           | Reconfiguration strategy                    | 23 |  |

|                                                    | 2.3                                                                                                           | Operating system design                     | 27 |  |

|                                                    | 2.4                                                                                                           | Design methodology                          | 31 |  |

|                                                    | 2.5                                                                                                           | Conclusion                                  | 42 |  |

| 3                                                  | 3 A Reality Check Based on FPGA Architectures from Xilin                                                      |                                             |    |  |

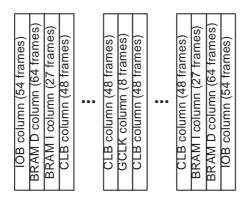

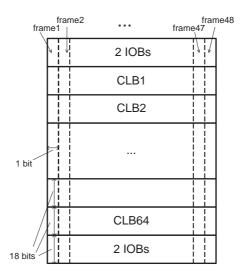

|                                                    | 3.1                                                                                                           | The Virtex configuration organization       | 46 |  |

|                                                    | 3.2                                                                                                           | Xilinx dynamic reconfiguration design flows | 47 |  |

|                                                    | 3.3                                                                                                           | ICAP                                        | 51 |  |

|                                                    | 3.4                                                                                                           | Conclusions                                 | 51 |  |

| 4                                                  | MT-ADRES: Multithreading on Coarse-Grained Reconfigurable<br>Architecture 5                                   |                                             |    |  |

|                                                    | 4.1                                                                                                           | Introduction                                | 54 |  |

|                                                    | 4.2                                                                                                           | ADRES Multithreading                        | 58 |  |

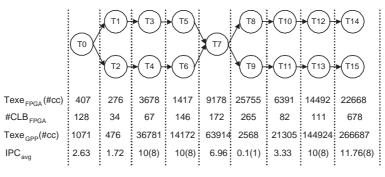

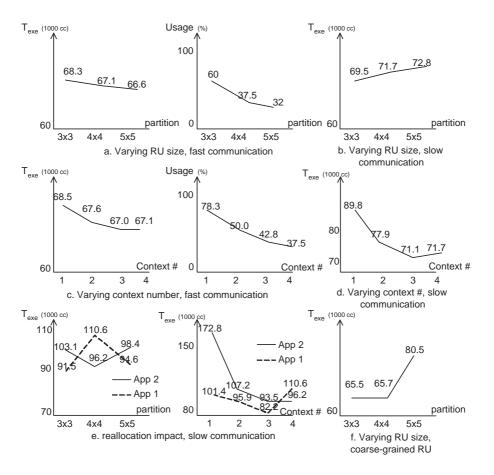

|                                                    | 4.3                                                                                                           | Experiment                                  | 62 |  |

|                                                    | 4.4                                                                                                           | Discussion                                  | 68 |  |

|                                                    | 4.5                                                                                                           | Conclusions and future work                 | 70 |  |

| 5                                                  | COSMOS: A System-Level Modelling and Simulation Frame-<br>work for Coprocessor-Coupled Reconfigurable Systems |                                             |    |  |

|                                                    | 5.1                                                                                                           | Background                                  | 73 |  |

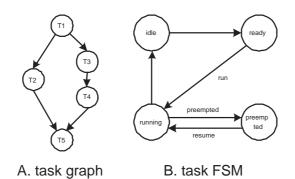

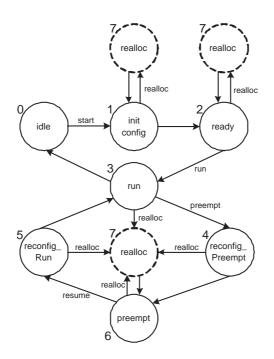

|                                                    | 5.2                                                                                                           | Task model                                  | 75 |  |

### CONTENTS

|   | 5.3              | Coprocessor coupled architecture model |  |  |  |

|---|------------------|----------------------------------------|--|--|--|

|   | 5.4              | System-C simulation model              |  |  |  |

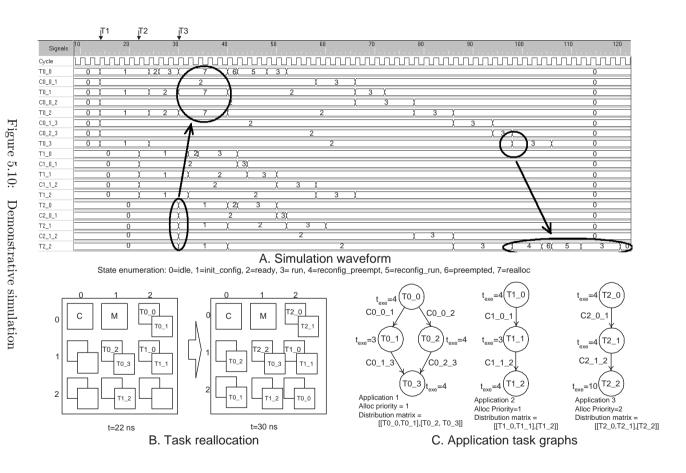

|   | 5.5              | Demonstrative simulation               |  |  |  |

|   | 5.6              | MP3 Experiments 90                     |  |  |  |

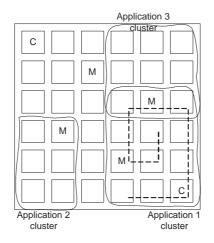

|   | 5.7              | Advanced allocation strategies         |  |  |  |

|   | 5.8              | Future work                            |  |  |  |

|   | 5.9              | Conclusion                             |  |  |  |

|   |                  |                                        |  |  |  |

| 6 | Con              | iclusion 105                           |  |  |  |

|   | 6.1              | Contribution                           |  |  |  |

|   | 6.2              | Outlook                                |  |  |  |

|   |                  |                                        |  |  |  |

| Α | A TGFF files 109 |                                        |  |  |  |

|   | A.1              | Input file                             |  |  |  |

|   | A.2              | Output file                            |  |  |  |

### Chapter 1

### Introduction

### 1.1 Reconfigurable architectures in a nutshell

Traditional computer architectures mainly takes two approaches to execute an application. The first one is to employ a programmable microprocessor. The processor-based architectures usually support an instruction-set that covers a wide range of logic and memory operations, thus can execute various applications when the application is proper compiled. However, due to the usually limited amount of parallel computing resource, the large execution overhead and the memory bottleneck, these architectures are inefficient in terms of performance and energy.

The second approach is to tailor a hardware for a specific application, so that the application can be executed at the highest affordable speed. The resulting Application-Specific Integrated Circuit (ASIC) is usually dedicated to one application, or even only one configuration of a certain application, thus exceedingly lacks the flexibility. ASIC design also has a long development cycle, thus the consequence of having fabrication fault or design errors is more severe than the software-based application design. The lack of flexibility substantially increase the verification and test phase of the implementation.

In hopes of closing the gap between the processor-based architectures and the

ASIC, reconfigurable architectures come into play. The mainstream of the reconfigurable architectures is composed of a fixed logic part and a reconfigurable part. The fixed logic usually includes a programmable processor that executes the non-crucial parts of the application and controls the reconfigurable unit. The reconfigurable unit is a high-performance field-programmable logic frequently used to accelerate the execution of the application kernels.

From the architecture composition, we see that both the fixed part and the reconfigurable part are programmable, thus the programmability of the processorbased architecture is retained. The reconfigurable unit can even extend the instruction set of its fixed counterpart, therefore makes the programmability of the architecture even stronger. The reconfigurable unit usually is a scalable gate array with high amount of parallel computation resource. This gives the reconfigurable unit a potential performance advantage over the processors. Due to the nature of the field-programmable logic, the reconfigurable unit is usually not as efficient as the ASIC implementation in terms of power and speed, but the flexibility compensates for it.

### 1.2 The origin, and the revival

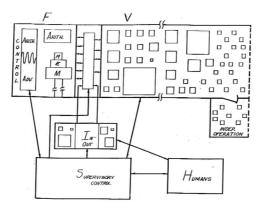

In year 1960, Gerald Estrin at the University of California at Los Angeles proposed a computer architecture that is very different from the main stream research [33] at that time. As shown in his original figure (figure 1.1), this computing machine is a combination of a Fixed (F) computing unit and a Variable (V) unit. The fixed part of the machine offers the user a consistent and friendly interface, while the variable unit of the system performs specific task as user requests. The variable part of the system offers a performance that is as high as dedicated hardware, and it can reconfigure itself to fit the user's application. This is the first time that the reconfigurable computing concept has been openly discussed. However, due to the lack of the technology support, this concept was not adopted well during 60's, and the microprocessor-ASIC combo have dominated both the industry and the academic research in the next few decades.

However, the advance of the silicon technology leads to many new digital system design strategies and trends. The appearance of the Complex Programmable Logic Device (CPLD) and the Field-Programmable Gate Array (FPGA), which are mostly used for implementing simple digital circuit and prototyping larger digital systems, respectively, gives very solid technical backbones to the reconfigurable computing. Through these devices, we have acquired a preliminary understanding of the configurability, the performance, the programmability and the application domain of the reconfigurable architectures.

Figure 1.1: One of the earliest proposal of reconfigurable computing architecture [33]

In recent years, the chip fabrication cost and the non-recurrent engineering cost has increased to a level where the non-reusable custom ASIC design is hardly affordable for smaller business. Since the chip reusability becomes an important issue, FPGA is not only used as a prototyping device, but also a solution as part of the final product. Even though there is always a performance margin between the ASIC and the FPGA, thanks to the demand of the digital design community, this margin has been shrinking in the last few years, and even battery-powered FPGA-based designs are emerging. This trend suggests that the FPGA is the most appealing base for reconfigurable architecture study, and people shouldn't expect anything less from the reconfigurable architectures than from the FPGA in terms of performance.

Some other recent technologies contributed to the study of the reconfigurable architectures. The development of the intellectual property (IP) core is a promising strategy for increasing the design reusability. One of the byproducts of the IP core reusability study is the hardware run-time adaptivity, which is one of the enabling technologies of the dynamically reconfigurable architecture. Also, the high-level synthesis, especially the finite-state-machine based and loop-level optimization based synthesis, fits naturally to the programmability study of the reconfigurable architectures.

The technology scaling is driving the computer architecture research into the era of Multi-Processor System-on-Chip (MPSoC). Multiple cores interconnected with an on-chip network (NoC) is one of the most interesting on-going architecture research due to its potential for increasing design scalability and performance. When the MPSoC paradigm is applied on the reconfigurable architectures, the reconfigurable architecture is benefited from higher flexibility, better

scalability and the better usage of coarse-grained parallelism.

Future embedded systems will be based on platforms which allow the system to be extended and incrementally updated while running in the field. This will not only extend the life time of the system, but also allow the system to adapt to the physical environment as well as performing self-repair, hence increasing the reliability and robustness of the system. Dynamically reconfigurable architectures is the most suitable technology for facilitating this, and is being studied in the research of self-evolving embedded system that can adapt to the environment and fault tolerable system that needs long lifecycle in the field.

To conclude, the reconfigurable architecture research at the current stage is of utmost importance and relevance. The study in this area has solid technology foundation from the previous work, and the issues to be addressed are tightly intertwined with many other crucial research areas. Investigating and understanding the reconfigurable architecture not only push the reconfigurable architecture study forward, but encourage the related fields of research as well.

### **1.3** Industry practice

Being the flagship of commercial FPGA developers, Xilinx [9] contributed significantly to the physical implementation of the reconfigurable device. Their VIRTEX FPGAs can partially reprogram themselves during run-time, hence are realistic platforms for studying the online adaptive systems. Their existing configuration development tool chain has been augmented for supporting the generation of partial configuration, and the on-chip configuration device is given a higher bandwidth to achieve faster reconfiguration. At the current stage, the killer application for such a system is yet to be found, and their partial reconfiguration approach is mostly used for academic experimentations.

There exists some off-the-shelf reconfigurable architectures. The XD1 [5] supercomputers from Cray, the MAP [8] processor from SRC and various systems from Nallatech [6] etc. tries to get the most out of the commercial FPGA by coupling them to other control modules. These systems are more focused on offering parallel computation power than frequent reconfiguration, and mainly attempt to offer user-friendly interface to the programmers. Many of them also focus on employing an array of FPGAs in order to improve the system performance even further.

Other in-the-lab commercial examples are known. The Chameleon System

Inc[96]<sup>1</sup> proposed a single-chip solution, cs2000 architecture, to push the use of much more advanced reconfiguration strategies on commercial FPGAs. Their architecture development is discontinued from its infancy, but it still inspired many academic researches. The Silicon Hive [7] approached the reconfigurable system development from the IP development and programmability study. Celox-ica [4] proposed to use a c-like programming language, Handle-C, to address the programmability issue of the reconfigurable architectures. There are many other new technologies used in some context, but a highly integrated tool flow or a dedicated architecture is yet to be seen.

In general, the commercial reconfigurable architecture is centered on the offthe-shelf FPGAs. The technologies being studied and put to practice is mostly computation-oriented rather than reconfiguration-oriented. The study on programmability and architecture is still premature, and the run-time management is not being recognized as a critical issue. The lack of highly automated tool support and the lack of better understanding of the application domain is hindering the acknowledgement of the reconfigurable architecture, and in turn, results in the miscarriage of many great technologies' commercial breakthrough.

### 1.4 State-of-the-art academic research

On the contrary, academic researches on reconfigurable architecture has witnessed an outburst of new ideas. The architecture study leads to the demand of the better understanding of the logic granularity issue, the architecture coupling issue and the configuration strategy issue etc. The programmability study leads to the demand of highly automated and efficient high-level synthesis, mapping, partition tools etc. The behavior study of the reconfigurable system leads to the need of highly complicated run-time management system design, which is closely related to the architecture design and application mapping strategy.

In the last couple of decades, logic units of various granularities have been proposed and evaluated. The logic granularity is the measure of how precise the configuration data can describe the function of the logic unit. The impact of the granularity variance has been studied to a great extend in terms of memory requirements, performance and programmability etc.

The coupling between the reconfigurable unit and the fixed part is also a complicated issue. Commercial solutions are usually multi-chip systems, where the fixed part and the reconfigurable part are not on the same chip, thus the coupling between these two parts is always very loose. Tighter coupling enables

<sup>&</sup>lt;sup>1</sup>Not in business since 2001

much faster communication between the fixed logic and the reconfigurable unit, therefore results in much more interesting system behaviors and increases the occurrence of reconfiguration. The coupling has great impact on the architecture scalability, the data communication efficiency and the reconfigurability.

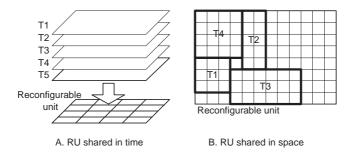

The online configuration strategy has also lead to many discussions. Whether a reconfigurable unit should be shared by multiple tasks in time or in space, and how to share the reconfigurable unit between tasks are open for further experimentation. These topics further lead to the study of the multi-context FPGA, inter-task communication and configuration memory hierarchy.

Programmability of reconfigurable architectures is another interesting topic. The reconfigurable architectures need the application to be partitioned into two parts, one being executed on the reconfigurable units, and the other being executed on the fixed part. The part of the application being executed on the reconfigurable unit needs to optimally use the reconfigurable unit, which offers parallel computing resources. To program for the reconfigurable architectures, we either need a high-level synthesis tool that integrates the partitioning tool, synthesis tool and compilation tool in one environment, or we need a development kit to carry out the software programming, hardware modelling and the interfacing at the same time. No matter which approach we take, the performance of the architecture is determined by how well we can explore the parallelism in the application from data level to task level, which is not a trivial task.

The dynamic reconfiguration is a costly operation. How frequently should a reconfigurable unit be reconfigured, and how should it be reconfigured needs to be decided at run-time, thus the run-time management system is another challenging design issue. For a large-scaled reconfigurable system that supports multi-tasking, the reconfigurable part of the system is a critical computing resource, and efficiently sharing it among several tasks is another challenge.

At current stage, the architecture design of the reconfigurable architecture is studied by many. The issues in the physical design is rather well-understood, and moving towards realization of dedicated reconfigurable device is not posing any prohibiting technical difficulties. The programmability of the reconfigurable architectures is still being discussed, and many tools and methodologies have been proposed. Due to the variety of reconfigurable systems, the study on tool chains are hard to converge, and most solutions take ad hoc approaches based on the architectures. The run-time system design is in a similar status as the programmability study is in. The complexity and variety of reconfigurable systems make it difficult to capture and generalize the run-time behavior of the reconfigurable system, thus makes it hard to develop a run-time system and assess its efficiency. The design verification and testing has been discussed by a few, but moving into verification is still not a concern for most people.

### 1.5 Thesis Outline

In our study, we would like to acquire a thorough understanding of the reconfiguration before we decide what issues are important at the current stage, and what possible technical support is available to build future technologies upon. We took the bottom-up approach to understand the reconfigurable architectures, thus our study went through the following four phases.

A survey of the reconfigurable architecture has been carried out in the first phase, and the findings of our study are documented in chapter 2. We noticed that the coupling between the fixed logic and the reconfigurable logic has huge impact on the architecture scalability, configurability and programmability etc, and therefore dedicated most of the rest of the study to investigate this issue.

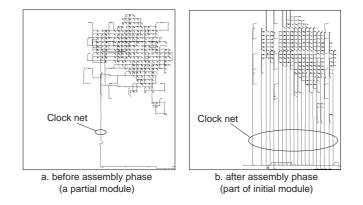

Then we moved on to the study of the commercial FPGA, and experimented on the partial reconfiguration design flow supported by the Xilinx Virtex FPGAs. The objective of this study is to get a general understanding of what stateof-the-art commercial reconfigurable devices can achieve, what technologies are mature and feasible in practice, what technologies not being put to practice are actually feasible and crucial, and most importantly, what unconventional physical characteristics reconfigurable systems have. During our experimentation, we noticed that several limitations exist in the current Xilinx tool flow as well as in the architecture, and documented them in chapter 3. We also described what urgent issues need to be addressed to make the current Virtex FPGA a more suitable platform for building more complicated reconfigurable architectures.

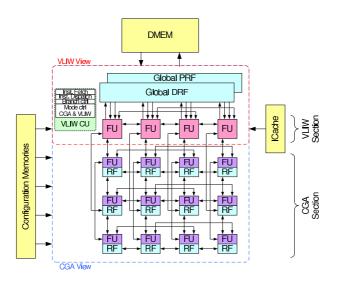

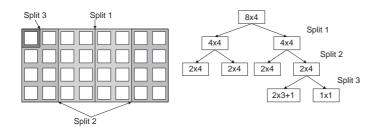

To acquire a better understanding of the datapath-coupled reconfigurable architectures, we carried out some study on the state-of-the-art ADRES architecture developed at IMEC, Belgium, and extended it to support the simultaneous multi-threading (SMT). Our approach and conclusions are documented in chapter 4 of this dissertation. From this exercise, we gained the knowledge of the design pitfalls of datapath-coupled architectures, and proved that the threading is a feasible and important solution for improving the performance and scalability of these architectures.

After carrying out many studies in various areas, we are convinced that the coprocessor-coupled architectures have great potential, but there hasn't been enough investigation on many critical issues of these architectures yet. We propose our general system-level simulation framework, COSMOS, for further study

on coprocessor-coupled reconfigurable architectures. We demonstrate how the COSMOS model can be used for acquiring a better understanding of the reconfigurable architectures' dynamic behavior, and for evaluating the performance of a reconfigurable system. The result is documented in chapter 5.

Chapter 6 concludes our work and discusses the perspectives of the reconfigurable architecture research.

### Chapter 2

# Survey of the Dynamically Reconfigurable Systems

In the last two decades, large number of reconfigurable architectures have been proposed, along with many new technologies. In general, the state-of-the-art reconfigurable systems still resemble the F+V system proposed by Gerald Estrin decades ago. The variable part of the reconfigurable architecture does the arithmetic computation to speed up the execution of user programs, while the fixed part offers a consistent programming interface to the programmer and supervises the use of the variable part at run-time. Quite a few architectures have shown great potential in accelerating user applications and improving energy-efficiency.

The architecture design in this area is getting mature, and many new technologies have been proven feasible. However, people started to notice that the dynamic behavior of the reconfigurable system is very different from that of the traditional architectures. Improving the run-time system efficiency, the reconfigurability and the programmability of the reconfigurable architectures are bigger challenges than the architecture design. Recently, the lack of integrated high-level compilation tools and efficient run-time systems starts to restrain the dissemination of reconfigurable system, so the focus of the mainstream research is currently moving towards these areas to provide the missing pieces. Before we can understand where the current research trends are going and pinpoint what critical challenges lie ahead, we want to understand what has been done, or proved, by others and what is the state-of-the-art. We start our study by surveying the research activity in the last couple of decades, and documenting our observation in the next four sections. The first section gives a general overview of the architecture proposed in recent research, and discusses the new technologies being used. The second section focuses on the reconfiguration strategies, and discusses their impact on system-level design. The third section discusses the known run-time system design issues and some proposed strategies to address them. The fourth section discusses the methodology design issue currently under study and some general direction being taken to approach them. In the final section of this chapter, we conclude how the state-of-the-art motivates us to continue, and what is most relevant in the near future for us.

### 2.1 Architecture

The deterministic architecture design issues of reconfigurable systems are the host-reconfigurable unit coupling and the reconfigurable logic block granularity. Also, several recently proposed FPGA technologies contribute to the architecture design. In the last few years, all these three areas have evolved rapidly, and a classification is necessary.

### 2.1.1 Reconfigurable unit coupling

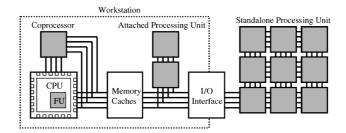

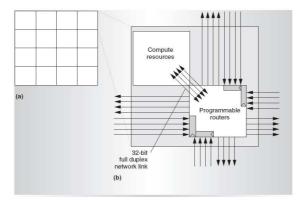

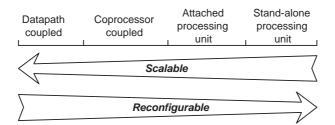

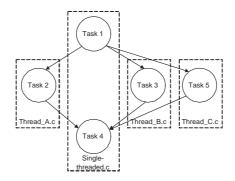

The reconfigurable unit (RU) can be coupled into the host architecture in four ways, as shown in figure 2.1 [23]. It can be a reconfigurable functional unit (FU) built into the datapath, a coprocessor, an attached reconfigurable unit or an external stand-alone processing unit. The coupling method has deterministic impact on the operating system design and the methodologies, and is the most important decision a designer has to make.

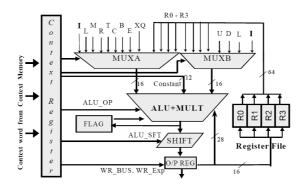

### 2.1.1.1 Datapath-coupled reconfigurable architectures

The reconfigurable units can be embedded into the datapath of a processor as a special function unit. Most of the known architectures in this class are similar to RISC processors or Very-Long-Instruction-Word (VLIW) architectures. But unlike VLIW architectures, this class of Reconfigurable architectures demands complicated compiler design due to the flexible instruction set. During

Figure 2.1: Different coupling methods of reconfigurable units [23]

compile time, the complicated and regular arithmetic operations are identified and extracted by the programmer's guidance[58] or by profiling[85]. If executing these operations on an RU is beneficial, a special RU-operation instruction with reconfiguration op-code extension will be generated from the compiler, and the extracted arithmetic operation will be synthesized into an RU configuration bitstream with dedicated synthesis tool. At run time, several RU operation bitstreams are stored on the RU, and the dedicated op-code extension bits selectively switch the bitstream enabled on the RU when an RU operation needs to be executed.

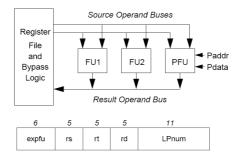

PRISC is an early example of such systems [85]. The datapath and the instruction format of PRISC are shown in figure 2.2. In the PRISC instruction format, the op-code *expfu* indicates whether the current instruction invokes RU, which is called PFU in the figure. The field *LPnum* indicates which pre-synthesized configuration should be loaded onto the PFU. The PRISC PFU is more flexible and efficient than a normal functional unit, but the size of it is still rather small (30.5K transistors).

Figure 2.2: PRISC datapath and instruction[85]

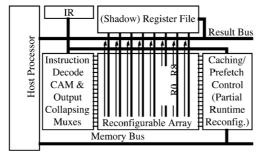

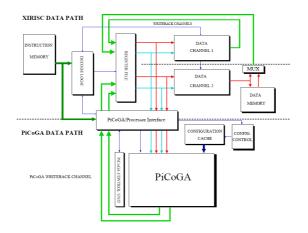

The Chimaera architecture [47] and XIRISC[64][65] architecture shown in figure

2.3 are a couple of examples of more recent datapath-coupled architectures. The Chimaera system has an array of reconfigurable columns, several of which can be used to map one algorithm. It allows the configuration of several algorithms to co-exist in the RU, and programmers can use this feature to enable configuration caching. Similarly, the XIRISC system's reconfigurable unit, PicoGA, is partitioned into 3 blocks. Depending on the complexity of the algorithm mapped onto the PicoGA, blocks can be combined if necessary. PicoGA also uses redundant memory to achieve configuration prefetching and caching. The XIRISC prototype costs 12M transistors, and more than 1/3 of the total area is occupied by the PicoGA unit.

a) The Chimaera datapath

b) The XIRISC datapath

Figure 2.3: Other recent datapath-coupled architectures

In general, this class of reconfigurable systems has the tightest coupling between

the host and the RU. The RU is easy to access by the host, and it is frequently reconfigured during function execution. The operating system support of such a system is simple, and the compilation is straight-forward. The drawback of such system is the regularity of the memory-to-RU interface and the scalability of the RU, and they limit the type and the size of the digital circuits that gain benefit from the RU.

#### 2.1.1.2 Reconfigurable coprocessor

The RU coupled with the host as a coprocessor has direct access to the host's memory hierarchy. The host usually controls the coprocessors through message passing instead of instruction. Interaction between the host and the RU is much less frequent compared to the datapath-coupled systems, and the host and the RU can execute different applications concurrently and independently.

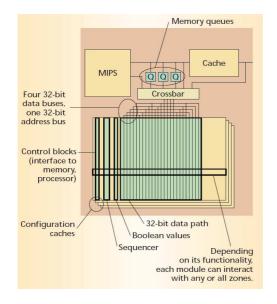

The GARP system[48][21] shown in figure 2.4 is a typical architecture of this class. The host MIPS II processor handles the configuration, task execution control and data transfer between the MIPS II and the RU. The Chameleon CS2112 chip[96] and the MorphoSys[90] have similar structures, but their RUs are further optimized for configuration data size reduction and configuration caching. The MaRS system[95] is an advanced version of the MorphoSys. The RU of MaRS is shared by a group of processors, and the memory modules are distributed among the processors in order to increase bandwidth.

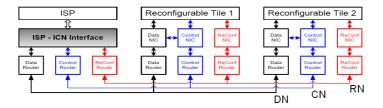

The work from [70] experimented on the Xilinx Virtex-II device. The architecture used the existing on-chip instruction set processor PowerPC as the host, and divided the rest of the FPGA into several reconfigurable blocks. These reconfigurable blocks are connected with 3 on-chip networks (NoC), as shown in figure 2.5. These NoCs include a reconfiguration network (RN), a data network(DN) and control network(CN). The host is responsible for controlling all the networks and activities.

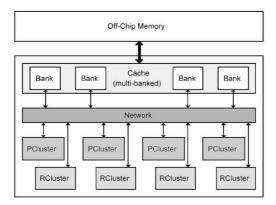

The Amalgam processor[55][38] shown in figure 2.6 is another NoC based architecture. In Amalgam, there are totally 4 reconfigurable units (RCluster) and 4 programmable units (PCluster). Managing so many computation resources at run-time is complicated, so the control of this system relies heavily on static analysis. The DART system[27][26][28] has 4 clusters of reconfigurable units, and the host processor is simply a task control unit. This architecture is suitable for linear and computationally demanding applications, but is not very flexible for general purpose computation.

The RU of this class of architectures is scalable, but when the RU is upscaled

Figure 2.4: The GARP processor architecture

Figure 2.5: The NoC support for the reconfigurable system

to a certain extend, dividing an oversized RU into several smaller ones is more flexible and practical. Using complicated buses or NoCs to support a multi-RU system is often necessary, but the overhead and bandwidth requirements always pose design challenges. Also, having large RU enables designers to map complicated algorithms onto the RU, but it also increases the overhead of dynamic reconfiguration, e.g. long reconfiguration latency. What is also worth noticing is that the co-processors often can directly access the main memory or even the cache, thus creates two problems. First, the bus is sometimes overloaded, and it leads to stalling on both RU and the host. Second, if data consistency can not be guaranteed through static analysis, the cache consistency issue need to be addressed at run-time, thus the hardware and the performance overhead will increase.

Figure 2.6: The Amalgam architecture.

### 2.1.1.3 Attached processing unit

The attached processing unit is coupled to the host through ports and external bus. The host system's memory is not directly accessible to the RU, and the RU functions are very independent. The RU is controlled by the host through device drivers or the operating system API call. Due to the inconvenience, the RU is rarely configured. The single chip solution of this class is much less efficient compared to the coprocessor architecture, and the RU is often built with several commercial FPGAs.

The GECKO system[101] is an experimental system that belongs to this category. This system's host is a complete COMPAQ iPAQ pocket PC, and the RU is a Xilinx Virtex-II device. These two parts have their own clock domains, power supplies and memory systems. One of the most interesting objectives of this project is to study the dynamic task migration, e.g. how a task can be moved to run on the host or the RU, and what the cost is for doing so.

Most of the commercial FPGA-based development systems belong to the category of attached reconfigurable processing unit. These systems are usually infrequently reconfigured by a host system, but they also have their own memory and peripheral devices. These architectures' coupling is very weak, and can usually be reconfigured through many standard interfaces.

#### 2.1.1.4 Stand-alone processing unit

The stand-alone processing unit coupled reconfigurable system is the most loosely coupled architecture. The reconfigurable unit can even be a workstation accessed through the ethernet. The RU is usually wrapped up by many layers of software, from network protocol to device drivers, and the users of such system may have no knowledge of the RU. This type of system has high volume, and is scarcely reconfigured.

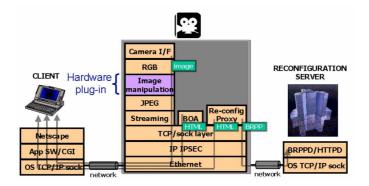

The Cam-E-Leon system is a typical stand-alone processing unit. Figure 2.7 shows the architecture of this system. User of this system accesses services by using a web browser and remotely gets the image processing service.

Figure 2.7: The Cam-E-Leon system layer

The attached processing unit and the Stand-alone processing unit have relaxed size constraints, but the communication cost between the host and the RU is very high. These systems fit for dedicated and highly complicated operations, and the dynamic reconfiguration means little to them. Both of these classes are well-understood and widely used, thus are not the focus of the current reconfigurable system research.

### 2.1.2 Logic block granularity

The logic block granularity is one of the primary factors that decides the system performance. The granularity of the reconfigurable logic is defined as the complexity of the atomic logic unit addressed during logic mapping. In general, finer-grained logic block is more flexible when being used to implement digital circuits, while coarser-grained logic requires less configuration memory and can achieve faster reconfiguration.

#### 2.1.2.1 Fine-grained logic block

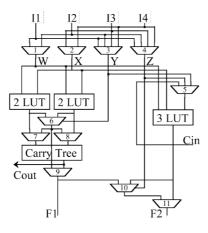

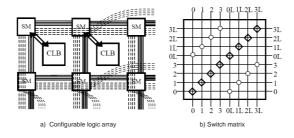

The most commonly used configurable logic blocks (CLB) are fine-grained. The input and output data of the fine-grained unit are single-bit wide, as shown in figure 2.8. The look-up table (LUT) is the most frequently used building-block of CLBs, especially in commercial FPGAs.

Figure 2.8: The fine-grained logic block from Chimaera system

The fine-grained reconfigurable unit suffers from the costly reconfigurable overhead. Due to the high volume of the configuration data, the storage requirement of these system is usually very high, e.g. approximately 30% of total chip area for commercial FPGAs. Also, the latency to load a configuration into an RU is proportional to the configuration data volume, thus fine-grained RU often suffers from slow reconfiguration. These shortages make the caching/prefetching of configuration difficult, but not prohibitive.

The greatest advantage of the fine-grained system is the flexibility. Any algorithm can be mapped onto the fine-grained logic device, and the bit-level operation-intensive applications use the fine-grained systems very efficiently. Due to the low granularity, these devices also have the highest utilization rate if compared to the coarser-grained devices.

#### 2.1.2.2 Medium-grained logic block

The medium-grained logic block is a compromise between flexibility and reconfigurability. Figure 2.9 shows the medium-grained logic unit from PicoGA's reconfigurable unit [65]. As shown in the figure, the medium-grained logic block is very similar to the fine-grained version, except for the input/output data bit-width. Most of the medium grained systems are 2 or 4-bit wide.

Figure 2.9: The medium-grained logic block from PicoGA system

The medium-grained systems are more friendly to reconfigure, but harder to map some application on. The utilization rate of the logic device is normally lower than that of the fine-grained systems, but for applications that do not perform many bit-level logic operation, the medium-grained systems are still practical and efficient.

### 2.1.2.3 Coarse-grained logic block

The coarse-grained logic has no regular form. The reconfigurable unit of the MorphoSys is an 8X8 array of 16-bit ALU, as shown in figure 2.10. The Montium tile processor[84] has a similar logic block, but extended with a butterfly-shaped MAC unit. The ADRES [75] architecture has up to 64 32-bit heterogeneous functional units as basic logic block.

The coarse-grained logic block could be more complicated than an instruction-

Figure 2.10: The coarse-grained logic block from the MorphoSys system

set processor. The RAW processor[97] is a compiler-directed reconfigurable system. As shown in figure 2.11, it is constructed with 16 tiles of independent processing units. In each tile, there is a MIPS-style processor interfaced with a programmable router. At compile time, single task will be partitioned and mapped onto one or more adjacent tiles. The RAW compiler is architecture-conscious, and orchestrates the routers statically. The programmable router layer of this system is one of the early NoC.

Figure 2.11: The RAW processor architecture

The coarse-grained logic block has the lowest reconfiguration overhead in terms of memory cost and reconfiguration latency. Many architectures employ ALU or similarly coarse-grained logic unit as the basic logic block, thus instruction-logic block mapping is more frequently used for these architectures instead of logic synthesis. This enables designers to program their applications in high-level language and apply advanced compilation technologies to use the architecture optimally.

#### 2.1.2.4 Mix-grained unit

As mentioned earlier, architectures with lower logic block granularity fit narrower application domain. To improve the robustness and flexibility of these reconfigurable architectures, mix-grained architecture was introduced.

The technical proposal in [72] discussed a hierarchical architecture. The hierarchy of this reconfigurable unit is a quadric-tree. The lowest-level cluster is composed of an arithmetic node, a bit-manipulation node, a finite state machine (FSM) node and a scalar type operation node, since the operations of these four different algorithm domains are very incompatible. The four functional nodes are recursively clustered by a matrix interconnect network. The logic granularity of these different nodes is apparently different.

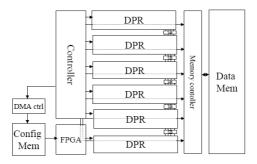

Another example is the DART architecture. The reconfigurable cluster of the DART has six coarse-grained logic unit (DPR) and an FPGA, as shown in figure 2.12. The DPR is used to execute most of the instructions, but the bit-level manipulation is handled by the FPGA. For an architecture like this, the task partitioning is another challenge.

Figure 2.12: The mix-grained DART reconfigurable unit

The logic mapping of the mix-grained RU is more complicated than that of the mono-grained RU. If an RU is comprised of both the fine-grained and the ALU-grained logic, two of which require different compilation/synthesis tools, the integration of the tool will be difficult. Also, applications may need to be partitioned in an early stage to ease the compilation and the synthesis, and optimal partitioning will be a great challenge.

#### 2.1.3 FPGA technology

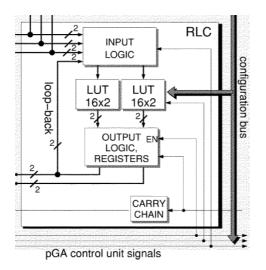

The traditional FPGA suffers greatly from reconfigurable overhead. Without applying more advanced FPGA technologies, dynamic reconfiguration is only suitable for very small-scaled system. The most important technologies that increase the FPGA's reconfigurability are the run-time partial reconfiguration and the multi-context design. Routing issue of the commercial FPGA has always been a great challenge, and some other work proposed some means of simplification to this issue.

#### 2.1.3.1 Partial reconfiguration

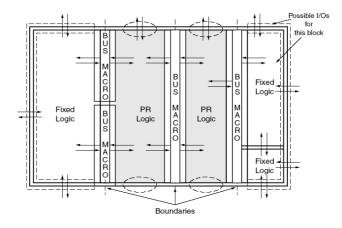

The partial reconfigurability allows part of the FPGA to be reconfigured, while the other part is running. This function is already supported by many commercial FPGAs, e.g. Xilinx Virtex family and ATMEL at6000 series[1].

The Virtex-II FPGA, as an example, can be divided into several separated blocks at very early design phase. The separated blocks, which are called PR logic in figure 2.13[11], are independent, and they communicate to the surroundings through dedicated ports. The boundary of each block cannot be changed once the algorithm starts running on the chip, but the algorithm mapped on the blocks can be reconfigured at run time. Since the reconfigurable block's boundary is rarely changed, the system is equivalent to a group of smaller FPGAs.

Figure 2.13: The partial reconfigurable logic of Virtex FPGA The partial reconfiguration opens up many possibilities, e.g. it enables the

hardware context switching and multi-tasking. If the system has a large amount of redundant reconfigurable blocks, the idle blocks can be used for configuration prefetching. However, the current FPGAs and their tool chains are not very friendly to use, and killer application is yet to be found.

#### 2.1.3.2 Multi-context FPGA

Conceptually, the logic layer of an FPGA is an array of configurable logic blocks and interconnection nodes, and the configuration layer is physically a collection of distributed SRAMs or register files that store the configuration data of the logic layer. Unlike normal FPGA, which has one configuration layer and one logic layer, multi-context FPGA has multiple configuration layers but one logic layer, and all the configuration layers configure the same logic layer. Each configuration layer can store one set of complete configuration data and the intermediate data of the whole logic layer, thus is called one context. These configuration layers are connected to the logic layer through a multiplexing circuit, and the multiplexing circuit selects which configuration layer currently activates the logic layer. For those configuration layers that are inactive, they can be used as configuration caches. Most of the multi-context architectures can change their configuration in only one clock cycle, if the configuration is properly cached.

Xilinx has proposed a time-multiplexed FPGA[98] based on their XC4000E FPGA. This time-multiplexed FPGA has eight configuration layers and one logic layer. The reconfiguration loading time of the whole chip is only 5ns, which gives almost no reconfiguration penalty. Their proposal has not been commercialized, but their idea is adopted by many other research group. The DRLE system is also an 8-configuration system. In their work[35] the trade-off between the energy-latency product and the area has been studied. Their result shows that the 4 or 8-context FPGA is the most efficient for their architecture. The MorphoSys has coarse-grained logic block, and can store up to 32 configurations on-chip. The PicoGA FPGA has 4 configuration RAMs. As mentioned before, the PicoGA is partitioned into 3 blocks, thus one context switching can switch in up to 3 new functions.

The multi-context design provides configuration caching, which helps to hide the reconfiguration overhead. This technique also enables reusing the logic layer for executing different parts of a task, thus reduces the size of the logic layer. A main drawback of this technique is the high volume of the storage, thus is mostly applicable on coarser-grained systems.

#### 2.1.3.3 Alternative FPGA design technologies

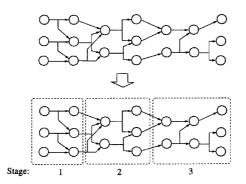

To make the reconfigurable architecture more flexible and user-friendly, many effort has been put into reducing the latency of creating a configuration from a netlist. Here is an example of how the architecture simplification can reduce the placement and routing latency.

The flexibility of fine-grained configurable logic block is not fully used by many applications, and the research described in [66][67] propose to simplify the fine-grained FPGA without significantly losing performance. As shown in figure 2.14a, their routers (SM) of each configurable logic block (CLB) link to their 1-hop neighbors and their 2-hop neighbors with solid and dashed lines, respectively. The internal structure of the router offers very limited connectivity: the wire from one side of router can only be connected to the wires of the other three sides with the same name, as shown in figure 2.14b. The result of the project shows that the WCLA FPGA, combined with the tool chain ROCPAR from the same group, are comparable to XILINX Virtex-E FPGA. Due to the simplified hardware structure, the execution time of the ROCPAR is on average 40 times faster than XILINX tool. One extra benefit is the whole tool chain ROCPAR, from logic synthesis to P&R, can be fit into the cache memory of the ARM processor.

Figure 2.14: The WCLA FPGA routing[66]

# 2.2 Reconfiguration strategy

Depending on the coupling of the reconfigurable units, reconfiguration can be performed differently. Stand-alone processing units and attached reconfigurable units are usually less frequently reconfigured due to the device complexity and memory bottleneck, but they are scalable, reliable and simple to use. User of these devices are not very interested in the device flexibility, but mostly in the computation power, thus the reconfiguration of these devices are not interesting enough to study.

The coprocessor-coupled and the datapath-coupled architectures are more flexible and versatile, and the reconfiguration of these architectures are frequently discussed. They are both the main focus of the run-time reconfiguration (RTR) research, but due to their different characteristics and potential, they are reconfigured differently. The coprocessor-coupled architectures have great potential in scalability and performance, but are also the most complicated to reconfigure.

#### 2.2.1 RTR of the datapath-coupled architectures

The datapath-coupled architectures are very frequently reconfigured. The PRISC system can reconfigure its PFU every clock cycle if the configuration is preloaded into the PFU. Once the reconfiguration occurs, the whole RU is updated. The Chimaera system and PicoGA system's RUs support partial reconfiguration, thus several configurations can co-exist on the RU. Comparing to the system that cannot be partially reconfigured, The Chimaera system and PicoGA system are not very frequently reconfigured, but it is very normal that their RUs are reconfigured several times when executing one task.

The datapath-coupled architectures are relatively small and regular. For systems like PicoGA, the reconfigurable array is homogeneous, has regular structure and is partitioned. Thanks to these characteristics, the dynamic reconfiguration overhead is manageable. The most frequently used strategy for these architectures is to statically explore the fine-grained parallelism, e.g. instruction-level parallelism (ILP) or loop-level parallelism (LLP), generate the configurations, and plan for the reconfiguration statically.

#### 2.2.2 RTR of coprocessor-coupled architectures

Multi-tasking is one of the greatest potential of the coprocessor-coupled system. Depending on the size and the number of the co-processing RUs, the multi-tasking architecture varies, so is the RTR strategies. In general, the two main multi-tasking strategies are the single-coprocessor multi-tasking (SCMT) and the multi-coprocessor multi-tasking(MCMT).

#### 2.2.2.1 RTR of SCMT system

The SCMT systems usually have a large non-partitioned reconfigurable unit that allows several tasks to run on it concurrently. Figure 2.15[45] shows the run-time multi-tasking strategy of such systems. Each shaded rectangular area on the FPGA models a task or a kernel of the task.

Figure 2.15: The SCMT system[45]

There are several design issues for SCMT systems. Firstly, the task allocation results in fragmentation on RU. Several research groups[24][45] have proposed algorithms to defrag the free space. Most of the defragmentation methods require reallocation of the issued tasks, which could be extremely time-consuming to do. Secondly, the rectangular model of the tasks is inadequate for many tasks, and more realistic models greatly increase the execution time of the task placement algorithms. Finally, the task communication interfaces must be persistent or at least traceable after reallocation, and run-time rerouting might be needed to handle the task communication channel.

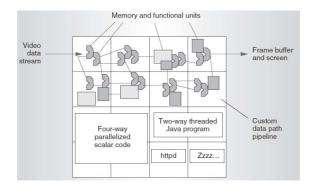

The most critical performance bottleneck of the SCMT system design is the reallocation of the tasks. The issuing, allocation and reallocation of a task must occur at system run-time, which is not supported by the traditional FPGA design methodologies. Xilinx has contributed the JBits[40][39], a Java based program that can manipulate the FPGA bitstream at run-time, to support run-time reallocation. The JBits can access the logic and routing blocks when the FPGA is powered-on, reprogram any part of the circuit, and enable the updated part. The JBits operates at the logic level, which not only gives great flexibility but also results in many drawbacks. It is manual, and requires the programmer to have very good understanding of the FPGA. It also lacks a verification tool that can exam the modification and verify the timing of the final results.

JBits has stimulated many other research activities. In order to hide the low-

level detail of the FPGA, Xilinx developed several other tools running on top of the JBits. Run-time parameterizable cores[41] are extended from the traditional static core models. Due to its dynamic parameterizable nature, the bitstream of an IP core can be dynamically synthesized and downloaded into the FPGA. The interconnects among cores are handled by using a stitcher class. User of the system only need to manually allocate the interface of the cores and stitchers, and the low level details will be automatically handled by the Java program. JRoute[54] is another automated routing program from Xilinx. JRoute supports more flexible routing/unrouting features and functional debugging. User of JRoute and the Run-time parameterizable core methodology needs very little knowledge of the FPGA, and their designs are portable. The software PARBIT[49] generates the partial bitfile of a given task and rearrange a running FPGA bitstream to fit the partial bitfile into the bitstream. This program extends the idea of JBits into task level. The CLB reallocation software introduced in [37] uses JBits as part of their reallocation flow. The proposed reallocation tool is capable of reallocating the circuit when it is running, thus hides the reallocation overhead.

The SCMT system's performance depends on the run-time RU management, and the task reallocation adds significant overhead to the reconfiguration latency. The recent FPGAs can support task reallocation, but the efficiency is rather low. The design methodology is currently under research, and there are only few architecture-OS combinations proposed.

Multi-context FPGA can eliminate the need of task reallocation. If we assume that each context of the FPGA stores the configuration of one task, then the tasks can share the reconfigurable unit in time rather than in space. This strategy has several disadvantages. Firstly, multi-context architectures normally have less computation resource due to the high memory cost, thus the size of the task that can be fit into the RU is more limited. Tasks will have a tighter area constraint when being synthesized, and larger tasks have to be partitioned. Secondly, tasks cannot be executed in parallel anymore, but have to be executed in turn. The overall performance of the system might be even lower than the systems suffering from task reallocation penalties. Finally, inter-task communication might have to go through special memory device, since communicating tasks can not be active at the same time. In general, Multi-context systems are also hard to design on SCMT system, and practical methodology and run-time system design is yet to be seem.

#### 2.2.2.2 RTR of MCMT system

The MCMT systems have an array of reconfigurable unit tiles. A tile of RU could be a coprocessor, an FPGA or a partially reconfigurable module of an FPGA. The reconfigurable units are often small and not able to execute a complete application. Complicated tasks are accomplished by a group of interacting units that are connected with NoC or bus. Figure 2.16 shows the 16-tile RAW processor running 4 tasks concurrently as an example.

Figure 2.16: The multi-tasking of the RAW processor[97]

The MCMT system is scalable, flexible and easy to control at run-time. The task model of the MCMT system is similar to that of the multi-processor system, but there are extra (re)configuration delay during task initiation and reconfiguration. The run-time support of the MCMT system only need to assign a task to a certain tile and setup the inter-task communication, hence is considerably simpler than that of the SCMT systems. The executed algorithm is partitioned and optimized at compile time, therefore the reconfiguration overhead is predictable and small. The reconfiguration of a tile is systematic, thus can be optimized by many existing technologies. The drawback of the MCMT design is the complicated compilation system, but many existing embedded system design technologies can be adopted.

# 2.3 Operating system design

The coupling of the reconfigurable units determine what operating system (OS) support is relevant. For datapath-coupled reconfigurable units, the RU is managed as a flexible datapath of the host processor and requires little OS support. For reconfigurable coprocessor, multi-processor OS design can be adopted. For

attached processing unit, the OS manages the RU as a peripheral device. For stand-alone processing unit, the RU is usually a server with its own OS, and can not be accessed directly by other users. Due to the increasing complexity of the reconfigurable systems, traditional OS designs must be extended in many aspects, and some of the features need to be implemented in hardware to achieve higher efficiency.

#### 2.3.1 Reconfigurable unit virtualization

From the programmer's point of view, the reconfigurable computing resource is always there to speed up the application execution, but in reality, the RU is a limited resource. If several tasks need to access the RU during a short period of time, and the total resource requirement exceeds the RU's capacity, the RU must be shared by tasks in time. In this case, which can be quite common, a virtulization mechanism must be built into the OS to facilitate this.

Such virtual reconfigurable resource management system is similar to the virtual memory management. But in contrast to the virtual memory management, RU has more complicated physical constraints, and the virtualization should partly be done at application compile time. For instance, larger tasks that can not be fit into the RU should be partitioned during compilation in order to reduce the run-time overhead. However, this research topic has not been recognized as an urgent issue to address. Even though it has been mentioned by many, solid solution are yet to be seen.

#### 2.3.2 Virtual memory management

For systems that can support multi-tasking, the data allocation problem should be addressed. Reconfigurable systems that can support multi-tasking is often capable of running complicated algorithm. In case the local memory in a reconfigurable tile is not sufficient to hold the intermediate variable, the main memory access from the tile is necessary. The virtual memory (VM) management of the main memory access comes into the picture.

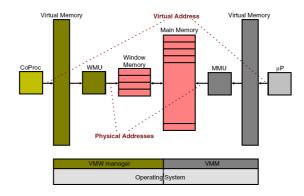

A simple method of managing VM in MCMT system is to maintain a table in the OS. Every entry of the table corresponds to a reconfigurable tile. When a task is issued to a reconfigurable tile, the corresponding table entry is updated with the virtual address of the task. When a tile tries to access the main memory, the data address is translated by the OS through the corresponding table entry. The work described in [102] is a hardware implementation of the concept. As shown

in figure 2.17, the memory management unit (MMU) unit translates the physical address from the processor to the main memory. The window management unit (WMU), which is the MMU for the coprocessor, performs the same function at coprocessor side.

Figure 2.17: The Virtual Memory Management hardware[102]

### 2.3.3 Inter-task communication

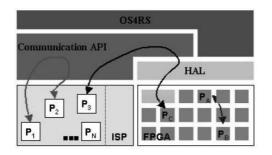

The inter-task communication of the reconfigurable system differs greatly from that of the traditional OS. The tasks of the reconfigurable system could be located in the host processor as software or in the RU as hardware. In order to enable the inter-task communication between the host processor and the RU, an abstraction layer of RU should be built into the OS[81][77]. If the abstraction layer is well-designed, the traditional message passing is still appropriate for the reconfigurable system.

As shown in figure 2.18, the communication can be categorized into 3 types: the software-software, the software-hardware and the hardware-hardware communication. The software-software communication on the host processor is similar to the inter-task communication of the traditional system. The software-hardware communication passes through the hardware abstraction layer (HAL). In this case, the HAL is responsible for translating the OS specified task ID to the physical reconfigurable tile. The hardware-hardware communication can be handled by several manners. The straight-forward method is to pass the message to the OS and let OS transfer the data among different reconfigurable tiles through HAL. This method is easy to implement, but the data bus becomes the performance bottleneck. A more complicated but scalable communication method is achieved by the cooperation between the OS and the on-chip network that

connects the reconfigurable tiles. The OS is only responsible for maintaining a routing table that keeps track of the location of the active hardware tasks. Once a message passing starts, the message source task fetches the physical location of the destination task from the routing table, packs the location information into the message and sends the message through the on-chip network. The MCMT system is very suitable for this communication scheme due to its multi-threading nature.

Figure 2.18: Three possible cases of message passing[81]

# 2.3.4 RU-OS interface

The choice of the interface method between the operating system and the reconfigurable units depends on the coupling between the host processor and the RU. For datapath-coupled systems, the compiler has a global view of the whole architecture and orchestrate the software execution at compile-time. At run time, software is directly executed on the reconfigurable hardware without any operating system interface support.

The architectures coupled in other methods usually need a device driver built into the operating system, unless the architecture is very simple. The driver can offer an abstract view of the underlying RU, buffer the input/output data and solve resource sharing problems. As shown in figure 2.18, the hardware abstraction layer hides the detail of the hardware implementation on the FPGA by offering a simple inter-task communication interface to the software. The HAL keeps track of the use of the reconfigurable tiles and location of the service, and if conflicts need to be solved, a message buffer can be implemented in the HAL.

The work described in [19] focuses on the single-thread applications. For each active procedure, no matter if it is implemented in hardware or software, there is a corresponding interfacing stub registered in the OS. Caller calls the callee with

remote procedure call through the stubs and locate the required service without even knowing the location of the callee. Their device driver also supports the configuration readback function and partial configuration function.

#### 2.3.5 Hardware context switching

Hardware context switching is difficult to handle for the following reasons. Firstly, context switch latency is normally high, and it adds to the task execution time. Secondly, loading a configuration into an RU costs memory bandwidth, and in turn lowers the overall system performance. Thirdly, storing a digital circuit's current state means storing all the data in its memory element, and it can be tricky and costly to do. Without proper optimization, hardware context switching causes huge performance penalty.

There are several methods to reduce the context switching overhead. The first one is to take the context switching overhead into account when assigning task priority. E.g. periodic tasks that demand high data bandwidth should be given a higher priority than the other tasks, thus be preempted less frequently. The second method is to use the RUs that can support bitstream readback. The readback should be able to access the status of all the internal registers and RAMs[60]. The third method is to define certain context switching points[78] in the application program. Experienced programmers can choose the best place for the context switching to reduce overhead cost.

# 2.4 Design methodology

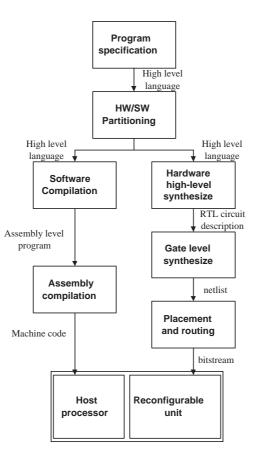

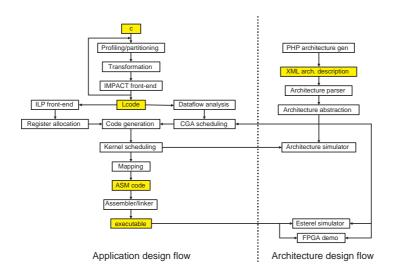

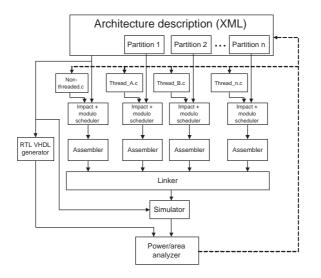

The reconfigurable system can speed up the application execution significantly, but the performance gain is not easy to obtain. The programmers must have ample knowledge of the underlying architecture and great deal of experience in parallel programming in order to fully utilize the architecture's computation power. As shown in figure 2.19, the design flow of the reconfigurable system's application is also much more complicated than usual software design flow. It usually requires several software engineers and hardware engineers working together to program the reconfigurable systems, and the application development cycle can be very long.

The design automation is recognized as the crucial issue if the reconfigurable system wants to be adopted by the mainstream software engineers. When designing an application, the manually optimized application is the most performance-

Figure 2.19: A typical design flow of application implementation for reconfigurable system[81]

optimal, but it takes too long time to design. Automated design tools still have only limited ability to explore the design space and take advantage of the RU, but are much faster than the completely manual approach. A compromise of the two extremes is to let programmer control part of the design flow. The early decisions in a design flow have the most significant influence on the performance, thus the partitioning and the high-level hardware design are often done under the supervision of programmers.

The objective of the design automation is to explore the application parallelism, take full advantage of the available on-chip resource and partition the algorithm efficiently into hardware and software without violating the resource and timing constraints. The programming language, the compiler and the synthesis tool play the most important rolls in the design flow. Many research of these areas have been done, and quite a few interesting results have been seem.

#### 2.4.1 Programming

#### 2.4.1.1 Register transfer level design

VHDL and Verilog are the most well-known Register Transfer Level (RTL) hardware design languages. Experienced reconfigurable system programmers can parallelize the application and manually map the algorithm on to a given RU with these languages. The timing of the design is manually constrained and optimized, and the use of the registers in the algorithm is pre-defined. The designer has control over all the details of the algorithm implementation, thus the development circle is very long.

SystemC extends the ANSI C with its own library. The SystemC-based FPGA design flow is very similar to VHDL/Verilog based design flow, although it offers a more friendly programming environment. The design is still at RT level, thus the clock signal and the circuit structure are explicitly defined by programmers. Since SystemC is based on C, it can be used for both software and hardware designers.

JHDL[15] is a Java based RTL design tool. Compare to SystemC, JHDL has explicit mechanism that supports reconfiguration. In JHDL, FPGA is represented as a *Reconfigurable* class, and the reconfiguration process is represented by the *Reconfigurable* object instantiation. When the hardware is realized, the interface between hardware and software is interpreted by device drivers. Programmers can manually partition the application into software parts programmed by usual Java semantics, and reconfigurable hardware parts encapsulated by reconfigurable class. The design can be easily co-simulated in Java environment.

#### 2.4.1.2 High-level programming language

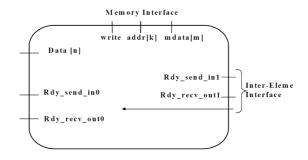

Cliff is an embedding of a network-domain specific language[56]. The fundamental unit of Cliff is an **element**. These elements have uniform interface, which is shown in figure 2.20. Communication among Cliff elements is based on threeway handshake protocol. When synthesized, all the elements are implemented as FSM with communication state and user state.

The work described in [79] generates RTL hardware description from DSP as-

Figure 2.20: The interface of the cliff elements [56]

sembly code. Their compiler takes assembly language as input and decompiles it into Control and Data Flow Graph (CDFG). After the CDFG is optimized, it is translated into another intermediate abstract syntax tree that can be converted into RTL VHDL or RTL Verilog.

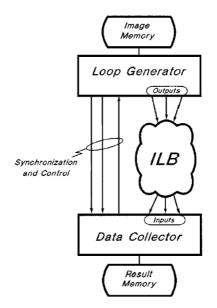

SA-C is a C-based single assignment language that targets image processing algorithms [80]. It supports integer and fixed-point number with user specified bit width[31]. The pointer and recursion are not supported due to the single assignment nature of the language. The body of a SA-C function is constructed with an input data window, a set of loops and a set of data return points. When VHDL code is generated from software function, a uniform hardware model that structurally represents each part of the software is used. As shown in figure 2.21, the loop generator, which is translated from the input data window, fetches data from the memory and sends them to the arithmetic unit called inner loop body (ILB). When ILB finishes the computation, the results will be stored in the memory by data collector, which is translated from the data return point. The ILB unit is synthesized from the optimized software loop. Because the ILB is fully combinatorial, its latency varies according to the software loop complexity. The timing and control of the computation process is handled by the loop generator and data collector. The SA-C also supports external VHDL component plug-ins and pragmas that mark the region of the code that need to be optimized [44]. The programmer can control function inlining, loop fusion, loop unrolling e.tc. through the use of the pragmas.

Handle-C is another C-based high level programming language[4]. Even if there is no explicit clock information specified by programmers, the compilation system assumes that certain instructions in the algorithm are clocked. E.g. all assignment statements and if/while statement execute in a single clock cycle, and a value assigned to a register can only be available in the next clock cycle.

Figure 2.21: The hardware model of SA-C[86]

Haydn-C extends the idea of the handle-C by using two timing models[25]. The strict timing model of haydn-C is similar to the timing model of handle-C, and the flexible timing model is more advanced. Haydn-C compiler can break down the C description of an application into a dataflow graph (DFG). With the DFG and some user constraints, haydn-C compiler can reschedule the application in flexible timing model to find optimal implementations. Haydn-C also borrows the concept of entity and component from VHDL that make design more structured.

#### 2.4.2 Software optimization

Software kernels are the most important candidates for intensive optimization analysis, since they are most frequently mapped to the reconfigurable units. The optimization objective is to exploit the data-level parallelism (DLP), the instruction-level parallelism (ILP) and the loop-level parallelism (LLP) of the high-level application description, and to efficiently map the parallelized kernels onto the RU. The optimization is mostly based on four different types of analysis: loop analysis, data analysis, communication analysis and pipeline analysis. Here we introduce some of the most frequently used technologies in these categories and discuss how they are different from traditional issues when applied to the reconfigurable systems.

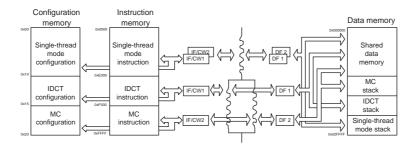

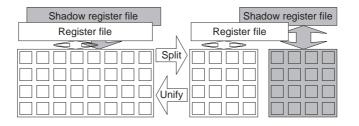

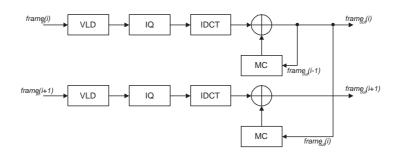

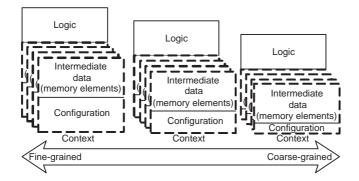

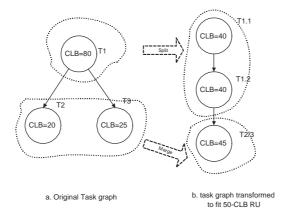

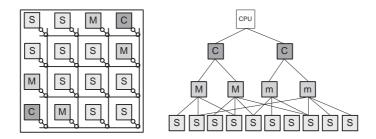

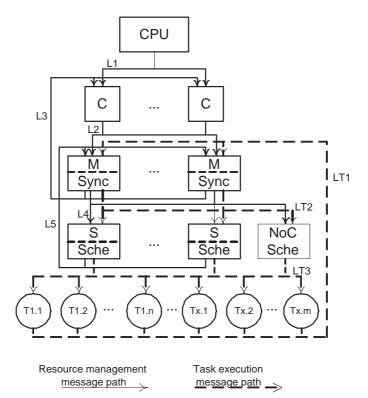

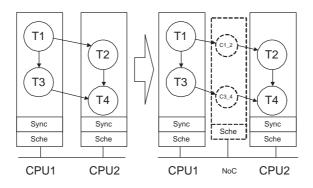

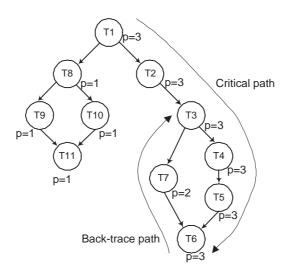

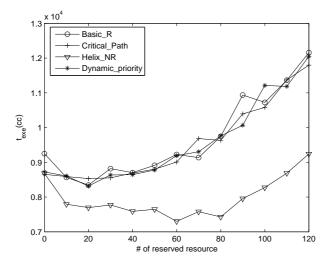

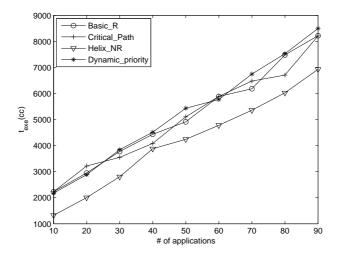

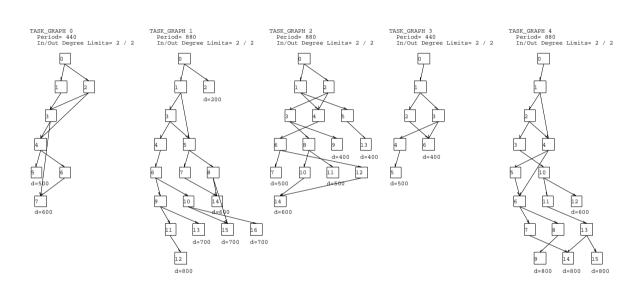

#### 2.4.2.1 Loop analysis