# Dependable boot and fail safe software for the DTUsat-2

Esben Rugbjerg

Kongens Lyngby 2007 IMM-MASTER-2007-39

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-MASTER: ISSN 0909-3192

# Contents

| In | trodu | uction                       | 3  |

|----|-------|------------------------------|----|

|    | Back  | ground                       | 3  |

|    | Stat  | us                           | 4  |

|    | Prob  | lem                          | 4  |

|    | App   | roach                        | 5  |

|    | The   | report                       | 6  |

| 1  | Dep   | endability                   | 9  |

|    | 1.1   | Dependability notions        | 9  |

|    | 1.2   | The $KIS(S)$ principle       | 13 |

|    | 1.3   | Redundancy                   | 13 |

|    | 1.4   | Graceful service degradation | 14 |

|    | 1.5   | Available tools              | 15 |

|    | 1.6   | Coding rules                 | 15 |

|   | 1.7 | Source code inspection tools            | 16 |

|---|-----|-----------------------------------------|----|

| 2 | Sys | tem description                         | 19 |

|   | 2.1 | The development board                   | 19 |

|   | 2.2 | The externally connected peripherals    | 23 |

|   | 2.3 | The memory layout                       | 25 |

| 3 | Rec | uirement analysis of the boot procedure | 29 |

|   | 3.1 | The choice of implementation languages  | 29 |

|   | 3.2 | Before launch                           | 31 |

|   | 3.3 | After launch                            | 31 |

|   | 3.4 | The system information block            | 36 |

|   | 3.5 | The fail safe mode                      | 39 |

| 4 | The | e memory test                           | 41 |

|   | 4.1 | Memory test - analysis                  | 41 |

|   | 4.2 | Memory test - design                    | 47 |

|   | 4.3 | Memory test - implementation            | 51 |

|   | 4.4 | Memory test - software test             | 52 |

| 5 | Sof | tware modules                           | 55 |

|   | 5.1 | The SIB - design                        | 55 |

|   | 5.2 | The SIB - implementation                | 62 |

|   | 5.3 | The SIB Parameter Structure             | 64 |

|    | 5.4   | FLASH driver - analysis                    | 64  |

|----|-------|--------------------------------------------|-----|

|    | 5.5   | FLASH driver - design                      | 68  |

|    | 5.6   | FLASH driver - Implementation              | 71  |

|    | 5.7   | Real Time Clock - analysis                 | 71  |

|    | 5.8   | RTC - design                               | 72  |

|    | 5.9   | RTC - implementation                       | 73  |

| 6  | Imp   | elementation details of the boot procedure | 75  |

|    | 6.1   | The first phase                            | 75  |

|    | 6.2   | The second phase                           | 83  |

| 7  | Con   | npilation and debugging                    | 87  |

|    | 7.1   | Building and compilation                   | 87  |

|    | 7.2   | The linker scripts                         | 89  |

|    | 7.3   | Debugging and Test                         | 90  |

| 8  | The   | timed models                               | 95  |

|    | 8.1   | Introduction                               | 95  |

|    | 8.2   | Communication between OBC and COMM         | 96  |

|    | 8.3   | Modelling the memory test of DTUsat-1      | 103 |

| Co | onclu | sion                                       | 109 |

|    | 8.4   | Main contributions                         | 110 |

|    | 8.5   | Future work                                | 110 |

|    | 8.6 Final conclusion                                        | 111 |

|----|-------------------------------------------------------------|-----|

| Bi | ibliography                                                 | 112 |

| In | dex                                                         | 112 |

| Aj | ppendices                                                   | 114 |

| A  | Schematic of the satellite                                  | 115 |

| в  | Solutions used in report generation                         | 117 |

|    | B.1 Source listing                                          | 117 |

| С  | Pseudo code of the memory test implemented in Assembly      | 121 |

| D  | Test cases and results from the <i>memory test function</i> | 125 |

|    | D.1 The structural test                                     | 125 |

| E  | DTUsat-1 related material                                   | 129 |

|    | E.1 Source code                                             | 129 |

| F  | Source files of the DTUsat-2 implementation                 | 137 |

|    | F.1 init.S                                                  | 137 |

|    | F.2 memTest.S                                               | 143 |

|    | F.3 cStack.S                                                | 149 |

|    | F.4 boot.h                                                  | 149 |

|    | F.5 boot.c                                                  | 150 |

iv

### CONTENTS

|   | F.6 sysInfo.h                                | 154 |

|---|----------------------------------------------|-----|

|   | F.7 sysInfo.c                                | 156 |

|   | F.8 intFlash.h                               | 161 |

|   | F.9 intFlash.c                               | 164 |

|   | F.10 rtc.h                                   | 173 |

|   | F.11 rtc.c                                   | 174 |

|   | F.12 intWDT.h                                | 176 |

|   | F.13 intWDT.c                                | 177 |

|   | F.14 crc.h                                   | 178 |

|   | F.15 crc.c                                   | 179 |

|   | F.16 cMemTest.h                              | 183 |

|   | F.17 cMemTest.c                              | 185 |

|   | F.18 testBench.S                             | 188 |

|   | F.19 test01.gdb                              | 189 |

| G | Test output                                  | 205 |

|   | G.1 Output from test of memory test function | 205 |

| н | The timed models                             | 207 |

|   | H.1 OBC vs. COMM                             | 207 |

|   | H.2 Memory test of DTUsat-1                  | 214 |

# Preface

This report describes the master's thesis project of cand.polyt Esben Rugbjerg. The project has been carried out between September 2006 and April 2007 on Technical University of Denmark at Institute of Informatics and Mathematical Modelling. I would like to thank my counsellor assistant professor Hans Henrik Løvengreen of Informatics and Mathematical Modelling at Technical University of Denmark. The project has been written as a part of the DTUsat-2 project. The DTUsat-2 project's primary goal is to teach students at DTU about the special issues which should be considered when designing a spacecraft. Besides it is also planned to set the built satellite in orbit to solve its scientific mission which is to track birds.

Lyngby d.

# Contents

# List of Figures

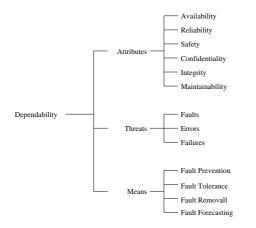

| 1.1 | The dependability tree. Copied from figure 2.1 of [ALR04]. $\ldots$                                                                                                                                                                      | 10 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | The memory layout of the RAM concerning the routines provided<br>by the boot loader. The areas written in yellow is not used during<br>execution of a program and thereby also available to the program<br>together with the user space. | 27 |

| 2.2 | The memory layout of the user space just after boot time                                                                                                                                                                                 | 28 |

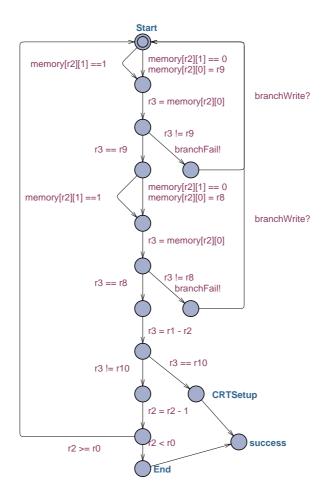

| 4.1 | The memory test algorithm used in DTUsat-1 as described in the assembler code in init.S.                                                                                                                                                 | 44 |

| 4.2 | Pseudo code of the 'Write' function                                                                                                                                                                                                      | 46 |

| 4.3 | The mechanism showing why the WDT cannot recover the system<br>from an infinite loop caused by a software fault or permanent fault<br>in the memory test function.                                                                       | 47 |

| 4.4 | First part of the memory test algorithm used during the init<br>phase. This is a short version meant for obtaining an overview<br>over its functionality.                                                                                | 49 |

| 4.5 | Second part of the memory test algorithm used during the init<br>phase. This is a short version meant for obtaining an overview<br>over its functionality.                                                                                  | 50  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Figure ill. the contents of the 512 bytes data assembled before being written to the FLASH.                                                                                                                                                 | 69  |

| 5.2 | Pseudo code of <b>prepDataArraySIB</b> ().                                                                                                                                                                                                  | 70  |

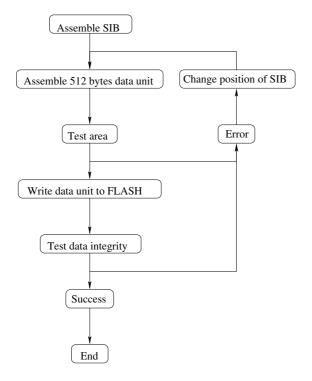

| 5.3 | Flowchart showing the procedure for writing a SIB to the FLASH memory.                                                                                                                                                                      | 70  |

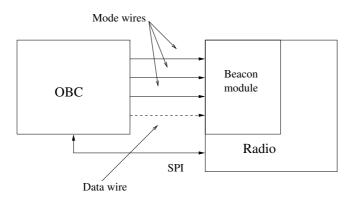

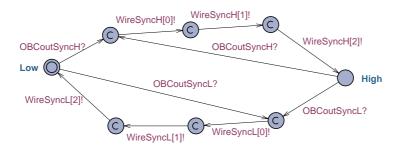

| 8.1 | Schematic illustration of the wire connection between the OBC and the beacon module of the COMM subsystem. All unnecessary details are discarded.                                                                                           | 98  |

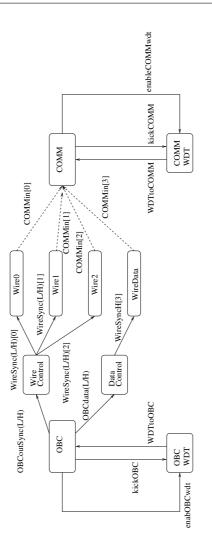

| 8.2 | Figure showing the interconnections between the processes in the OBC-COMM model. Solid lines represent channel connections and dashed lines represent connections through global variables. Only the important interconnections are showed. | 100 |

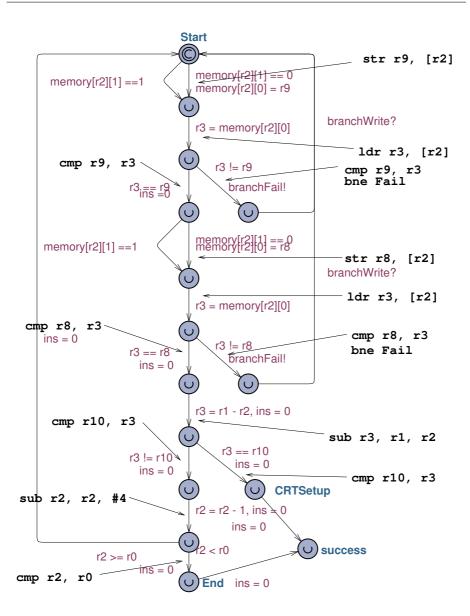

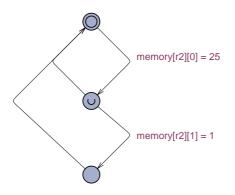

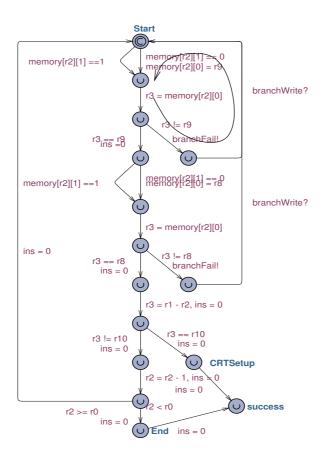

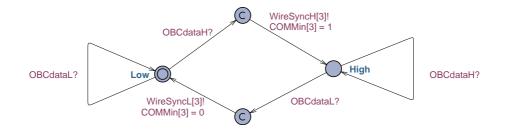

| 8.3 | Figure showing connection between edges and assembler instruc-<br>tions in model of memory test on DTUsat-1.                                                                                                                                | 104 |

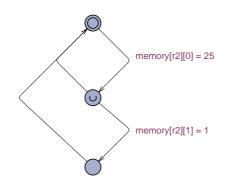

| 8.4 | The process handling fault injection in the memory test model                                                                                                                                                                               | 106 |

| 8.5 | Ill. showing the infinite loop in the 'Write'-process                                                                                                                                                                                       | 108 |

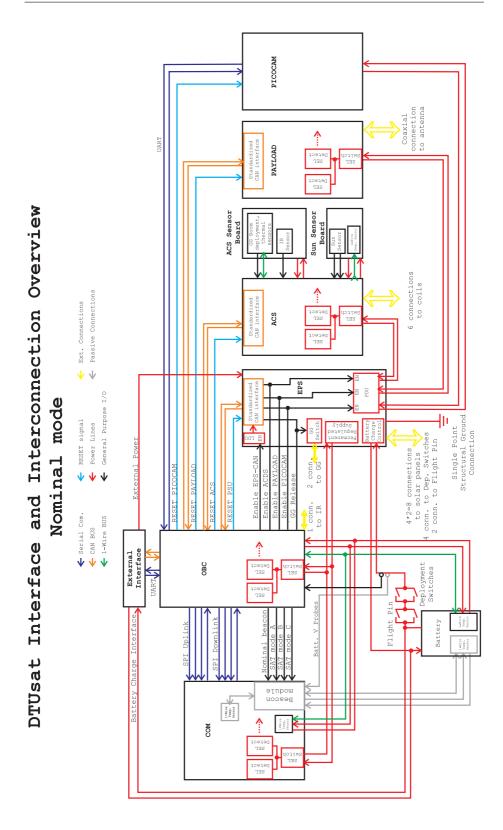

| A.1 |                                                                                                                                                                                                                                             | 116 |

| C.1 | To be continued in figure C.2.                                                                                                                                                                                                              | 121 |

| C.2 | First part of the memory test algorithm used during the init phase.                                                                                                                                                                         | 122 |

| C.3 | To be continued in figure C.4                                                                                                                                                                                                               | 123 |

| C.4 | Second part of the memory test algorithm used during the init phase.                                                                                                                                                                        | 124 |

### LIST OF FIGURES

| H.1 | The OBC process              | • | • | • | <br>• | • | • | • | • | • | • | • | • | • |   | • | • | • | 210 |

|-----|------------------------------|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| H.2 | The COMM process             |   | • |   |       |   |   |   | • |   |   | • |   |   |   | • | • |   | 211 |

| H.3 | The WDTs                     |   | • | • |       | • | • |   | • |   | • | • |   | • |   | • | • | • | 211 |

| H.4 | The wire processes           |   | • |   |       | • | • |   | • |   | • | • |   | • |   | • |   | • | 212 |

| H.5 | The wire control process     |   | • |   |       | • | • |   | • |   | • | • |   | • |   | • |   | • | 212 |

| H.6 | The data control process     |   | • |   |       | • | • |   | • |   | • | • |   | • |   | • |   | • | 213 |

| H.7 | The 'write'-function process |   | • | • |       | • |   |   | • |   |   | • |   |   |   | • | • |   | 215 |

| H.8 | The failure control process. |   | • | • |       | • | • |   | • |   | • | • |   | • | • | • | • |   | 215 |

| H.9 | The fault injection process. |   |   |   |       |   |   |   |   |   |   |   |   |   |   |   |   |   | 216 |

\_\_\_\_\_

# Introduction

# Background

In the summer 2003 the DTUsat-1 was launched using a reused russian ballistic missile. The DTUsat-1 was a CUBESAT satellite which means that it adhere to the CUBESAT[HT05] design concept. This concept dictates that the design of the satellite shall conform to a simple set of rules where the most important is that the satellite must be a cube with a side length 10 centimeter.

The concept behind the CUBESAT project is to design small satellites with a low weight resulting in keeping the launch expenses low. Another major asset of the design is that the launch system is standardised making it simpler to incorporate the satellites as secondary payload on commercial rockets.

No signals were received from this satellite which means that it for some reason never got into function. The cause of the failure of the DTUsat-1 has never been determined since no information about the state of the satellite could be collected. The satellite is a complex system where a specific combination of several events needs to occur in the correct order if just a single 'beep' shall be sent from it. Because several different subsystems need to work in cooperation to startup the satellite the fault causing the error can be found in any of these<sup>1</sup>. This complicates the error detection and has made it impossible to determine why the satellite never started working.

In the middle of 2005 a new satellite project (the DTUsat-2) was proposed at

<sup>&</sup>lt;sup>1</sup>No chain is stronger than its weakest link.

DTU. In this project a new CUBESAT should be built. In spite of the failure of the first satellite it was decided that the DTUsat-2 should contain a scientific mission as its payload. A payload contest was arranged to get proposals for the payload. The winning project was announced ind November 2005. It suggested that birds (cuckoos) should be tracked on their migratory route by placing GPS transmitters on the back of them and collect the information about their positions using the satellite. Besides that the satellite should also contain a simple camera such that pictures of the earth can be transmitted back from the satellite.

### Status

The subsystems of the DTUsat-2 are built as student projects, because the major goal of the satellite project is to educate engineer students in system engineering and aspects of spacecraft design. Both hardware and software are designed and implemented by students. Until now some of the subsystems (the electrical power system (EPS) and the on board computer (OBC)) have been designed and implemented but the radio systems are not yet designed. A lot of the software for the satellite is designed and some is implemented. Parts of the software of the DTUsat-1 has been reused. Some of the software projects are delayed because the complete hardware design is not known yet.

# Problem

The most mission critical group of applications developed in the engineering world is that of spacecrafts. These highly developed technical applications contain state of the art solutions in all their aspects. All components of the system are chosen especially for their purpose and most of them are also developed with this specific purpose in mind. This is also the case concerning the software programs running on the computers in, for example a satellite.

When a system is given the predicate *mission critical* it means that if any subsystem fails during operation it is very likely that the mission of the whole system fails. This property results from the fact that it is very difficult to recover the system from the fault e.g. because it is almost impossible to get in physical contact with the system again. This is e.g. the case with satellites. It can also result from a time-wise property for example that some astronomic event only can be observed very rarely.

The software of the DTUsat-1 was divided into the following parts: A nominal mode which was recognised by the fact that the operating system (OS) had been booted successfully, and the fail safe mode (FS) in which the FS software was executed. Execution of the boot software is a part of the FS. This structure of the software has been adopted by the DTUsat-2 project. The nominal mode is quite complex system whereas the boot and FS software is kept as simple and minimalistic as possible.

For this reason the boot and FS software of a satellite is considered mission critical. The task of the program is to startup the satellite and ensure that all subsystems function correctly before the OS of the satellite is started. If for some reason the OS cannot be started for example due to some subsystem not working as expected or the OS itself fails, the FS program should be started to handle this situation. Therefore the boot and FS software is the most mission critical software on the satellite: If the boot software does not function correctly the satellite will never start, and if the FS software does not function correctly the satellite cannot be recovered from any failures caused by some of the other software on the satellite or one of the hardware subsystems. In both situations the satellite and thereby its mission will fail.

The main task in this project is to design and implement the boot and FS software for the DTUsat-2. The program should be as complete as possible meaning that as much of the functionality of the program as possible should be designed and implemented. The goal is a highly dependable, operational program which can be used on the DTUsat-2 when it is completed with as few modifications as possible.

# Approach

The boot and FS software needs to be very robust and dependable and it should be developed to an operational level in this project. These three properties have been decisive for the choice of approach in the project.

In order to achieve the robustness and dependability of the program best practice methods of software development have been applied during the project. The choice of the used software tools and tool chain also reflects this. As explained later in chapter 7 the GCC tool chain has been chosen among other reasons because it is open source software which enables us to inspect the source code if some problems demands it. Another and even more important reason is that the GCC tool chain is considered very reliable due to its long development history. The project has been carried out as a classic software project with an analysis phase, a design phase and an implementation phase, since this is an approved procedure and since I am familiar with this method.

Through the analysis and design phases of this project an operational approach has been chosen. This approach has been based on classical "pen and paper"pseudo-coding. This working method is in contrast to the more academic method where a formal model of the whole satellite and the program running on it would have been developed. The temporal properties of this model would have been verified using a model checker. The verified model could then constitute the outline for the implementation of the program in the C programming language. The time frame of the project did not allow such a model to be developed. Another reason why this approach was abandoned was that the modelling approach is not believed to lead to the desired product i.e. an operational program. These two reasons entailed that a more operational approach was chosen. It was tried to combine the described approach with the usage of available software tools whenever they were found to simplify specific tasks in the project or raise the robustness or dependability of the final product. It was however not found feasible to use any software tools to handle any larger issues during the software development process. Neither suitable problems nor tools were found.

The software of the DTUsat-1 has been used as inspiration and the FS part has been modified and merged into the DTUsat-2 software. This has been done partly because this part of the program was well designed and tested and due to lack of time in the present project to write the everything from scratch.

### The report

The report describes the development of the boot and FS software of the DTUsat-2. The first chapter contains short introduction to dependability in software which is a main property of mission and safety critical software. The second chapter contains a description of the OBC and the test board used during development of the software. The third chapter contains an analysis of the boot situation of the satellite and outline the requirements of the boot and FS software. The fourth chapter describes the development of the memory test used during the boot procedure. The fifth chapter describes the development of other parts of the boot and FS software. The sixth chapter contains a description of methods used while testing and building the software. The seventh chapter describes the attempts to verify the soundness of the protocol used to communicate between the on board computer (OBC) and the radio (COMM) subsystem of the satellite using the model checker Uppaal. Finally a conclusion

describing the obtained result and the properties of the developed software are given in chapter eight. After that some appendices are given containing the source code of the program as well as test output etc.

In this report a lot of references to background information which is not necessarily interesting when reading the report as the documentation of a master's project are given.

The reason for this is that the report is written with more than this purpose in mind. Besides being the documentation of a master's thesis it is also intended to be the primary source of information about the boot system and its internals for the students who shall complete the system when the hardware platform of the DTUsat-2 will be finished. Emphasis has therefore been put into collecting all relevant references. In addition to this an index and a glossary are also available. In the index the names of the C functions are listed together with links to the source code and their prototype. The beginning positions of the C functions are also listed in the table of contents. The glossary contains explanations of the abbreviations used during the report together with definitions of some central terms in the project.

# Chapter 1

# Dependability

Dependability is a central subject in computer technology especially concerning embedded systems. The reason for this is that most applications of embedded systems possess some kind of safety or mission critical properties.

This chapter is divided into two main sections. The first section contains a brief description of the basic of dependability notions and the second section introduces some methods which can be used to raise the dependability of a system. A more thorough survey than the one given in this chapter is presented in [GL02].

# 1.1 Dependability notions

Dependability of computer systems has been a research subject since the beginning of the development of electronic computers. The reason is that computer scientists always have tried to raise the dependability of the systems such that the results computed by the computer could be trusted and such that the computers could be trusted to work at all. Later when computers were used to control systems where failures could be lethal to humans this research subject became even more important.

### 1.1.1 The framework of Dependability theory

A good starting point for getting an overview over the notions used in dependability theory is the *dependability tree* which is a simple tree structure showing the relations between the central notions in dependability. It is shown in figure 1.1 which is copied from figure 2.1 of [ALR04].

Figure 1.1: The dependability tree. Copied from figure 2.1 of [ALR04].

Figure 1.1 shows that the three central areas of dependability theory are:

**Dependability attributes** Dependability attributes are the quantities which a system's dependability is measured in. The attributes are not necessarily given a specific value but the quantities constitute a framework which a system's dependability can be assessed in.

Dependability threats The threats are faults, errors and failures.

**Dependability means** The means are the tools available to raise the dependability of a system.

#### 1.1.2 The Attributes

The dependability attributes are a set of attributes which can be described for a specific system. It does not always make sense to try to determine the value of all attributes for a specific system. For example it is not meaningful to determine

the safety <sup>1</sup> of the DTUsat-2 because it will be very far away and no people will ever get in physical contact or even close to it while it is in service.

A central attribute to the DTUsat-2 project is the *availability* which is defined as:

readiness for correct service

in [ALR04, section 2.3]. The most important attribute is the *reliability*. The reliability is defined as the system's exhibits of:

continuity of correct service

in [ALR04, section 2.3]. The availability of the DTUsat-2 is raised by ensure the robustness of the EPS and including a battery in the system's design of the satellite etc.

The attributes *confidentiality* and *Integrity* are together with *Availability* closely connected to the IT security area. *confidentiality* is defined as:

absence of unauthorized disclosure of information

and *integrity* as the:

absence of improper system alterations

Both quoted from [ALR04, section 2.3].

Maintainability is defined in [ALR04, section 2.3] as the:

ability to undergo modifications and repairs

Even though it is impossible to get in physical contact with the satellite when it has been launched this attribute is interesting even in the case of a satellite.

$<sup>^1\</sup>mathrm{defined}$  as "absence of catastrophic consequences on the user (s) and the environment" in [ALR04, section 2.3].

On the DTUsat-2 as little of the software as possible is stored in a ROM, and as much as possible in a FLASH memory. The software stored in the ROM is made capable of writing to the FLASH memory making it possible to erase the entire OS and application software of the satellite and upload a new version. In this sense the satellite has the highest possible maintainability.

#### 1.1.3 The notions of faults, errors and failures

In normal conversations the three terms fault, error and failure is almost interchangeable or at least the two first are. This is not the case in dependability theory where each term has a specific meaning.

In dependability theory a *failure* is the consequences to the surrounding or system caused by some wrong internal state of the system. The wrong internal state is called the *error*. The cause of the error is called a *fault*. This distinction will be illustrated in a small case study.

#### 1.1.3.1 The Mars Climate Orbiter incident

September 23th 1999 Nasa's Mars Climate Orbiter was navigated into orbit around Mars. Unfortunately it was lost during this maneuver. The following investigation showed that the reason for the loss was that the altitude of the satellite was to low. It should have entered an orbit with an altitude of 150 kilometers above the surface of the planet but the actually altitude was only about 60 kilometers which had catastrophic consequences for the satellite [MCO99].

In the following investigation it was revealed that the cause of the low altitude was a fault where one team of engineers used imperial units and another team used the metric system [IHU99].

In this example the **fault** is the usage of the imperial units instead of the metric system. The **error** is the low altitude of the spacecraft and the **failure** the spacecraft's crash into the surface of Mars.

#### 1.1.4 The means available in dependability

As it has been implied indirectly there are different techniques to improve dependability of a system. All these techniques can be classified into one of the following groups (copied from [ALR04, section 2.4]:

fault prevention are means to prevent the occurrence or introduction of faults.

fault tolerance are means to avoid service failures in the presence of faults.

fault removal are means to reduce the number and severity of faults.

fault forecasting are means to estimate the present number, the future incidence, and the likely consequences of faults.

In the boot and FS software on the DTUsat-2 two major **fault tolerance** methods have been implemented. The first is the memory test (described in chapter 4) which tries to prevent the usage of defective memory locations. The second is the use of a WDT which can recover the system if it gets trapped in an infinite loop. In the rest of this chapter some fault prevention and fault tolerance methods will be presented.

# 1.2 The KIS(S) principle

The kis(s) (Keep It Simple (stupid!)) principle is not a real design paradigm but a guiding rule used when choosing between different design options. The principle require the designer to choose the simplest solution which solves the problem, avoiding adding unnecessary features and complexity. The principle can also be applied to writing style of the source code where the programmer is demanded to keep the code as simple and self explained as possible. The principle is also connected to Occam's razor [kis06].

The main design principle which should adhered in all design processes concerning parts of the DTUsat-2 project is the kis(s) principle. This principle should be adhered even when other design paradigms are applied.

# 1.3 Redundancy

Redundancy can be applied to both software and hardware. It can be applied in both a parallel (computational) and a serial (temporal) manner.

The parallel redundancy is normally applied as hardware redundancy where several computers compute the answer to the same problem using different methods or algorithms. When all computers have computed an answer the answers are compared and the answer which occur most often is used. The method is based on the assumption that if an answer occur several times even if it is computed using different methods it must be correct. The method can also be described as a voting process where the computers vote on the solutions to a problem.

The temporal redundancy is normally applied as software redundancy. Empty slots of time are added to the schedule making it possible to rerun processes which fail. Another solution is computing the solution to the problem again using a simpler algorithm.

The size of the DTUsat-2 and the available resources of energy and therefore computing resources does not allow any kind of hardware redundancy to be implemented in the satellite.

In general both software and hardware redundancy adds a lot of complexity to a system if applied. This argument constitute another major reason for avoiding software redundancy on DTUsat-2, since the kis(s) principle should always be adhered. This does not mean that software redundancy in general cannot be applied to a system in combination with the kis(s) principle but that it has not been found feasible in this particularly project.

# 1.4 Graceful service degradation

Graceful service degradation means to adapt the quality of a service based on the available computing resources and available functional subsystems. Graceful service degradation is closely related to *reconfiguration*. Reconfiguration means to restore a stalled system to some operational state, avoiding use of subsystems which contain permanent faults. Reconfiguration is primarily applied on the hardware level.

Graceful service degradation on software level may be based on using simpler or slower algorithms to compute the solution. In this case a trade off between quality of the produced solution and ability to deliver a solution at all is made.

On the DTUsat-2 graceful service degradation is used as a design principle by adding a fail safe mode in addition to the nominal mode.

# 1.5 Available tools

Several software tools have been developed to help developing more dependable software. In this section a short summary of some of the available tools will be given. The tools have been chosen for their relevance to the DTUsat-2 boot and FS software.

None of the tools have actually been used during the development of the boot and FS software development due to lack of time.

### 1.5.1 Stack size calculation tools

Stack usage tools analyse the binary code to estimate the worst case stack size. This is relevant when planing memory usage of the system. The stack usage analysis is a static test meaning that the worst case stack usage is computed for the specific binary file not inferring any kind of equation for the stack usage.

The reason for doing the analysis on the binary is that the compiler optimisation can influence the stack size, hence it is not meaningful to do the calculations on the source code.

The stack size analysis makes it possible to prevent stack overflows and is hence a good fault prevention method. An example of a stack analysing tool is the commercial tool StackAnalyzer (see [stA07]).

Another solution is to do the calculation manually by constructing a test case which gives rise to the largest possible stack usage, and then inspect the memory by a debugging tool when the test program has been run. This method is outlined in [ARM] together with other similar methods. This solution does not lead to a verifiable calculation of stack size but only to an estimation.

# 1.6 Coding rules

Coding rules are conventions and rules for how the source code should be written. They include rules about which language constructs are allowed, how variables and functions are named etc. Coding rules have two purposes: Prevent the usage of "dangerous" constructions in the source code and raise the uniformity between code written by different developers. An example of a classic coding rule is that **while()** loops are not allowed, because they contain the ability to go into infinite loops. All loops should be bound to finite upper level of iterations.

Especially in the case of development of mission or safety critical software compliance of coding rules are required. An example of this is the "C and C++ Coding Standards" of the European Space Agency [esa00]. This report contains 113 rules and recommendations on how to write understandable, portable and safe C and C++ code. The rules and recommendations are based on experiences more than theoretical or strictly analytical work. A more thorough survey on design and coding constraints is given in [PP02].

### **1.7** Source code inspection tools

A group of fail prevention tools do an automated code inspection of the source code. Several different programs exist. In this section short descriptions of two of the tools are given. The tools have been chosen for the following reasons: Security Programming Lint (Splint) implements a lot of tests also implemented in an older and popular tool called "Lint", and it is optionally annotation driven.

The Berkeley Lazy Abstraction Software Verification Tool (BLAST) is a annotation driven model checker for C source code.

### 1.7.1 Splint

Splint ([spl]) is a source inspection tool. It reads the source files and searches for unused declarations, type inconsistencies, use before definition etc. [Sec, p. 9]. The coding mistakes searched for by Splint is often the same as the coding rules mentioned in section 1.6 try to avoid.

Splint is capable of finding a lot different coding mistakes. Unfortunately it produces a lot of false positives. The most of these false positives can be removed if annotations are added to the source code. These annotations helps Splint to determine which of the potentially faults are actually faults and which are code constructions intended by the programmer.

An example is the /\*@null@\*/ which tells Splint that the pointer declared on the next line is intended to contain null pointer in some cases. As it can be seen the annotations are added to the source code as comments. Therefore the program can be compiled directly.

/\*@null@\*/

int \* counter;

### 1.7.2 BLAST

The Berkeley Lazy Abstraction Software Verification Tool (BLAST) (see [BLA05] is a model checker for C source code. The model-checker can verify that invariants are not violated during execution of the code. The code is executed in a symbolic fashion by the model checker.

BLAST also contains a scripting language which makes it possible to carry out more advanced tests where more than one invariant needs to be tested at the same time. Using the scripting language also avoids applying changes to the source code.

BLAST contains some advanced features which will not be discussed here.

# Chapter 2

# System description

The brain of the satellite is the OBC. Physically the OBC is a circuit board. This board is equipped with the central CPU chip (described in 2.1.1), the external memory chips (SRAM and FLASH, described in 2.1.1.3), an external watch dog timer  $(WDT)^1$  and some components controlling the energy supplies.

The energy for the subsystems of the satellite is supplied by the electric power system (EPS), which therefore must be considered the heart of the satellite. This board is connected to the solar panels, the batteries, the sun sensor board, the Altitude Control System sensor board (ACS sensor board), the ACS board<sup>2</sup> and all other subsystems. This board contains all central electrical systems and power connections.

### 2.1 The development board

This section contains a description of the hardware system used during the software development. The system is an Olimex LPC-E2294 development prototype board [oli06] equipped with a Philips LPC2294 ARM CPU chip and several pe-

<sup>&</sup>lt;sup>1</sup>no information is available on this device yet.

$<sup>^2\</sup>mathrm{The}$  "ACS sensor board" and the "ACS board" are two different boards.

ripherals for example a 16x2 character LCD display. Where no other thing is mentioned the information given in this chapter also complies to the OBC of the DTUsat-2. No information will be given about the interface between the programming PC and the development board.

#### 2.1.1 The CPU chip

The CPU chip on the development board which has been used during the development of the software is a Philips LPC2294. Besides the processor it contains all necessary devices to build a simple embedded system. In this section a description of the relevant subsystems on the chip is presented. The CPU chip on the DTUsat-2 is a Philips LPC2292. The only difference between the two chips is that the LPC2294 contains four CAN bus controllers whereas the LPC2292 only contains 2 CAN bus controllers.

#### 2.1.1.1 The processor core

The processor core implements the ARM7TDMI architecture which is a true 32-bits architecture with both 32-bits instruction set and memory space. It is a RISC architecture which does not contain any floating point (FP) instructions. The CPU contains 13 general purpose registers. The ARM7TDMI is a pipelined architecture having three stages (fetch, decode and execute).

Besides the 32-bits instruction set the processor is also capable of executing the 16-bits *thumb* instruction set. This instruction set was developed to offer more compact binary code than the 32-bit code offers.

#### 2.1.1.2 The clock system

The crystal which supplies clock pulses to the CPU chip runs at 14.7456 MHz. This clock is passed to the phase locked loop (PLL) circuit, which is used to increase the clock frequency of the CPU core. This frequency is referenced as the *cclk* in the documentation which gives a more thorough description of the use and configuration of the PLL in [Phi03, page 75]. An example of how to calculate the constants needed to setup the PLL is also given in [Lyn05, section 15]. Besides the *cclk* the chip has a peripheral clock net. This clock is referenced to as the *pclk*. The frequency of this clock is controlled by the *VLSI peripheral*

bus  $(VPB)^3$  clock divider (VPB divider). How to configure the VPB divider is described in page 86 of [Phi03]. the *pclk* is for example used by the WDT. The frequency of the *pclk* also depends on the configuration of the PLL since it is generated by dividing the *cclk*.

#### 2.1.1.3 The memory system

The LPC2294 contains both internal FLASH memory and internal static RAM. Besides that, it is possible to connect external memory devices. On page 48 and 49 in [Phi03] two complete memory maps of the memory in the LPC2294 chip are given. The memory system contains no cache stages, but the bus system includes a memory accelerator module (MAM) which enables execution of sequential code at the speed of the internal clock (*cclck*). This module is described further in section 2.1.1.3. A more complete describtion of the memory layout of the system is given in section 2.3.

**The RAM** The internal static RAM is 16 KB in size. It starts at address 0x40000000 and ends at 0x40003FFF.

**The FLASH memory** The internal FLASH of the LPC2294 chip has a storage capacity of 256 KB. It is mapped into the address space from address 0 to address 0x003FFFF. The top 8 KB of the FLASH is reserved for the boot loader program and should not be erased or used for anything else. At the lowest 64 bytes of the FLASH (starting at address 0x00000000) the interrupt vectors should be placed. At address 0x00000000 the reset interrupt vector should be placed and it should contain a jump function to the entry point of the boot program.

The memory accelerator module The memory accelerator module (MAM) speeds up reading of the FLASH memory by prefetching 128 bit in each read operation and latch them for faster answering on instruction fetch requests from the CPU. The FLASH memory is divided into two banks each having a 128-bit latch. This enables a switch behavior where one bank is reading 128 bit of instruction data while the other bank is prefetching the next 128-bit. The MAM is described in [Phi03, page 90 - 93].

<sup>&</sup>lt;sup>3</sup>Described in [Phi03] on page 18

#### 2.1.1.4 The internal watch dog timer

The internal watch dog timer (WDT) is used as the primary WDT during software development. The WDT can be setup to have a timeout period between  $69.4 \mu$  seconds and 1165.08 seconds (= 19.41 minutes) if the pclk runs at 14.7456 Mhz.

The WDT contains a mode and status register referenced as **WDMOD** in the documentation. The value of this register is maintained during a reset if the power of the chip is not disconnected or interrupted. From this register it is possible to determine whether the WDT induced the reset or not.

The WDT is described more thoroughly in [Phi03, pp. 256].

#### 2.1.1.5 The real time clock

The real time clock (RTC) is a clock system using normal time units like hours, minutes, month and year. It is possible to read the time from the clock's counter registers. The RTC can also be setup as an alarm by providing interrupt generation based on value matching between its counters and a set of register which contain the desired time for the alarm.

The value of the counters is not maintained during power off. If the WDT reset the system only a delay as long as it takes the system to startup and initialise the RTC will occur.

The RTC is described more thoroughly in [Phi03, pp. 242].

#### 2.1.1.6 The boot loader

Every time the CPU chip is turned on or reset a boot loader program laying in the internal FLASH memory is executed. This program executes before any user program is executed.

If the 'BSL' jumper is set the boot loader calls its "In-System Programming" (ISP) functions. These functions is used to program the internal FLASH i.e. uploading a new user program. This is done through a UART of the chip.

The boot loader program also contains functions which are used to program the internal FLASH through a program running on the CPU. In this way unused

memory of the internal FLASH can be utilised by the user program. The mentioned functions are called "In-Application Programming" (IAP) functions and are described in [Phi03, pp. 262].

An example of the usage of the IAP functions is presented in 5.5. Through out the rest of the report the boot loader program is referenced as the "boot loader" or the "internal boot loader". The program developed in the project is referenced to as the "boot program".

## 2.2 The externally connected peripherals

Several external peripherals are connected to the CPU. All subsystems of the satellite can be considered peripherals if the OBC controls them. As all subsystems have not yet been designed an exhaustive description of all peripherals and subsystems is not provided here. Only peripherals and subsystems which are designed, implemented and relevant for the boot or FS software are described.

#### 2.2.1 External memory

The external memory is accessed through the external memory controller (EMC). It provides the possibility to have four banks of 16 MB each. Bank number 0 begins at address 0x80000000. The interface of the EMC is described in details in [Phi03, pp. 56].

It is possible to change the boot behavior of the chip such that the boot loader boots the boot program from address 0 of the first external memory bank. This would be address 0x80000000. See [Phi03, p. 133] for details.

The ability to change the boot address of the system will be exploited on the satellite to boot the boot software stored in a ROM. This ROM is connected as memory bank zero of the EMC, starting at address 0x80000000. The interrupt vectors are placed from the beginning of this and 64 bytes up and starts with the RESET interrupt vector at address 0x80000000.

**External RAM** On the development board 1 MB of external S-RAM is mounted. This is 10 ns devices of the type: "K6R4016V1D" [sam04] and it is manufactured by Samsung.

The external RAM on the OBC is static RAM as the internal RAM is. It is connected as the external memory bank one through the EMC. The size of the RAM is two MB and it starts at address 0x81000000 and ends at address 0x8101FFFFF. Details on the configuration of the communication between the EMC and the external RAM are found in [Phi03, pp. 56].

The external RAM is primarily used by the OS but is also used as stack area for the boot and FS software if the whole internal RAM area is corrupted.

**External FLASH memory** The development board is equipped with 4 MB of external FLASH memory. This memory is connected to the bank zero of the EMC. The external FLASH is of the type "Intel Advanced+ Boot Block Flash Memory 28F160C3" as described in [Int05].

The external FLASH memory of the OBC has a storage capacity of 2 MB and is manufactured by Intel. The type of the FLASH is "Intel Advanced+ Boot Block Flash Memory 28F160C3" and it is described in [Int05]. The purpose of the external FLASH is to store data collected by the OBDH. It will be connected as bank one of two of the EMC.

#### 2.2.2 The GPIO interface

The GPIO interface is a port based interface. It is only used for the hold signal send to the COMMpic because as much as possible of the communication between the OBC and the other subsystems should be transmitted over standard bus systems. This is a design goal of the DTUsat-2. The GPIO interface is described in [Phi03, page 134 - 137].

#### 2.2.3 The CAN bus and SPI interface

The CAN bus is used to communicate with the other subsystems on the satellite. Two different CAN bus controllers resulting in two individual channels are available on the LPC2292 chip, where four are available on the LPC2294 chip. The controllers of the CPU chip are described in [Phi03, page 188 - 210].

The SPI interface is also a hardware interface. It is used to connect the COMM system to the OBC.

# 2.3 The memory layout

During execution of the boot program and other programs which use the IAP routines to write data to the internal FLASH memory of the CPU chip, areas of the RAM is used by these routines. This should be taken into account in the design of the memory layout. Also the usage of areas by the stacks of the exception routines should be considered when prioritising the allocation of the RAM.

#### 2.3.1 Memory area used by the boot loader of the chip

The memory layout concerning the ISP and IAP routines can be seen in figure 2.1.

The boot loader of the chip uses some of the internal RAM when some of its code is executed. The ISP routines are used to write to the FLASH memory when uploading a program to the system. Therefore these routines are only used when no program is executed on the processor. The IAP routines are used to do operations on the FLASH through a user program. Besides the memory especially reserved to the IAP routines it also use some memory on the normal program stack. This amounts to be at most 128 bytes [Phi03, page 265].

Besides the FLASH writing routines the boot loader also provides a debug interface called *RealMonitor* which is especially suited for real time debugging. This is not used during development in this case due to lack of Linux based debugging applications which supports the RealMonitor protocol. The memory use of the system is shown in figure 2.1 for completeness only.

#### 2.3.2 The memory areas used by exception routines

Several exception types exist in the ARM architecture. A very important type is the interrupt. In this section the terms exception vectors and interrupt vectors are interchangeably.

When handling exceptions the ARM processor changes into other modes only used for this purpose. These modes have their own set of special purpose registers for example the stack pointer (SP) register. This design is chosen to speed up handling of interrupts and exceptions by avoiding time consuming context shifts. To support this design, special areas are reserved for the stacks used by these routines. The area containing these stacks has been placed at the top of the RAM area.

The area in the bottom of the internal RAM is used to store the remapped exception vectors, see [Phi03, page 52]. There is two reasons for this solution: speed, since the RAM responds faster than the FLASH memory, and security: If one of the IAP routines are called by a user program, the internal FLASH enters a busy mode making it impossible to read from it. Therefore if an interrupt occurs while the IAP routine is executed, it will not be possible for the system to read the exception vectors from the FLASH memory. Instead it is possible to read them from the RAM if they are also stored there.

The size of the area used by the exception vectors is 64 bytes. Since the interrupts are disabled during boot this area is not used. When booting the system, the boot loader of the chip sets up the MEMMAP register which controls the remapping, see [Phi03, page 74], such that no remapping is activated.

The area in the top is the actual stack areas used by the interrupt serving routines. If the interrupts are disabled they can be reduced to 4 bytes each. It is necessary to have unique stacks for the *undefined instruction mode*, the *abort mode*, the *fast interrupt* (FIQ) mode, the *interrupt* (IRQ) mode, and the *supervisor mode*. The user mode and the system mode share their stack. The user and system stack is a real stack laying below the other pseudo stacks and grows downwards. As it can be seen five pseudo stacks are needed, taking up four bytes each, using twenty bytes all included. This is described in more details in [Lyn05, section 14]. These twenty bytes are taken from the area available for boot and FS program, The memory layout of the user space can be seen in figure 2.2.

| 8 kB        | Boot block remapped from FLASH            | 0x7FFFFFFF<br>0x7FFFE000                                                 |   |

|-------------|-------------------------------------------|--------------------------------------------------------------------------|---|

|             | Top of SRAM                               | 0x40004000                                                               |   |

| 32 bytes    | Used by the ISP and IAP<br>FLASH routines | 0x40003FFF<br>0x40003FE0                                                 |   |

|             | Stack area used by the ISP FLASH routines | 0x40003FDF<br>0x40003EE0                                                 |   |

| 15584 bytes | USER SPACE                                | 0x40003EDF<br>Avaiable sta<br>for boot and<br>software: 16<br>0x40000200 |   |

| 224 bytes   | Space used by the ISP<br>FLASH routines   | 0x400001FF<br>0x40000120<br>0x4000011F                                   |   |

|             | Space used by RealMonitor                 | 0x4000000                                                                | 1 |

Figure 2.1: The memory layout of the RAM concerning the routines provided by the boot loader. The areas written in yellow is not used during execution of a program and thereby also available to the program together with the user space.

|            |                          | 0x40003FE0 |

|------------|--------------------------|------------|

|            |                          | 0x40003FDF |

| 20 bytes   | Interrupt serving stacks |            |

|            |                          | 0x40003FCC |

|            |                          | 0x40003FCB |

|            |                          |            |

|            |                          |            |

|            |                          |            |

| 1(2221 )   | A 1111                   |            |

| 16332bytes | Available user space     |            |

|            |                          |            |

|            |                          |            |

|            |                          |            |

|            |                          |            |

|            |                          | 0x40000000 |

Figure 2.2: The memory layout of the user space just after boot time.

# Chapter 3

# Requirement analysis of the boot procedure

This chapter contains a requirements analysis of the boot process of the DTUsat-2 regarding requirements of the boot software which carry out and control the boot procedure.

The following description of the launch lacks some data since some informations about the launch and subsystems is not available yet.

# 3.1 The choice of implementation languages

The choice of implementation language is a central design decision. In this project dependability, robustness and simplicity are central demands to the implemented program. Therefore the implementation language should support these three properties. To ensure these three properties the programmer should have as much control over the program as possible. This is accomplished by using a simple programming language where only the most simple things are taken care of by the compiler.

Another central characteristic of the candidate language is that it should run

directly on the CPU since no OS is available yet, why facilities such as memory management not yet is available.

#### 3.1.1 The assembly language

These demands point in the direction of the assembly language. This language demands the programmer of controlling almost everything and give him the most freedom to control the computer. Another very important property is that it runs directly on the CPU.

Unfortunately the assembly language also makes things very complicated as a consequence of the vast quantity of things the programmer needs to control. Therefore only small programs where the special facilities which the language offers to the programmer's disposal are needed, should be programmed in the assembly language.

#### 3.1.2 High level languages

Several high level languages and there derived dialects are available as candidates: C and Pascal etc. C is known to be very robust and it gives a lot of freedom to the programmer. Both languages are supported by open source software and free compilers. Both languages can be compiled to run directly on the CPU without needing any facilities supplied by an OS.

The C language is familiar to the programmer which Pascal is not. This measure is the deciding one since one additional way to make a program dependable is by letting the programmers work in a well known environment.

Both C and Pascal are stack based programming languages meaning that they both need a memory area to store variable values during execution. Therefore they both need that a memory area is prepared for this purpose before a program is called.

#### 3.1.3 Conclusion

The assembly language can run directly on a CPU without needing any stack area but programs written in assembly language normally get very complex when they grow large. High level languages on the other hand keep programming issues fairly simple even in large programs. Unfortunately they need an initialised system in order to execute.

This leads to a situation where a combination of a low level language as the assembly language to control the initialisation of the system and a high level language as C to implement the advanced tasks in, is the optimal solution. This combination is therefore chosen.

# 3.2 Before launch

When the final design of the DTUsat-2 is finalised it is built and assembled in Denmark.

As a part of the assembling the final version of the boot and FS software is built.

After the assembling another test procedure of the final satellite is carried out. During this procedure, it is necessary to be able to communicate with FS software to upload data and applications and download test results. Therefore the FS software should contain facilities to support this.

When the satellite has been tested it is sent to the launch location where it is prepared for launch. After that it is placed in the deployment system called a P-POD, see [HT05]. In the P-POD more tests and preparations can be carried out. At this point it should be ensured that the system is setup correctly.

- The satellite should be able to communicate before through a wired connection.

- The satellite should have facilities implemented which makes it possible to communicate with when it is placed in the P-POD.

# 3.3 After launch

After the satellite has been released from the launch vehicle, the kill switch will be turned on and the EPS should test the voltage level. If the voltage level of the batteries is high enough the EPS should turn on the rest of the sub systems on the satellite inclusive the OBC. If the voltage level not is high enough the EPS will start charging the batteries instead and turn on the rest of the subsystems when the voltage level has reached the correct value.

• The boot software should test the battery level and only start the OS if it exceeds a certain level. If it does not exceeds this level the FS software should be started.

# 3.3.1 Exception and interrupt handling during the boot process

The ARM7TDMI architecture supports hardware exceptions. This subject is closely related to the notion of running the CPU in a *priviliged mode*. The CPU is able to run in the following modes:

User mode Unprivileged mode which normal user applications should run in.

- **Fast interrupt mode(FIQ)** Mode to handle *fast interrupts*. This mode has a large set of its own registers in the CPU. This enables a faster context shift than normally possible.

- Interrupt mode Mode to process normal interrupts.

- Supervisor mode (SVC) Also called software interrupts mode. This mode is a protected mode and used to handle software interrupts in .

- Abort mode Mode to handle memory faults.

- Undefined mode Mode to handle undefined instructions.

System mode Privileged mode used by the operating system.

The different type of exceptions can be divided into two groups: A group of control able exceptions i.e. the ones which can be disabled. This is the software interrupts, the IRQ and FIQ interrupts. The second group cannot be disabled and consists of reset, undefined instruction, prefetch abort and data abort.

In general the exceptions should be avoided because they raise unpredictability of the system.

The first group should be disabled as the first thing in the boot procedure. The reason for this is to raise the predictability of the system but even more important it prevents failures caused by the interrupt routines. Since no execution stack is available early in the boot process it is very difficult to implement any kind of exception handling routines. This is caused by the fact that no memory to store the values of the registers is available. Therefore any alteration of any of the registers by an interrupt routine may lead to malfunction and failure of the software after the return from the interrupt routine.

• The interrupt system should be turned off as early as possible in the boot process.

The second group of exceptions consists of the exceptions which is caused by abnormalities in the execution of the code. The only way to prevent these are by designing a well structured program. Even when this is done these exceptions could occur anyway. An 'undefined instruction' -exception could occur because of a bit flip in the memory. If this happens the system should be able handle the exception in a controlled manner.

• The system should able to handle all exceptions in a controlled manner.

#### 3.3.2 Initialisation of the WDT

Another important task which should be carried out as early as possible in the boot process is to setup and start of the WDT. This is necessary to recover the system from hardware failures during the earliest phases of the boot procedure.

• The WDT should be initialised and turned on as early as possible in the boot process.

#### 3.3.3 Location of the C stack

A major task of the boot software is to set up a C stack on which the rest of the boot and FS program can be executed on. Therefore the boot program needs to choose an area of the memory to host the stack. The most simple approach is to place the stack in the same area at every boot i.e. give the stack a static location. This is not the optimal solution since the chosen memory area could get damaged by cosmic radiation and be rendered useless. If this happened the satellite would loose its ability to boot.

Instead the boot program should place the stack in a flawless area of the memory. Before the program can do that, it needs to ensure that the chosen memory area is actually fully functional and contains no defective memory cells. To test this the boot software should carry out a memory test on the memory area used to store the stack before the stack is setup.

All the above tasks needs to be carried out by a program implemented in the assembly language because no C stack is available.

• The boot program should setup a C stack. Before doing that it should ensure that the chosen area is fault free.

#### 3.3.4 Task carried out by the C program

After the C stack has been established the rest of the tasks during the boot process can be carried out by a program implemented in the C programming language.

#### 3.3.4.1 The silence period

According to the CUBESAT Design Specification [HT05], the satellite must stay silent i.e. send no beacons or anything else for the first fifteen minutes after it has been released from the launch vehicle, and it is only allowed to send low power beacons for the next fifteen minutes (from fifteen to thirty minutes from launch). After this period it is allowed to activate its high power transmission and primary radios.

When the COMMpic/beacon module gets turned on, it will test the state pins connected to the OBC, to test whether it is allowed to start sending beacon messages or not. At the first boot just after launch these pins should be set in hold state such that the satellite stays silent for the first fifteen minutes after it has been launched. Since it cannot be detected for how long the charging of the batteries lasted it is necessary to keep the satellite silent for a fifteen minutes period to ensure that it has been silent for at least this period.

As the COMM subsystem is not designed yet, the length of its boot period is unknown. It is expected though that it is shorter than the time it takes for the OBC to startup and setup the state pins to carry the 'hold' signal. This will lead to a situation where the COMM starts to send beacons just after it has been powered on and before the fifteen minutes silence period is over. Obviously this should be avoided, and a solution to this problem is to let the beacon module wait for a short period of time every time it is turned on. The size of this period will lay in the range of a few seconds and will depend on the worst case execution time of the memory test described in chapter 4.

• The OBC should send a silence signal to the COMM and keep it for first fifteen minutes after launch.

Since reboots could occur during the silence period it should be recorded between the boots how long the satellite has been silent or how much time is left of the silence period.

• The boot software should record for how long the hold signal has been hold, and save the information in the FLASH memory periodically.

#### **3.3.4.2** The rest of the boot procedure

After the C program is started it should be able to determine whether the satellite has been booted recently. If this is the case it should also be able to determine how many times, and start the FS software if the number of attempts exceeds a certain limit.

Before the boot program is allowed to boot the satellite in nominal mode i.e. start the OS, a complete memory test of all volatile memory should be carried out. Only if no faults are found the boot software should boot the satellite in nominal mode.

In addition to verify the integrity of the volatile memory the boot program should also verify the integrity of the binary image containing the OS and the application software. If faults are encountered the FS software should be started.

- The boot program should be able to determine if the OS has been booted recently and for how many times.

- The boot program should do a complete memory test of all volatile memory except the area used by the C stack of the boot and FS software. If faults are found the satellite should not be booted in nominal mode.

- The boot program should only boot into nominal mode if the integrity of the binary files can be confirmed.

## 3.4 The system information block

During the boot procedure various pieces of information about the system state of the latest boot and the system set up in general are needed. These pieces of information are used to determine for example whether to startup the OS or not. All information which should be stored between boots are written in the system information block (SIB).

The information should be stored between consecutive boot attempts, why it needs to be stored in a non volatile memory. On the DTUsat-2 this is either the internal or external FLASH memory.

#### 3.4.1 The content of the SIB

The content of the SIB can be divided into two groups: information which is updated at every boot and rarely updated information. The first group contains information about the state of the system and the second group contains information about the software on the system.

#### 3.4.1.1 The state of the system

The content of the system state part of the SIB should contain the following values:

Launch bit The launch bit indicate whether the satellite has been silent for the first fifteen minutes after launch as demanded by the CUBESAT standard. This information is used to control whether the satellite needs to stay silent or not. It is also used to keep track of how long time the system has actually been silent if a reboot should occur during the fifteen minutes period. The value of the launch bit is set to fifteen before launch and should be decremented every time a period of one minute has elapsed. When the value of the launch bit equals zero, the fifteen minutes have elapsed. If the satellite reboots during the fifteen minutes, this counter ensures that the system can continue were it left and not has to restart on the fifteen minutes period. The name 'launch bit' is misleading because it indicates that the variable is a boolean which is not the case. The source of the name is the launch bit of the DTUsat-1 which were used to indicate whether the silence period had elasped or not. This variable only had two

legal values unlike the launch bit of the DTUsat-2 which will have at least fifteen legal values.

- **Boot counter** The boot counter stores the number of allowed boot attempts. It is used to determine whether the OS or the FS software should be booted. If the OS has been attempt booted to many times the FS should be booted instead and the earth station should be contacted.

- **Checksum** The checksum contains the checksum of the SIB exclusive the checksum itself.

**Dynamic change of the boot attempt limit** To allow the operators at the ground station to change the boot attempt limit the boot counter should be a *decrementing* counter instead of an *incrementing*. If it is decrementing it is initialised to a value larger than zero, and when a boot has been attempted it is decremented.

When it reaches zero it indicates that no more attempts to boot the OS are allowed and that the FS mode software should be booted.

If the operators on Earth want to change the boot counter they can just upload a new version of the SIB containing a different value of the boot counter.

#### 3.4.1.2 The state of the software

The second part of the system information block should contain information about the location of the OS and application software and its checksum.

- **OS beginning address** The beginning address of the binary image containing the OS and the application software.

- OS end address The end address of the binary image.

- **OS checksum** The checksum of the binary image containing the OS and the applications.

- **OS pointer** Pointer which points to the address where the execution of the OS should begin.

#### 3.4.2 The default configuration of the SIB

If the system fails to read the most recent SIB for example due to memory faults it should have a default version to fall back on. The default version is only used if errors occur. Because of this the default version of the SIB should contain the values which leads execution into the FS software. The variable which controls this is the boot counter which therefore should be set to zero.

The default configuration of the SIB should also be easy identifiable. This is because the boot software needs to be able to identify that it is not the most recent SIB which is used. The boundaries of the OS stored in the default version of the SIB should never be used to anything since the boot counter is set to zero, indicating that the FS program should be started instead of the OS. Therefore these fields could be used to identify the default SIB from.

As a consequence of this, a valid version of the SIB containing the correct boundaries, checksum of the OS and pointer to the starting position of the OS should be stored in the first SIB position in the FLASH memory before launch. An important property of this SIB is that it should have the launch bit set to 15 to indicate that the system should be silent for the first fifteen minutes.

If the boot program for some reason is unable to read the SIB placed in the FLASH before launch it will not set the hold signal to the COMM beacon module. This results in the beacon module starting to send beacons immediately after the satellite has left the launch vehicle. This is as mentioned in section 3.3.4.1 an illegal action and should be avoided. The probability that this situation should occur is extremely unlikely. The solution which protects against the occurrence of this situation demands that the default version of the SIB has the value fifteen on its launch bit. This could complicate the maintenance and usage of the satellite:

If for some reason the EPS is only able to deliver power for a period shorter than fifteen minutes and the most recent SIB is damaged, the satellite will enter a state where it is unreachable. This situation is considered worse than the extremely unlikely situation that the satellite should start sending beacons before the fifteen minutes period has elapsed just after launch.

# 3.5 The fail safe mode

The fail safe mode software is used to do maintenance on the OBC and *on board data handling* (OBDH) (the OS and the application software) which cannot be carried out while the OS is running or if the OS fails to startup. The last task is the most important since it enables the operators on Earth to get in contact with the satellite if the OS has crashed and cannot restart on its own.

To resolve these tasks the FS software needs to be able to perform the following operations:

- **Download data** The FS software needs to be able to download any data placed anywhere in the memory of the satellite. This capability should be used to download status information, and data which could be used to debugging and to trace errors.

- **Upload data** The FS software needs to be able to upload any data to any location in the memory of the satellite (except for the area containing the boot and FS software). This capability should be used to replace the OS and OBDH. It could also be used to upload special programs which should be used for debugging purposes or carrying out special tasks on the satellite. Finally the capability could be used to place new system information after replacement of the OS.

- **Execute programs** The FS software should be able to start execution of code for any memory address in the satellite. This facility should be used to start any uploaded programs.

- **Collect status information** The FS sofware should be able to collect and return every kind of status information generated on the satellite. This facility should be used collect status information which could be used during diagnostics of faults in the satellite.

Of course a lot of scenarios of failure situations should be considered while analysing the satellite. First of all it should be determined which minimum preconditions are necessary in order to execute the FS software and get in contact with Earth:

- 1. The EPS needs to be in working condition such that power is supplied to the other subsystems of the satellite (at least the OBC and COMM).

- 2. The OBC needs to be in such a condition that the CPU chip and the ROM chip containing the boot and FS software, can work and communicate,

such that the boot program is able to start and run. This also demands the internal FLASH of the CPU chip to work since it contains the boot loader which startup the chip.

3. Finally the radio needs to be in such a shape that commands and data can be sent between the ground station (GS) and the satellite.

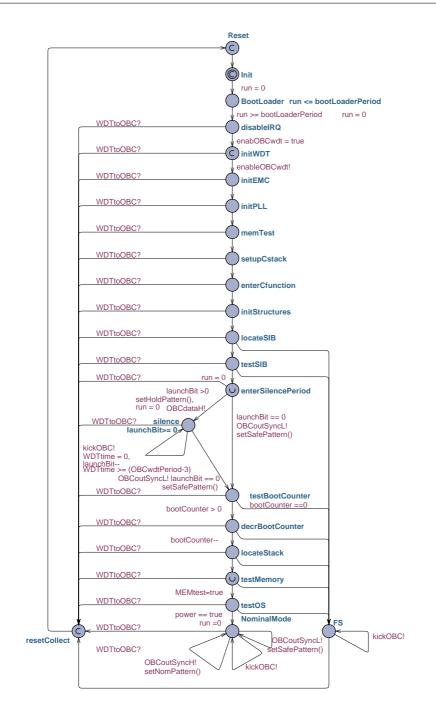

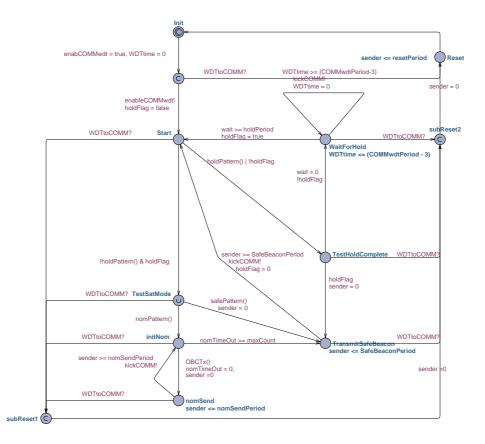

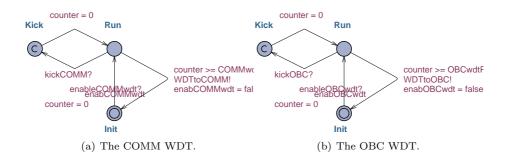

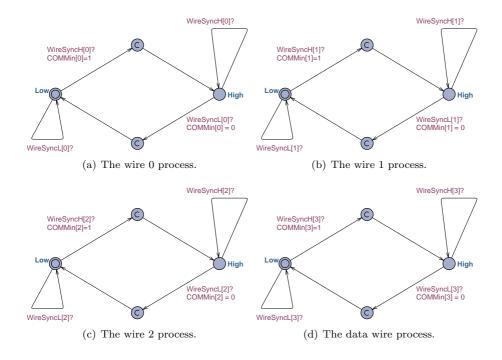

As it is seen neither the external RAM nor the external FLASH memory need to be in working condition. Other subsystems of the satellite could also be defective in some way without necessarily influencing the execution of the FS software. The satellite could be in a condition where the systems needed to start up the FS software are in working condition but where the lack of other subsystems makes it impossible to run the satellite in nominal mode. This is of course not a desired situation but as long as any contact to the satellite can be established the satellite is usable to some extent.