# Virtual Circuits in Network-on-Chip

Master of Science thesis nr.: 87

Technical University of Denmark Informatics and Mathematical Modelling Computer Science and Engineering

Lyngby, 18th of September 2006

Supervised by Jens Sparsø Co-Supervised by Mikkel Stensgaard

s011493 - Christian Place Pedersen

#### Abstract

This project investigates virtual circuits circuits in Network-on-Chip, specially how virtual circuits can be used to give guarantees on bandwidth and latency requirements. The project is in two parts: A study, which investigates guaranteed service in NoC implementations and an extension of the virtual circuit support in MANGO.

The study conducted in this project examines seven different NoC implementations both academic and industrious. The main focus of the study is to investigate the different approaches to guaranteed service.

The second part of this project describes the implementation of reconfigurable virtual circuits in MANGO, an asynchronous NoC developed in the PhD thesis by Tobias Bjerregaard, at IMM, DTU. The implementation presented here offers flexible programming of virtual circuits as well as reuse of virtual channels.

## Acknowledgements

This Master of Science thesis has been carried out at the Computer Science and Engineering division of Informatics and Mathematical Modelling department at the Technical University of Denmark, during 2006.

I would like to thank my supervisor Jens Sparsø for his guidance, discussions and support during the course of this project. I would also like to thank co-supervisor Mikkel Stensgaard for his most valuable inputs, ideas and support. Thanks to Tobias Bjerregaard for providing insight in MANGO and to Matthias Stuart for the discussions on MANGO and NoC implementations.

## Contents

| 1 | Intr | oduction                              | 1  |

|---|------|---------------------------------------|----|

|   | 1.1  | Previous Work                         | 2  |

|   | 1.2  | Project Description                   | 2  |

|   | 1.3  | Report Structure                      | 3  |

| 2 | Don  | nain Introduction                     | 5  |

|   | 2.1  | Network-on-Chip                       | 5  |

|   | 2.2  | Quality of Service                    | 13 |

|   | 2.3  | Use Cases                             | 14 |

|   | 2.4  | Asynchronous Circuits                 | 17 |

| 3 | A N  | etwork-on-Chip Study                  | 21 |

|   | 3.1  | Hermes                                | 22 |

|   | 3.2  | QNoC                                  | 22 |

|   | 3.3  | Octagon                               | 24 |

|   | 3.4  | NOSTRUM                               | 25 |

|   | 3.5  | Æthereal                              | 28 |

|   | 3.6  | SoCBUS                                | 30 |

|   | 3.7  | MANGO                                 | 32 |

| 4 | Gua  | ranteed Service with Virtual Circuits | 35 |

|   | 4.1  | Abstraction of Virtual Circuits       | 36 |

|   | 4.2  | Programming Model                     | 37 |

|   | 4.3  | Distribution of the Use Cases         | 38 |

|   | 4.4  | Network State                         | 40 |

| 5 | The  | <b>r</b>                              | 41 |

|   | 5.1  | 2                                     | 41 |

|   | 5.2  |                                       | 43 |

|   | 5.3  | Best-Effort Routing                   | 44 |

| 6 | Rec  | onfigurable Virtual Ciruits in MANGO  | 47 |

|   | 6.1  | -F                                    | 47 |

|   | 6.2  | Reusable Virtual Channels             | 48 |

|    | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul> | Programming the Network Adapters       | 52<br>54<br>54<br>55<br>58 |

|----|-----------------------------------------------------------------------------|----------------------------------------|----------------------------|

| 7  | <b>Test</b><br>7.1                                                          | <b>ing</b><br>Test Example             | <b>63</b><br>66            |

| 8  | Disc                                                                        | ussion                                 | 67                         |

| 0  | 8.1                                                                         | NoC Status                             | 67                         |

|    | 8.2                                                                         | The Status of MANGO                    | 68                         |

|    | 8.3                                                                         |                                        | 69                         |

|    |                                                                             |                                        |                            |

| 9  | Con                                                                         | clusion                                | 71                         |

| Bi | bliogr                                                                      | raphy                                  | 73                         |

| A  | Imn                                                                         | lementations                           | 77                         |

| 11 | A.1                                                                         | Handshake Conversion                   | 77                         |

|    | A.2                                                                         | NA Programming                         | 78                         |

|    | A.3                                                                         | Acknowledgement                        | 78                         |

|    | A.4                                                                         | Best-Effort Router                     | 79                         |

| р  | <b>T</b> 4                                                                  |                                        | 01                         |

| B  | Test                                                                        |                                        | 81                         |

|    | B.1                                                                         | The Mangofy Script                     | 81                         |

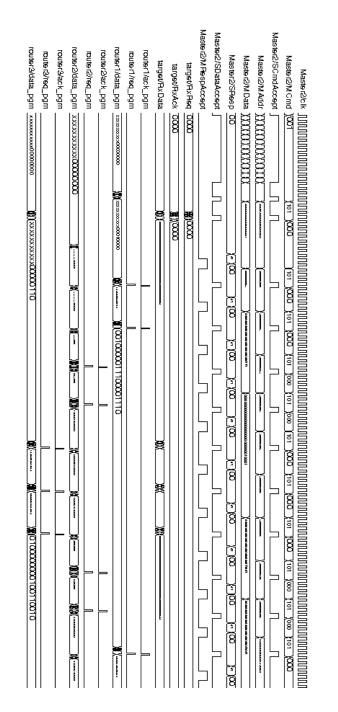

|    | B.2                                                                         | Wave traces                            | 82                         |

|    | B.3                                                                         | Configuring BE Paths Remotely          | 82                         |

|    | B.4                                                                         | Reuse of a VC and remote circuit setup | 83                         |

| С  | Sour                                                                        | rce Code                               | 87                         |

|    | C.1                                                                         | key.v                                  | 87                         |

|    | C.2                                                                         | lut_arb.vhd                            | 88                         |

|    | C.3                                                                         | gen_acknowledge_39.v                   | 90                         |

|    | C.4                                                                         | BE_behav.v                             | 92                         |

|    | C.5                                                                         | The Test Net                           | 04                         |

|    | C.6                                                                         | The Test Bench                         | 16                         |

|    | C.7                                                                         | OCP Master                             | 21                         |

|    | C.8                                                                         | OCP Slave                              | 25                         |

v

## **List of Figures**

| 2.1  | Communication structures                         |

|------|--------------------------------------------------|

| 2.2  | Basic NoC elements                               |

| 2.3  | Interfaces in NoC                                |

| 2.4  | NoC topologies                                   |

| 2.5  | Deadlock                                         |

| 2.6  | A Virtual Channel                                |

| 2.7  | Network abstraction layers                       |

| 2.8  | An use case example                              |

| 2.9  | A use case example with a set-top box            |

| 2.10 | Asynchronous Protocols                           |

| 2.11 | The Muller C-element                             |

| 2.12 | A handshake latch                                |

| 2.13 | Data flow in asynchronous circuits               |

| 3.1  | Basic Octagon Configuration    25                |

| 3.2  | Temporally Disjoint Networks                     |

| 3.3  | The Æthereal configuration process               |

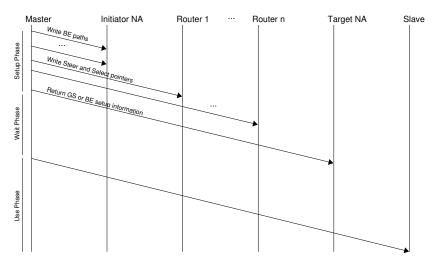

| 3.4  | Transactions in the SoCBUS network               |

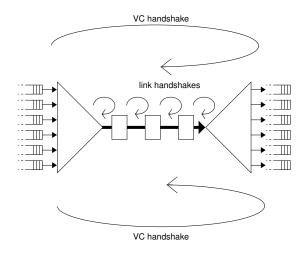

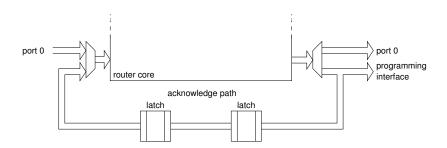

| 3.5  | A complete ALG link                              |

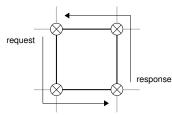

| 3.6  | Overlapping VC handshakes                        |

| 4.1  | Two virtual circuit using virtual channels       |

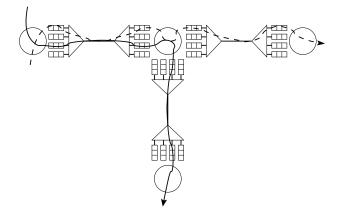

| 5.1  | GS Setup in MANGO                                |

| 5.2  | The MANGO NA         44                          |

| 5.3  | Basic NoC elements    44                         |

| 6.1  | A Virtual Channel in MANGO                       |

| 6.2  | Virtual Channel implementation in a MANGO router |

| 6.3  | New location of the key                          |

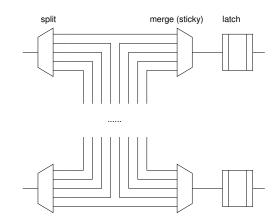

| 6.4  | The Gated Merge                                  |

| 6.5  | The configuration register inside the NA         |

| 6.6  | Configuration through NI                         |

| 6.7  | Acknowledge in the BE router                     |

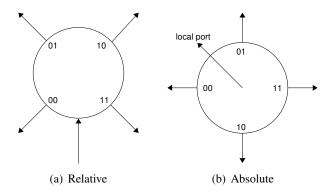

| 6.8  | XY-routing in a mesh net                         |

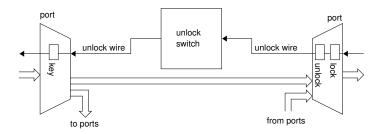

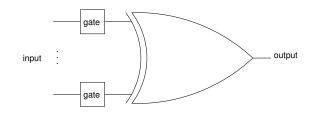

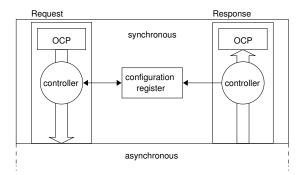

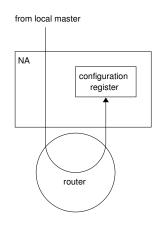

List of Figures 6.9 59 60 7.1 63 7.2 66 A.1 Gate level diagram of the key. 77

## CHAPTER 1

## Introduction

A System-on-Chip (SoC) is as the name suggests, a system made up of smaller subsystems on the same chip. These subsystems can be anything from general processing units over application specific units to memory modules and interfaces. Because the subsystems can be tailored to a specific application or be very general and broad, SoCs can cover a great range of applications and products, from small, low power embedded systems that have very thight constrains on area and power to large general systems that can handle a broad range of applications. By introducing subsystems into the design process, individual components can be designed and verified which makes the process of designing and verifying the entire system easier. In addition, the SoC approach allows for reuse of subsystems, which enables the creation of intellectual property cores (IP cores) that can be designed and used in several SoCs. This allows for a large amount of reuse which greatly decreases the time it takes to construct even large and complex SoCs.

The SoC approach to system design allows the system designer to plug IP cores toghether, through a common interface via an interconnect. In many cases, this interconnect is a bus structure or point-to-point links. As CMOS technology has scaled down, the cost of wires - i.e. communication - can no longer be neglected. To cope with the increased capacitance on a bus as more IP cores are connected, segmented busses are being used, but at the cost of increased latency and lower bandwidth for each IP core. To maintain and even increase the performance of the communication infrastructure in very large SoCs, alternative communication infrastructure are being investigated.

In recent years Network-on-Chip (NoC) has received increasing interest as an approach to handle the on-chip communication of large scale SoC. A network is characterised by having segmented links connected through intermediate points that route information incoming on one link to another of the connected links. NoC addresses many of the challenges that rise from scaling busses and point-to-point links to facilitate the increasing number of IP cores. Many of the solution can be adopted from research already done within the field of large scale networks, such as the Internet.

New challenges and possibilities arises from NoC, such as guaranteeing bandwidth and latency between IP cores.

As all IP cores are connected to the network, NoC enables logical point-to-point links between all IP cores. This increases the flexibility of the SoC, which can be used by introducing use cases. A use case is a way to describe the use of the network. The SoC can thus handle different applications with the same hardware, which gives the chip a larger market.

## **1.1 Previous Work**

Due to the rise in NoC research, several implementations of the NoC concept have been proposed and described both in the academic world and in the industry. The implementations investigate different aspects of the design spectrum within NoC.

The following networks are developed and described in the academic world.  $\times$  pipes [4] is a library of network components that can be put togheter using a designated compiler, [19], that allows different network architectures. CHAIN [1] and SPIN investigate different tree-topologies, but differ greatly as CHAIN is an asynchronous implementation where SPIN is synchronous. QNoC [10] is another synchronous network that uses virtual channels to give statistical guarantees on connections in the network. SoCBUS establishes an end-to-end connection for all data transfers across the network. MANGO [5] is a feature rich asynchronous NoC that offers among other things hard guarantees on bandwidth and latency between the connected IP cores.

In the industry, the NoC adoption has been sparse, but academic implementations have resulted in spin offs as fx. CHAIN [2] which is now developed by Silistix [18]. Philips Research has also implemented and described a synchronous NoC called Æthereal [16] that offers both best effort traffic and guaranteed service connections. The guaranteed service connections divides the time to multiplex the links in the network. In addition, Æthereal can be reconfigured to support different application requirements at runtime. Lastly IBM, Sony and Toshiba's Cell processor [20] uses a so called Element Interconnect Bus which bears great resemblance to the NoC concept.

## 1.2 **Project Description**

This project will build upon MANGO inorder to investigate how more flexibility can be added to the guaranteed service connections used by MANGO to provide hard guarantees on bandwidth and latency. Allowing for more dynamic uses of the MANGO NoC.

The MANGO NoC has been designed at IMM DTU, by Tobias Bjerregaard in his PhD thesis [5]. MANGO is a novel implementation of the NoC concept and is characterised by being asynchronous and providing hard guarantees on both bandwidth and latency. This is accomplished by introducing guaranteed service connections based on virtual channels on the intermediate links inside the network, creating end-to-end virtual circuits. MANGO's virtual circuits can be setup - at runtime - between any two IP cores, i.e. the virtual circuits can be tailored to meet the requirements of a wide range of applications on the same hardware.

Furthermore this project will take a look on the state of current NoC implementations, with focus on the guaranteed services approaches taken.

The main challenge in this project is to determine and in turn implement the extra feature that is needed to allow for dynamic reconfiguration of connections in the MANGO NoC. The solution will aim to provide a flexible approach to how the virtual circuits can be used and created.

## 1.3 Report Structure

The report is in two major parts. Part one, consisting of chapter 2, 3 and 4, is an introduction to the NoC domain. Chapter 2 describes general NoC concepts and introduces Quality-of-Service as it is used in this project, furtheremore use cases as a general way of describing traffic patterns in SoC design is described. Lastly, the chapter introduces asynchronous circuits. In chapter 3, a study of different NoCs and their take on Quality-of-Service is described. Chapter 4 discusses virtual channel specific topics.

Chapters 5, 6 and 7 make up part two about MANGO and the modifications and extensions that are done in this project. Chapter 5 thoroughly describes the MANGO NoC, with focus on the parts that must be taken into consideration when guaranteeing service. The extensions and modifications conducted in this project are described and discussed in chapter 6. Chapter 7 describes the test, which have been conducted as part of this project. Finally chapter 8 and 9 holds the discussion and conclusion respectively.

## CHAPTER 2

## **Domain Introduction**

This chapter introduces the basic concepts built upon in this project. First, an introduction to Network-on-Chip is given, followed by a description of which services can be offered by a communication structure. The term use case is then introduced and described in the context of NoCs. Lastly, a short introduction to asynchronous circuits is given.

## 2.1 Network-on-Chip

The NoC concept shares many concepts and features with large scale network, such as those created between computers in fx. the Internet. One of the great differences is that a NoC is static in contrast to most large scale networks that have to cope with ever-changing routes and number of connected users. This affects the design choices such as the transmission protocol and flow control. In addition, because a NoC is a closely coupled environment, data loss and corruption can be neglected in most cases.

In this section, basic concepts, distinctive features and terms of Network-on-Chip (NoC) will be described and discussed. Then more advanced topics within NoC are described. These topics include interfaces, topology, protocols and flow control. Lastly, different abstraction levels of the NoC and their effect on the overall SoC design process will be discussed.

This section is based on the terms and concepts introduced in [9], where a survey of the current state of NoC research and practises can be found.

### 2.1.1 Basic Concepts

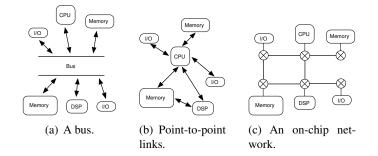

As the CMOS technology develops, transistors shrink in size, causing the wire resources to make up a larger part of the overall system. Therefore, the on-chip communication structure also takes up more of the overall ressources in a SoC. In addition, the most commonly used types of communication structures in SoC - bus (figure 2.1(a)) and point-to-point (figure 2.1(b)) links, scale poorly when more subsystems or IP cores are added to the system. NoC-based systems as the one seen in figure 2.1(c) try to cope with the problems that arise when scaling a bus and point-to-point links.

Figure 2.1: Examples of communication structures: 2.1(a): a bus, commonly used in SoC; 2.1(b): point-to-point links, used for high performance links and 2.1(c): network, segmented links connected by routers.

Figure 2.2 shows the basic elements of a NoC in SoC. These basic elements can also be thought of as abstraction levels which will be detailed in section 2.1.7. The basic elements of a NoC are:

- **IP Cores** are not part of the NoC, but are shortly described here. They are connected to the network interfaces and make use of the services provided by the network to gain access to another resource in the system. A core can typically either initiate requests, be the target of these requests or have both capabilities. The cores have different roles ranging from general processing units over signal processors and I/O controllers to storage such as RAM.

- **Network Adapters** (NA) provide the *interface* to the IP core through which the network *services* can be accessed. The NA encapsulates the data provided on the core interface into *packets*, which are again spilt into flow control units (flits) before they are sent into the network through the NAs network interface. Flits are used in order to minimise the need for buffers and wires in the network.

- **Routers** or switches routes data on the links in accordance with a chosen routing protocol. The router *routes* the data flits from one point in the network to another. The routers are arranged in a *topology* and they handle *forwarding* and *flow control* of data between the network adapters. The routers generally connect a number of links and one or more network adapters.

- **Links** are a group of bundled parallel wires that run from one point to another point on the chip. The data width of the links depends on the number of wires bundled together, and how many control signals that are used. On the links,

IP core IP cor

data is transmitted one flit at the time. Links connect routers to other routers and to network adapters.

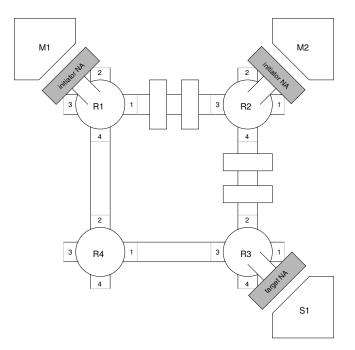

Figure 2.2: A 3x3 2 dimensional NoC. The basic elements of a NoC include: Network adapters, routers and links. Connected to the network adapters are IP cores, such as computational units, memory and I/O.

## 2.1.2 Interface

Because a NoC is just another implementation of a communication structure suited for SoC, each communication structure should present the same interface to the core. By using a common interface or socket, the system designers can choose different communication structures and other IP cores that suite their specific needs. An example of such a common interface is the Open Core Protocol (OCP) [30] interface which provides a master and a slave interface for initiating and receiving request respectively. To make use of some special services that are provided specifically by a communication structure, the system must be aware of these services. In the case of NoC an IP core is said to be network aware and can therefore make use of the extra features and services. A NoC can for example offer guaranteed bandwidth between any two of its interfaces in the network, an IP core must be aware of this feature in order for it to setup connections.

### 2.1.3 Network Adapter

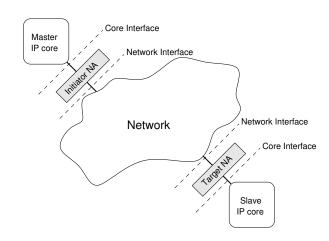

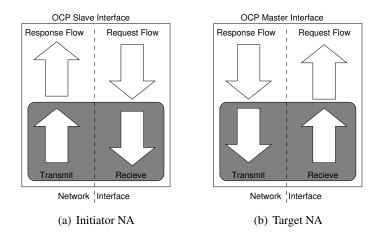

The network adapter (NA) communicates with the IP cores through what is called the core interface (CI) in this report. The NA transforms the request from the core into a request that can be transmitted by the network, through the network interface (NI). Figure 2.3 shows the interfaces and how they are used to make the network transparent for the IP cores. This allows for the network to be clocked by another clock

Figure 2.3: The NA translates between a core interface presented to the cores and a network interface presented to the network.

or no clock at all, allowing Globally Asynchronous Locally Synchronous (GALS) systems. The NA then handles the synchronisation between the different domains, further allowing each IP core to be clocked individually.

The figure also shows how the terms regarding master-slave interface are used in this report. A master IP core initiates request to a target slave IP core. Therefore, the master IP core is connected to a slave port on the network and a slave core is connected to a master port on the network. To avoid confusion, the term initiator NA is used in this report when describing the NA connected to a master IP core and the slave IP core is connected to the target NA. This means that requests are transmitted from the initiator to the target, while responses are transmitted from the target to the initiator. It should be noted that a target NA is always the target of requests and is thus the NA that receives a request and generates a response if needed.

### 2.1.4 Topology

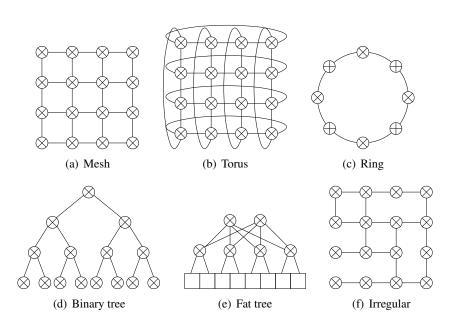

The network topology defines how the routers in the network are connected. A collection of network topologies that are used in NoCs are shown in figure 2.4. Topologies can be grouped in several ways: direct networks and indirect networks; homogeneous and inhomogeneous.

In direct networks, each router has at least one IP core directly connected, whereas in the indirect networks some routers are only connected to other routers and only designated routers are connected to IP cores. A mesh network, figure 2.4(a), is a typical example of a direct network and tree structured networks, figure 2.4(d) and 2.4(d), are examples of indirect networks where only the leafs of the tree are IP cores. However, an indirect mesh network can be created by only connecting IP cores at the edges of mesh and the trees can be made direct by adding IP cores to all nodes in a tree.

Figure 2.4: Different NoC topologies.

A homogeneous network is a network that scales in a predictable way, such as mesh, ring (figure 2.4(c)) and balanced trees do. Inhomogeneous networks such as the irregular network shown in figure 2.4(f) are arranged to suit the needs of a specific application in order to optimise the overall system, i.e. area, power or speed. Optimising the network by clustering IP cores that have a high amount of communication with each other decreases latency and switching activity resulting in better performance and a lower power consumption. Clustering can be done by creating irregular topologies or by mixing topologies to form a more optimised topology for that specific application. The cost however is that the flexibility of the system is lowered because while the system might perform very good when running that particular application, it may not be a viable solution for other applications.

Figure 2.4(b) shows a torus network that differentiates itself from the mesh network by connecting opposite edges and by usually having unidirectional links, where most other topologies favour bidirectional links. The torus network performs poorly on applications with high amounts of local traffic, but comes at a relative low cost in area due to having unidirectional links. Ring networks 2.4(c) are not common in NoC, but as shall be seen in 3.3 they can make for an interesting topology.

## 2.1.5 Protocol

A protocol describes how data is transferred from one point in the network to another point. In line with [9] switching is used here as transport of data, while routing determines the path the data takes.

NETWORK-ON-CHIP

Most NoCs today employ *packet switching* where packets are forwarded through the network in flits. The most commonly used forwarding strategies are store-andforward and wormhole. In a *store-and-forward* routing based network the router receives and stores the entire packets, i.e. it buffers multiple flits, and then forwards the packet based on the routing information held within the packet. Store-and-forward is the strategy most commonly used in macro networks, but can also be found in some NoC implementations. *Wormhole* routing is chosen in most NoC implementation, because it tries to minimise packet latency. The routing decisions in the routers are made on basis of the first flit in the packet and all the subsequent flits are forwarded as they arrive, thus also minimising the need for deep buffers in the routers. The downside of wormhole routing is that a large part of the network can be stalled if a worm of data is stalled itself, thus spanning several routers and blocking for yet other worms of data. There are however techniques to avoid this, one of which is called virtual channels, which will be described in greater detail later in this report.

Opposite packet switching is *circuit switching*, where a circuit is set up from source to destination and data is then transported on the circuit. Circuits may be dynamically setup and torn down as they are used or they may be statically created in the network prior to execution.

*Connection-oriented* mechanisms are dedicated or logical connection paths setup from sender to receiver before data is transmitted, which are torn down after use. Hence a circuit switched network is always connection-oriented. *Connection-less* networks do not setup connections, rather the sender transmits the data onto the network which then forwards it to the receiver. Packet switched networks can be either connection-oriented or connection-less, and as in the case of Æthereal both can be available in packet switched networks. Æthereal is examined in more detail in section 3.5. A very interesting example of a connection-oriented packet switched NoC is SoCBUS which will be described further in section 3.6.

When using a *deterministic routing* algorithm the path followed in the network is only based on the source of the packet and its destination. Source routing is a deterministic routing algorithm where the path through the network is decided by the source alone, whereas in XY-routing (mesh and torus networks) which is also a deterministic algorithm, the packet is routed fully along one axis and then fully along the other axis to arrive at its destination. In *adaptive routing* schemes the routing decisions are taken dynamically on a per-hop basis, and the decision can be based on congestion in the surroundings. NOSTRUM uses an extra wire between routers to signal congestion and then routes packets around the congested links. A more thorough investigation of NOSTRUM is conducted in section 3.4.

*Minimal routing* always follows the shortest path between sender and receiver. If the shortest path is not taken it is said to be *non-minimal*. The HERMES NoC employs a minimal routing algorithm and will be looked further into in section 3.1.

### 2.1.6 Flow Control

Flow control is the mechanisms that controls the flow of packets through the network, on both a global and a local scale. It ensures that the operation of the network is correct, such as avoiding deadlocks. Flow control can be extended to control the utilisation of the network resources, which can be used to improve the performance and give guarantees on data transfers. Here, flow control issues and the concept of virtual channels is briefly described.

As mentioned above, flow control is about ensuring the correct operation of the network, which means that it must avoid deadlocks. A deadlock is when network resources are waiting for each other to be released. A classical example of a deadlock is shown in figure 2.5. Deadlocks can be avoided by breaking cyclic dependencies in the resource dependency graph. A closely related problem in networks is livelock. Livelock is less common than deadlocks and occurs when resources constantly change state without getting anywhere.

Figure 2.5: Four streams of data wait for each other to release the occupied network resources, resulting in a deadlock.

In every network, macro network as well as NoCs, buffers play an important role. They provide decoupling on the segmented links in the network. In NoC design, buffers account for a very large part of the overall router area, and it is therefore a concern to minimise the size of the buffers. Two things contribute to the buffer size, the data width and the depth of the buffers. It has been shown that deeper buffers do not solve congesting problems but rather delay it. However, deeper buffers do smooth out burst traffic. Buffer placement is another topic within NoC design. Fx. placing buffers at the input results in packets being blocked behind a packet that is unable to leave through its designated output port.

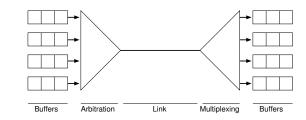

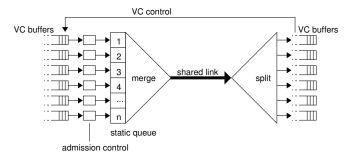

Several independent buffers can be used to share a physical link. This is called *virtual channels* (VC). A physical link is typically shared between 2 to 16 VCs which involves a matching number of buffers and an arbitration mechanism. Figure 2.6 shows an example of four VCs across a link. VC implementations therefore introduce a power and area overhead, because of the extra buffers in the routers. The advantage of VCs is that they can be used to break dependencies within the network, thus avoiding deadlocks. Wire utilisation can be optimised, performance can be improved due to fewer stalls in the network and VCs can be used to offer differentiated quality of service by reserving a certain priority in the VCs along a path to form vir-

Figure 2.6: A link with four buffers and the arbitration mechanism.

tual circuits. A more in depth discussion of VC and virtual circuits is presented in chapter 4.

### 2.1.7 Network Abstraction

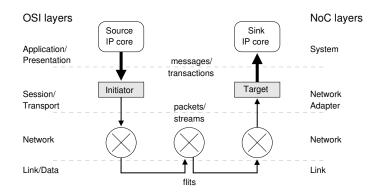

When designing a SoC, the communication structure can be abstracted at different levels. The most common model used to abstract networks is the OSI model which consist of 7 layers. In NoC some of the OSI layers are redundant due to the inherent differences between macro networks and NoCs. Due to these differences, a collapsed model is introduced in [9] that matches NoC usage. The collapsed model which is shown in figure 2.7 will be used in this project. The figure shows the collapsed model and the corresponding OSI layers, as well as communication directives between the different layers.

Figure 2.7: OSI layers and the adapted NoC abstraction layers.

The four different layers shown in the above figure also represents different abstractions of the NoC. A high level abstraction model plays an important role in the SoC design process, as it allows greater complexity to be captured. However, the lower levels are also an important part of the design process, as the awareness in the system of the lower levels can lead to better performance. In the following, the four layers depicted in figure 2.7 will be described.

#### System

The highest layer in the NoC model consists of processes and system architecture. The network details are mostly hidden at this level. At this level, the system only considers a generic communication structure and most SoC research applies at this level. The different processes of the system are communicating by passing messages back and forth between each other. In the process, the communication can be thought of as high level send and receive statements. In a CSP like language the sender would have a send statement, *send(message, receiver)*, and the receiving process would then wait for the message with a receiving statement, *receive(message, sender)*.

#### **Network Adapter**

The job of the network adapter is as mentioned earlier to decouple the IP cores from the network, as well as handle end-to-end flow control. As an abstraction layer this is the first layer that adds network awareness, in such a way that packets and streams are distinguished. Messages from the system level above are broken into either packets or streams. Packets contain information on their destinations placement in the network, whereas the streams follow pre-configured routes to their destination that has been set up prior to the transmission. A packet would be send in a more specific way than the messages above, code for transmitting a packet would look like *send\_packet(packet, destination\_address)* and a stream would be transmitted with *stream\_data(data, circuit)*.

#### Network

At the network layer, the network is described in terms of routers and links, thus the topology of the network can be described at this level. Routing and transport protocols are considered as well as the flow control in between the routers.

#### Link

This is the lowest layer in the NoC abstraction model and at this level the atomic units of a transmission, the flits are considered. Data encoding and synchronisation is considered at this level.

## 2.2 Quality of Service

A network can provide Quality of Service (QoS) to the cores connected to it. Different levels of service can be offered to the cores, thus QoS is defined as a quantification of the service level.

Services such as low latency, high through-put and controlled jitter, are interesting for real time applications and other applications that require guarantees on the transmission services. Services of increasing quality are offered in the different layers of the network abstraction model described in section 2.1.7. Services which can be characterised as high level services are offered in the high abstractions layers and build upon services from the lower layers. Examples of services that build upon each other from the bottom and up are given in the following.

| USE CASES |  |  |  |  |

|-----------|--|--|--|--|

|           |  |  |  |  |

|           |  |  |  |  |

*Lossless* service guarantees that data transmitted arrives and is received as it was sent, i.e. no error is introduced in the data delivered by the service. Together with *in order* delivery, that ensures that a data packet B, transmitted after a data packet A, will never be delivered before A, this provides the basis for guaranteed service (GS).

14

GS provides guarantees on transmission specific parameters such as through-put and latency. *Guaranteed through-put* enables streamed data to arrive at a constant rate and *guaranteed latency* ensures that the latency on data transmissions such as read and write operations have a maximum latency.

The guarantees are offered differently in different NoC implementations. The asynchronous MANGO NoC, described in more detail in section 3.7 and in chapter 5, offers hard guarantees whereas QNoC offers statistical guarantees. More on QNoC and the concept of statistical guarantees in section 3.2.

## 2.3 Use Cases

A use case is a way to describe the communication requirements of a system. In [26] use cases are used as input to the mapping tool used to generate a NoC - more specifically the Æthereal NoC. This section will give an introduction to use cases, their use in NoC design and how multiple use cases can be exploited to optimise NoCs.

A use case describes the traffic pattern i.e. which cores need to communicate, the bandwidth and latency requirements and the traffic types. The use case can be used to plan the traffic. By planning the traffic, power consumption can be lowered as well as optimising overall performance in the network. By distributing the traffic equally over the network, congestion points in the network can be avoided to a large extent. General network layouts can be tailored to meet specific requirements of an application, thus allowing the network and in turn the entire system to handle a wide range of applications. In NOSTRUM, circuits are setup at run time, but the allocation of bandwidth to each circuit can be configured during run time allowing the same fabricated chip to meet bandwidth requirements of several applications.

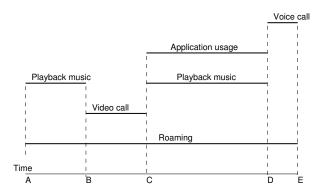

The application domain of SoCs ranges from digital hearing aids over multimedia phones to set-top boxes, all of which are applications that handle several tasks simultaneously. An example of a use scenario involving a multi-media phone is shown in figure 2.8. If the roaming and GSM specific traffic is discarded the figure shows four different typical phone tasks; voice call, general application usage, music playback and video call. Each of the four tasks presents different requirements to the system. In addition some of the tasks are executing in parallel creating yet more constraints and requirements for the system.

Playing back or streaming audio requires a low jitter and a constant bandwidth connection between a signal processing unit and the audio output. In addition the audio stream can either be stored locally requiring access to off-chip storage, or the audio stream can be acquired across the GSM net requiring access to the RF device. Video calling requires a low and constant latency between IP cores in the system along with some high bandwidth connections to support the video de- and encoding. General application usage such as text messaging, playing games or browsing the Internet generally has lower requirements and can in many cases be handled by best-effort type services. Voice calls requires, as the video call low latency and jitter free connections between RF devices, signal processors and audio input and output devices.

The figure can be segmented into several parts in different ways. Each of the four tasks has requirements that could be described by a use case. However from a system point of view the segmentation shown along the time axis, A to E, into use cases makes more sense. Such a view can be obtained by creating use cases that encapsulate all the tasks that run in parallel. Such a use case completely describes the use of the system in that time interval. As mentioned earlier, the general applications of SoC involves multiple tasks, some of which can execute in parallel. Therefore the use of a system can rarely be described by one use case which leads to having multiple use cases describing the requirements at different times, even more use cases than there are tasks. Use cases can be used to make an application run on a specific SoC, by specifying circuits, routes and services to setup. Use cases can also be used as input to a mapping tool laying out the system to meet the requirements of a specific application.

### 2.3.1 Multiple Use Cases and Mapping

When considering multiple use cases, the requirements to the communication structure become more complex, as the requirements are now distributed between multiple use cases. In the following, only NoC is considered, but some of the discussion here

Figure 2.8: An example of how a mobile multi-media phone could be utilised. From A to B the user of the phone listens to some music, from B to C a video call is received, followed by the user interacting with some build in applications while playing more music from C to D. Lastly the user is making to different times. a voice call D to E, during the entire use the phone is handling roaming and other GSM network specific operations.

USE CASES

also applies to other communication structures such as configurable crossbars. One method used in NoC research to handle the problem of how to find the requirement of each connection, when the information is segmented between several use case is to construct a worst case use case. This approach is taken in [26], which uses the worst case use case to map the Æthereal NoC. The NoC mapped from the worst case use case is however most often over engineered, which leads to a bigger design and a higher power consumption. The same group of authors has since described another method to solve this problem that leads to less overhead, by keeping track of requirements during the mapping process. They also introduce the concept of smooth switching, and that approach will be described later in this section.

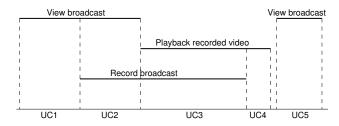

The Viper [14] is a multiprocessor SoC (MPSoC) developed by Philips Research and is designed for use in set-top boxes. Viper features two general processors (a MIPS CPU and a TriMedia CPU), along with several dedicated processors and I/O interfaces. A set-top box such as the Viper is a prime example of a MPSoC and the need for multiple use cases. Figure 2.9 illustrates a possible use case scenario for a set-top box such as the Viper. The figure shows examples of four use cases, displaying a broadcast, recording a broadcast while viewing another, playing a recorded video while recording a broadcast and only playing a recorded video. When creating use cases, all possible interleavings of system tasks must be considered and placed into several different use cases, creating a large amount of use cases. The important thing is that not all interleavings are possible, fx. a set-top box will not at any time playback a recorded video, while at the same time viewing a broadcast. The exception being picture-in-picture, where several video streams or broadcasts are shown on the screen in smaller partitioned areas, which again could be described by a use case.

Figure 2.9: A use case example with a set-top box.

The authors of the above mentioned worst case use case has described another approach of mapping multiple use cases to a NoC in [27]. In addition, they introduce the concept of smooth switching. Smooth switching is an important feature as switching between use cases involves reconfiguration of the NoC, which might cause interruptions or delays in ongoing communication. Such a delay or interrupt would not be acceptable in many multi-media applications, and smooth switching addresses just that problem. In addition to specifying use cases, the authors also specify which use cases that should be able to smoothly switch to another use case without interrupting tasks that survives the switch. The communication of these tasks can then be mapped in the network to avoid interruption when other tasks are stopping and starting. This is done by creating use cases that can handle all the tasks of the use cases that can smooth switch in between each other. It should also be noted that not all switches has be smooth, one example being the switch between UC4 and UC5 in figure 2.9.

To avoid creating the very large amount of use cases by hand, [27] presents the approach of creating use cases for all the tasks of the system and then grouping use cases that run in parallel together in compounds. In addition, they specify which use cases should be able to handle smooth switching in between them. All this information is then fed into a mapping tool that creates all the different use cases and maps the requirements to a NoC. They avoid the overhead of their previous approach where they used worst case to construct the network, by considering the overall constraints when mapping each individual use case.

## 2.4 Asynchronous Circuits

Asynchronous circuits are clockless circuits, which as opposed to synchronous cicuits do not have a global synchronisation. Instead, asynchronous circuits make use of local handshakes. This chapter gives an introduction to asynchronous circuits and especially the concepts used in this report. A comprehensive introduction to asynchronous circuits can be found in [32].

Asynchronous circuits are interesting to explore, due to some of the inherent properties, such as *lower power consumption*; *high operating speed*; *less emission of electro-magnetic noise*; *robustness towards enviroment variations*; *better composability*; and *no clock distribution problems*. Of course, these advantages come at a cost and just like synchronous implementations there are trade-offs to be made. One of the disadvantages with asynchronous circuits is the lack of design and test tools, which makes implementation and verification a tedious job. In NoC, asynchronous circuits are especially interesting due to their composability and the fact that no clock has to be distributed over the entire chip. Where in synchronous circuits the entire system is limited by the slowest path in the system, asynchronous circuits do not have this global dependency and therefore does not suffer from this dependency. The behaviour of asynchronous circuits depends on the data, which makes them hard to predict and depending on the implementation style this can affect the execution time and power consumption.

Asynchronous circuits inherently support the Globally Asynchronous Locally Synchronous (GALS) scheme, which makes them very suitable for NoC implementations. The main themes when designing asynchronous circuits are handshake protocols, data encoding, handshake blocks and combinatorial logic blocks. This section is divided into a section on handshake protocols, followed by a description of basic building blocks and how timing is matched through the circuit.

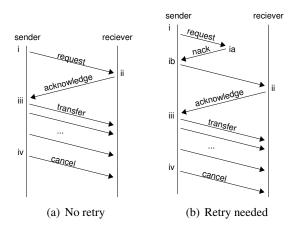

### 2.4.1 Handshake Protocols

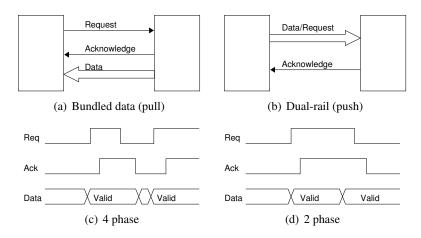

A handshake protocol is a series of events that occur in a specific order. A general handshake occurs as follows: A request is initiated, as data is valid; an acknowledge is raised by the target, as the data is accepted; the data no longer has to be valid. In return-to-zero protocols the request is lowered followed by a lowered acknowledge. This examples is a push channel handshake as data is pushed forward along the request, as opposed to a pull channel where data is requested by the reciever and delivered as part the acknowledge.

The request and acknowledge can be signaled on seperate wires to the data which is called bundled data (figure 2.10(a)), where the dual-rail embeds the request in the data wires (figure 2.10(b)). Dual-rail uses 2 wires per bit for a total of  $2 \times bit\_width + 1$ , where in the bundled data the overhead only consists of 2 wires (request and acknowledge). As mentioned, protocols also differ in whether they return to the same state after a handshake (4 phase, figure 2.10(c)) or keep the state, thus using the shift on the wire as part of the signalling (2 phase, figure 2.10(d)).

These 3 different aspects of a handshake protocol can be combined to create the handshake protocol of choice, MANGO employs 2 phase push dual-rail and 4 phase push bundled data.

#### 2.4.2 Data Flow

Two types of building blocks create the fundament for asynchronous circuit design: handshake blocks and functional blocks. Handshake blocks handles the flow control such as, splitting, selecting or joining data channels or control. The function block manipulate the data, without taking part in the handshakes.

Figure 2.10: Asynchronous circuits can be implemented with different style of handshake protocols.

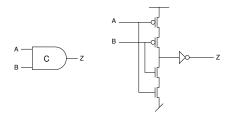

#### C-element

The basic element in asynchronous design is the Muller C-element, which is shown in figure 2.11. The C-element only changes output value when all inputs are the same, it is therefore suitable for the indication style circuit that is employed in asynchronous design.

Figure 2.11: The basic element of asynchronous design is the Muller C-element, the output only changes when both inputs are the same.

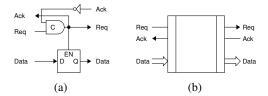

#### Latch

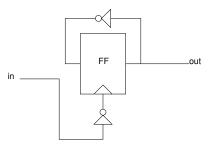

The basic handshake latch is controlled by a C-element and in figure 2.12 a 4 phase data latch is shown. The latch is operated by the EN signal that is generated by the output acknowledge and the input request.

Figure 2.12: A hanshake latch is controlled by C-element (figure 2.12(a)). The symbol used for handshake latches (figure 2.12(b)).

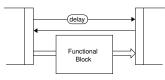

#### **Functional Blocks**

Several latches can be placed after each other to form a pipeline of latches. In between the latches, functional blocks can be placed. Because the functional blocks do not affect the handshake, the request and acknowledge is exchanged between the latches surrounding the functional block, as is depicted in figure 2.13. The figure

Figure 2.13: The functional block does not affect the actual handshake, but the arrival of the request in the next latch must be matched with the data.

also indicates a delay on the forward flowing request, which is needed to match the arrival of the request with the arrival of data. The delay of data in the functional block depends on the actual data and the request delay will therefore either be a function of the data or a fixed worst case delay.

## CHAPTER 3

## A Network-on-Chip Study

In recent years, the academic interest in NoC [12] has increased and different research groups have made publications on NoC concepts and implementations. Among academic implementations of NoC are the CHAIN network [1], SPIN [17] and  $\times$ PIPES [4].

Industrial implementation of the NoC concept, has also picked up over the last few years. Examples of these are the Element Interconnection Bus in the Cell processor [20], most known for its use in the upcoming Play Station 3. Philips are also researching in the NoC area with their Æthereal network [16], for use in the company's multi-media products such as televisions [33] and set-top boxes [14].

This chapter is a study of NoC implementations with focus on how Qualityof-Service features are implemented. The seven different NoCs in this study are chosen because they represent different approaches to and different levels of QoS. The first NoC described only provides BE routing and gives no guarantees on latency and throughput. The study then looks at NoCs that provides increasing levels of guarantees on latency and throughput.

Each of the NoCs is described in relation to what basic concepts the implement, such as the interface they implement and the unique features that makes them stand out. Their routing scheme are described, along with the components that they are constructed with and what topologies they support. The different communication structures are investigated with focus on what kind of service the NoCs offer. Especially how setup and configuration of service, such as guaranteed latency and throughput are handled.

Most of the studied NoCs are developed in academic environments, but Æthereal and Octagon are developed by Philips and STMicroelectronics respectively.

## 3.1 Hermes

The HERMES NoC [25] is developed at Faculdade de Informática PUCRS, Brazil. HERMES is designed to implement very small switches and be of immediate practical use. The routing scheme employed is XY routing between the switches arranged in a 2d-mesh structure.

A HERMES switch consists of control logic, five bidirectional ports and buffers. Four ports connect to neighbouring switches and the fifth port connects to the local IP core. The buffers are placed at the input ports. HERMES implements wormhole routing, for low memory and latency. The flit size is 8 bit and the two first flits in a packet contains the header, which consists of the target address and the number of flits in the packet.

The routing is a typical XY routing scheme where the packet is routed fully in the X direction and when aligned properly on the X axis, it is routed in the Y direction until it reaches its target, thus employing a minimal routing algorithm. When a packet has been granted access to an output port through its header flit the connection between input and output port is reserved for that packet. The number of flits is counted and compared to the flit number in the header until the entire packet has propagated through the switch, at which point the connection is closed. The connected ports inside the switch are stored in a switching table. Five simultaneously connections can be operated at any one time. The arbitration scheme prioritises the ports, based on which port last had a successful connection established to ensure that no port gets starved.

HERMES employs input queues as mentioned earlier. The purpose of these buffers is to reduce the number of switches affected by a blocked packet. The size of the buffer is parametrisable, with a default size of eight flits.

HERMES is loss less and inorder, but does not provide any form of latency or bandwidth guarantees. Because HERMES is connection-less no such guarantees can be given.

## 3.2 QNoC

At the Electrical Engineering Department, Israel Institute of Technology, Quality-of-Service NoC (QNoC) [10] has been developed and described. QNoC is a network of multi-port switches connected to each other by links. A link is composed of parallel point-to-point lines. The topology of QNoC is a mesh and it employs wormhole packet forwarding with hop-by-hop credit-based back-pressure flow-control. Routing paths are static, shortest path and X-Y coordinate based. Traffic is divided into four different classes of service: signaling, real-time, read/write and block-transfer, with signaling having the highest priority and block-transfers the lowest priority. A distinct feature of QNoC is that, unlike other wormhole based routing systems, packet forwarding is interleaved according to the QoS rules. This means that a high priority packet, such as a real-time packet, will preempt a low priority packet such as a read/write packet. QNoC does not provide hard guarantees on the service, but instead QNoC provides a statistical guarantee.

QNoC is loss less and it assumes that retransmission is never required. Packets always travel the shortest route, which minimises power dissipation and maximises the utilisation of the network. QNoC is unable to give hard guarantees because it has been chosen not to implement circuit switching due to the high cost of managing and establishing circuits. QNoC applies an irregular mesh topology to accommodate the irregular structure of SoC floor plans.

An IP core or as they are called in QNoC, a system module is connected to a router via a standard interface that is adapted to the communication needs of that module. The inter-router links are similarly adjusted to meet the expected bandwidth needs of that link. The expected communication needs and bandwidth requirements are developed from an extensive simulator that has been built alongside QNoC. Routing is done over fixed shortest paths, using X-Y directions in a coordinate fashion, thus packets are routed first all along X and then perpendicular or first along Y and then along the perpendicular X axis.

In QNoC, four different types of traffic are considered. They are as mentioned earlier, signaling, real-time, read/write and block-transfer. *Signaling* has the highest priority and is used for urgent and very short messages, such as interrupts and control signals. The introduction of a signaling service removes the need for dedicated single-use wires. The *Real-Time* service is used for streaming real-time applications, such as streamed audio and video. As described earlier, QNoC does not use circuit switching, thus the real-time service level is packet based like the remaining service levels. A real-time link may be allocated a maximum bandwidth that should not be exceeded. *Read/Write* is designed to provide bus-like semantics and supports short memory and register access. *Block-Transfer* service level is used for transfers of long messages and large blocks of data. These four service levels are prioritised, with signaling given the highest priority and block-transfers lowest. More service levels could easily be defined and included in this priority scheme. It would however, as described later, require more buffers.

A packet in QNoC consists of three parts: target routing address, command and payload. The routing address is required for routing, the command field identifies payload format. The payload can be of arbitrary length and contains, along with the payload, operation specific control information such as sender identification. A packet is transmitted as multiple flits, and the flit transfer over the link is controlled by handshaking. Three types of flits exist: full packet; end of packet; body. The full packet is a packet that is only one flit long. The body flit is a flit that is not the last flit of a packet. Flit type and service level is indicated on separate out-of-band wires.

A router in QNoC is connected to up to five links: four neighbouring routers and one IP core. The router forwards packets between input and output ports, flit by flit. Upon entering the router the flit gets stored in an input buffer. When the first flit of a packet arrives at the router, the output port for that packet is determined. Every flit arriving on that port and service level is then forwarded to the same output port. Because QNoC uses direct buffer mapping, every service level has its own buffer at each input. The buffer is small and only capable of storing a few flits, but the buffer size can be altered at design time. The buffers at each service level and input port are managed by credits. When a flit passes from input to output, a credit is passed back to the previous router on a separate wire. The actual transfer of data can be done by different types of handshake interface, an asynchronous interface could be used. Inside the router, each output port keeps tracks of available buffer space in the connected router in a table for each service level. The output link is allocated according to the available slots in the next routers buffers, the service level and a round-robin scheme between the input ports.

## 3.3 Octagon

Octagon is an on-chip communication architecture designed to meet the performance requirements of network processor SoCs, such as Internet router implementations. The communication architecture is described in [21]. The authors present the following desirable properties of Octagon: two-hop communication between any pair of nodes (depending on the number of nodes and configuration); higher aggregate throughput than a shared bus or crossbar under certain implementation conditions; simple, shortest-path routing algorithm; and less wiring than a crossbar interconnect. Octagon can operate in two modes; packet- and circuit-switched. A node in Octagon is associated with a processing unit and a memory module, this means that only non-local memory request generates Octagon communication requests. According to the authors of Octagon this is a very desirable feature when working with network functions such as routing table look-up and Internet Protocol classification.

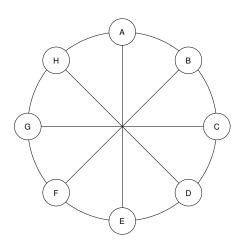

An example of a basic Octagon configuration that consists of eight nodes and twelve bidirectional links is shown in figure 3.1. As can be seen from the figure, every node can reach any other node with a maximum of two hops. When scaling Octagon up this maximum length changes, but this will be discussed later. The complexity of Octagons implementation increases linearly with the number of nodes that must be connected through the network.

In circuit switched mode, a network arbiter allocates the path between the two nodes that are to communicate. The path is reserved for a number of clock cycles for that communication. The arbiter permits several pairs of nodes to communicate with to each other at the same time, as long as the paths do not overlap, i.e. the arbiter permits spatial reuse of resources in circuit switched mode. To optimize the throughput when working in circuit switched mode, the authors of Octagon have developed the best-fit algorithm to schedule connections in the Octagon network. When working in packet switched mode the, nodes, routes the packets according to a destination field in each packet. The node calculates a relative address based on the destination address and the node's own address, and the packet is then either routed left, right, across or in to the node.

One of Octagon's strong features is its ability to scale. In [21] two scaling strategies are presented, low wiring complexity or high performance. As the naming of

Figure 3.1: A basic Octagon configuration, with 8 nodes and 12 bidirectional links.

the strategies suggests Octagon can be optimised for both low area and high performance. When scaling for low wiring the strategy is to connect several basic Octagon configurations as the one shown in figure 3.1. Nodes that are members of two basic Octagon loops function as bridges, and performs hierarchical routing. This allows the standard nodes to be used without modifications, because only the bridge nodes need to know about the other circles. An Octagon network with 22 nodes scaled for low wiring complexity has a maximum distance of 6 hops while maintaining very few wires when compared to a fully connected crossbar. The other scaling strategy proposed has higher performance than the above mentioned low wiring scaling strategy at the cost of more complex wiring. The high performance scaling strategy allows 512 nodes to be connected with a maximum distance of 6 hops and 2,304 links compared to a crossbar that would require  $512 + \cdots + 1$  links. The reader is referred to the above mentioned article for more on the interesting scaling strategies.

## 3.4 NOSTRUM

At the Laboratory of Electronic & Computer Systems, Royal Institute of Technology, Stockholm, the Nostrum Network on Chip has been described in several articles, fx. the protocol stack is described in [23] and the guaranteed bandwidth approach is described in [24]. Nostrum takes the same approach as macro networks, i.e. computer networks, and emphasises the layered communication by using layered protocols. Nostrum implements among other things switch load distribution, guaranteed bandwidth and multicasting. Furthermore, a simulation environment is provided.

IP cores or resources as they are called in Nostrum, are organised in a twodimensional mesh, where each switch is connected to its switch neighbours and to its resource. Other topologies are possible in Nostrum, but the outset of Nostrum is a 2d-mesh. The routing scheme chosen is hot-potato or deflective routing [15],

NOSTRUM

which eliminates the need for buffers in the switch compared to traditional storeand-forward routing schemes. Furthermore [28] describes how load distribution is implemented in Nostrum. Each switch indicates its current load by sending a stress value to its neighbours. This means that each switch has a picture of the load in its surroundings. Incoming packets are sorted by the number of switch cycles the packet has been travelling (in its current implementation). The packet with highest priority chooses its output port first and then the remaining packets choose in descending priority. Because of the hot-potato scheme packets which find their desired output port to be taken by a higher priority packet must choose another output port. Because the routing decisions are made locally and on individual flits there is no guarantee that flits let alone packets will arrive in order. Only best-effort traffic is handled by the above described routing scheme. The guaranteed service traffic is described in the following.

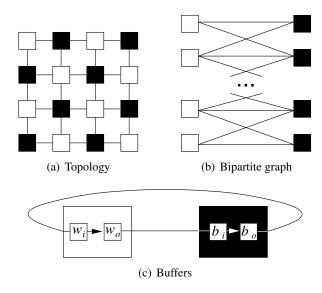

Figure 3.2: Temporally Disjoint Networks due to topology (3.2(a) and 3.2(b)) and buffers (3.2(c)).

As mentioned earlier, Nostrum provides Guaranteed Bandwidth as described in [24]. The guaranteed bandwidth is accomplished by introducing looped containers. A container, once created, is looping around on a predetermined path, a virtual circuit, and can either carry data or be marked as empty. As mentioned earlier Nostrum employs hot-potato routing, but to avoid packets being deflected into the local port when it was not meant for that resource, the insertion of new packets is only granted when there is a free output port. To guarantee bandwidth, insertion of the data must be ensured and because the container is already in the network the insertion of data is guaranteed. The header of a container contains two bits, the first bit marks the packet as a container the second bit marks it as empty or full, in addition to the normal header of a Nostrum packet. A container is a special type of packet hence the extra

marking. When a container arrives at an input port at the source of the virtual circuit it will, because of the deflective routing scheme and lack of buffers in the switch, be forced to leave on the next clock cycle. The virtual circuit will however not be deflected away on another path, but will always follow the path of the virtual circuit. The separation of the virtual circuits in each switch is done by Temporally Disjoint Networks and will be explained later in this section. The source of the virtual circuit will thus have one clock cycle to place data in the container, while the container resides at the input port of the switch. Once the container has left the input port of the switch it will follow the path with precedence over the normal BE traffic to the destination. Upon arriving at the destination the container will be unloaded and possibly be filled with new data. It is obvious to introduce multicasting by simply having the container loop around on a virtual circuit consisting of all the recipients of such a multicast. This is described in [22], and only involves changes to the switch. The granularity of the bandwidth allocation is determined by the maximum bandwidth available divided by the round-trip delay on a virtual circuit and the amount of bandwidth acquired by a virtual circuit depends on the amount of containers inserted on the virtual circuit. There is an upper bound on the amount of containers that can be inserted on the virtual circuit, which comes from the amount of buffer space along the virtual circuit. Virtual circuits are semi-static, in the meaning that the virtual circuits and their paths can only be created at design time. The amount of containers can however be adjusted at run time, by inserting and extracting containers.

As mentioned earlier, Nostrum uses the concept of Temporally Disjoint Networks (TDN), to explain the time-division multiplexing in the network. TDNs arise from the topology and the amount of buffers in the network. By colouring the nodes in the network in a chess-board like fashion, figure 3.2(a), it can be realised that two flits residing in different coloured nodes can never contest for the same resource, under the assumption that a flit does not get stored in a node, as it is the case with hot-potato routing employed by Nostrum. These two flits can then be tought of as being in different networks. Further a 2d-mesh network can be displayed as a bipartite graph, figure 3.2(b), where the two networks are placed opposite to each other. From this, it can be realised that a flit will always change network on each move, which leads to figure 3.2(c) where the biparte graph is collapsed into one node for each network. This is referred to as the topology factor. Introducing input and output buffers in each node,  $w_i, w_o, b_i, b_o$ , gives more distinct networks. This can be realised, by looking again at figure 3.2(c), it can be seen that a flit has to travel through at least four buffers, and the four flits in each of the four buffers will never contest for resources. These distinct networks is what Nostrum calls TDN. A virtual circuit can then be assigned to one or more specific TDNs and several virtual circuits will then be able to use the same switch. This however puts an upper bound of the number of virtual circuits that can pass through a single switch. The upper bound scales with the amount of buffer stages in each nodes as  $TDN = Topology \ factor \times Buffer \ stages$ .

# 3.5 Æthereal

The Æthereal NoC is developed at Philips Research Laboratories, Eindhoven, The Netherlands and is one of the few industry implementations. Æthereal has been described in several articles such as [16], [31] and [13]. In addition, mapping approaches and tools have further been described in [26] and [27] amongst other. Æthereal is a synchronous NoC, which offers among other things both GS and BE traffic, interfaces for standard sockets, monitoring and reconfiguration. In [3] and [33] an Æthereal implementation of a digital video reciever and a high-end consumer TV-system is compared to traditional interconnect solutions.

The Æthereal NoC offers a range of standard sockets (including OCP [30] and AXI - The Advandced eXtensible Interface) through network interfaces. The term network interface is used of the NA in Æthereal. The network interfaces handles the conversion from messages to packets, thus being a NA as described in section 2.1. The network interface is composed of a kernel and a shell, which will be described later in this section. Connected to the network interface is a router, which are used to provide contention-free source routing based on time-division multiplexing (TDM).

Æthereal uses a logical notion of synchronicity to create time slots for flits. A circuit is created by reserving consecutive slots in consecutive routers. Source routing is used because it allows for topology independence, and the path is made from a list of output ports on the route. As mentioned, two types of traffic service exist, namely BE and GS. GS traffic gives guarantees on both throughput and latency. Due to the nature of TDM the latency and throughput guarantees depend on each other. BE traffic is moved through the network using spare slots not used by GS connections and contesting BE packets are arbitrated using a round robin scheme. Interleaving of BE packets are not possible. GS traffic can however interrupt in the middle of BE traffic. Interleaving of GS connections are avoided by scheduling. A credit based flow control scheme is used between the BE buffers to avoid loss of flits by overflowing the buffers. The neighbouring routers keep track off each others buffer status by exchanging credits as flits are forwarded.

GS traffic is scheduled by the network interfaces, and the flits are then forwarded from their allocated slot to the next in the routers. Depending on the operating scheme the slot reservations are either done in network interfaces and routers or solely in the network interfaces. Æthereal operates with two ways of reserving slots: Distributed and central. The distributed approach uses slot tables in the routers and network interfaces, where the central approach only sets up the network interfaces. A path is then applied like in the BE case. A slot table matches input and output ports for each time slot. In both cases the network interface handles the insertion of data by use of a similar slot table. Æthereal thus requires an extensive scheduling of the traffic patterns in order to avoid congestion on links.

The authors of Æthereal argue that the distributed scheme is scalable, due to the route being distributed in the routers where in the central scheme the length of the routing path affects the flit size. The central scheme however has significantly smaller routers due to not using slot tables. The central scheme therefore works very well in smaller NoCs, which in the near future seems to be most likely.

The Æthereal network interfaces are split into two major parts; a network kernel that recieves and provides message to the network; and a network shell which converts standard sockets into the message type handled by the kernel. The actual message structure is irrelevant to the kernel, as it just handles the message as payload in packets that must be transported across the NoC. The kernel and shell communicate through ports and each port allows for a peer-to-peer connection with a shell and thus an IP core connected to another kernel. A network kernel can have several shells attached, both master and slave shells thus connecting several IP cores to one network kernel. Multiple connections are possible over each port, by using a connection ID to signal different connections. Each port has a number of buffer pairs, one pair for each connection that can be handled simultaneously, the pair is split in a reciever and sender buffer part. The use of buffers allows IP cores and the NoC to operate at different clock frequencies, and end to end flow control ensures that packets are only transmitted if the recieving end has buffer space to accept the packet. To support protocol features such as narrowcast and multicast special modules can be inserted between the shell and the kernel to enable these features. These modules are optional and can be inserted at design time if required by the application.

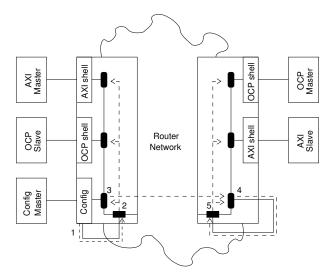

Figure 3.3: The configuration master first sets up its own configuration port (step 1), secondly it sends a configuration request to the remote network interface using the network (step 2), which sets up a return path to the configuration port. In step 3 the remote network interface is configured. Step 4 sets up the channels from the right to the left network interface, step 5 sets up the paths the other way.

One major asset of Æthereal is the support for configuration during run time. A special configuration shell is used to connect a configuration master to a network kernel. This configuration shell is connected to a standard port on the network kernel as well as to a special configuration port. The standard port is used to forward con-

figuration requests to other parts of the network and the configuration port is used to configure the other standard ports of the network kernel. The remote network kernel connects a port to its own configuration port, allowing the configuration master to access its ports. This means that the configuration is done using the network i.e. no seperate configuration channels or network is needed. Figure 3.3 shows two network kernels, one with a configuration shell; and one with a configuration loop. It also shows the use of different shells for different sockets.

A major part of the (re)configuration of Æthereal comes from the associated use case tools that were described in section 2.3. Because the use cases define the usage of the network ressources, mapping of connections in the network is used to allow use case switching. Scheduling is a very important aspect of Æthereal because it is used to avoid congestion on GS traffic. The scheduling allows for very small buffers in the GS part of the routers because a GS flit is never stalled in the network. This requires a very extensive scheduling to ensure.

# 3.6 SoCBUS

In [34] the Linköping SocBUS is proposed and described as a bus replacement network. It is developed at the Department of Electrical Engineering at Linköping University as part of Daniel Wiklunds PhD thesis. SoCBUS implements circuit switching only in a form they call packet connected circuit (PCC), which will be described later in this section. By only making circuit switching available, avoiding deadlock and guaranteeing in-order delivery becomes much simpler than in packet switched networks.

IP cores are arranged in a 2 dimensional mesh, because the authors of SoCBUS found the 2D mesh topology the most suitable for NoCs, due to an acceptable low wire cost and reasonable high bandwidth. In addition, cores with a high amount of communication between each other can be placed closer together to avoid large amounts of long distance traffic. The switches are 5 port switches with four of the ports connecting to neighbouring switches and one port connected to an IP core through a wrapper. These wrappers handle the differences between the IP cores interface and the interface used by SoCBUS, such as transaction style, port width, endianness and clock frequency. As mentioned, SoCBUS only employs circuit switching, but during setup of the circuits the switch has to route a request from the source of the circuit to the end destination. The routing scheme used for this is a minimum path length algorithm, where the routing decision is based on the destination address of the request. This is possible and feasible due to the fact that a NoC is static, as described in section 2.1.7.