# A MIXED VERIFICATION STRATEGY TAILORED FOR NETWORKS ON CHIP

G.Tsiligiannis, L.Pierre TIMA Laboratory, Grenoble, France

# INTRODUCTION

#### • Questions:

- Is it worth defining a specific verification methodology for NoCs?

- How should it look like?

- Answer as a proposal:

- Two-level approach:

- Verification of coarse-grained features at the *algorithmic level*

- Verification of fine-grained properties at the *implementation level* (VHDL RTL description)

- For this latter goal  $\rightarrow$  taxonomy of properties

# INTRODUCTION

• « Verification »

Correctness of communications, considering NoC features:

Network architectural characteristics (topology)

Routing algorithm

- Switching technique

- Access control

Ο...

Synchronous or asynchronous transmission protocol

o Buffered or bufferless transmission

# INTRODUCTION

• Nowadays, few verification-oriented results

- [Salaün et al, ASYNC'2007]: model checking approach, CHP specification translated into LOTOS description, some properties proven for FAUST (using CADP)

- [Yean-Ru et al, ICGCS'2010]: verification of properties for a part of a wormhole XY-routing NoC router, using State Graph Manipulator

- [Chenard et al, workshop at DATE'2007]: Assertion-Based Verification for a hierarchical ring network, debugging infrastructure

- Goossens et al, NoCs'2007]: also uses a monitor-based solution, and proposes a debug architecture

# PROPOSAL

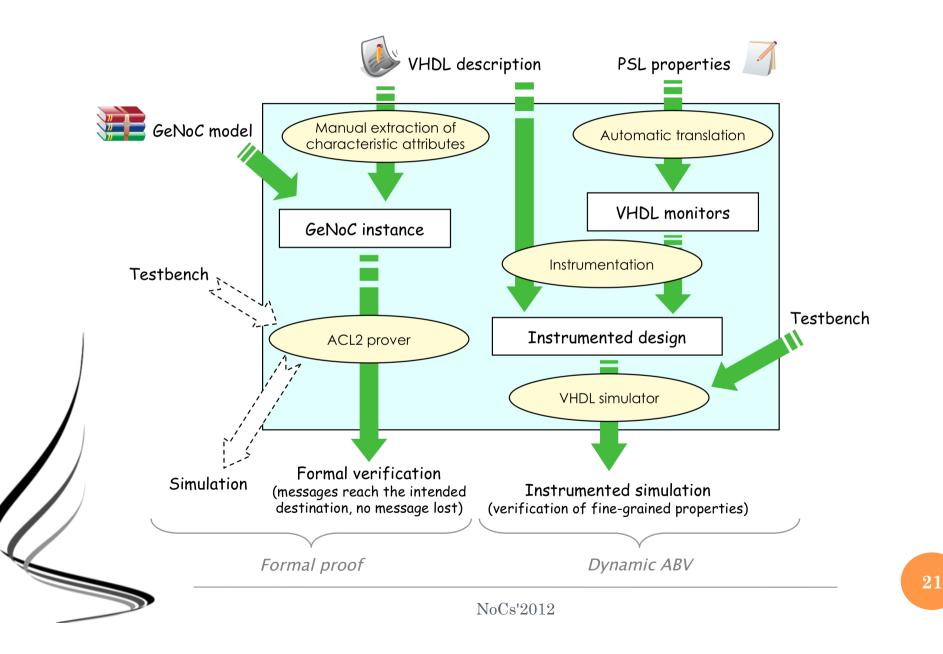

#### Mixed verification strategy

- Verification of high-level (algorithmic) properties

- Network description at a high level of abstraction, focuses on functional features and ignores implementation details

- Algorithmic specification + formal verification (description in a functional language and verification by theorem proving)

- Complemented by verification of low-level (implementation) properties

- Network description at a low level of abstraction: VHDL RTL source code

- Specification by logic and temporal properties + semi-formal verification (Assertion-Based Verification)

# APPLIED TO 2 STATE-OF-THE-ART NOCS

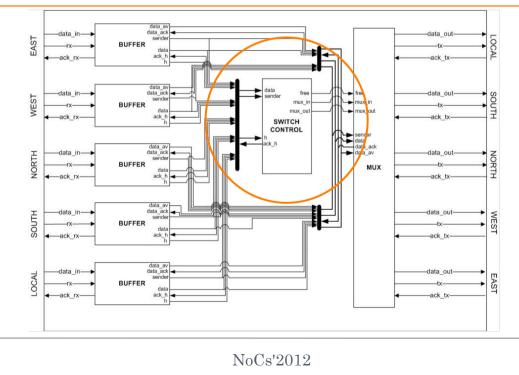

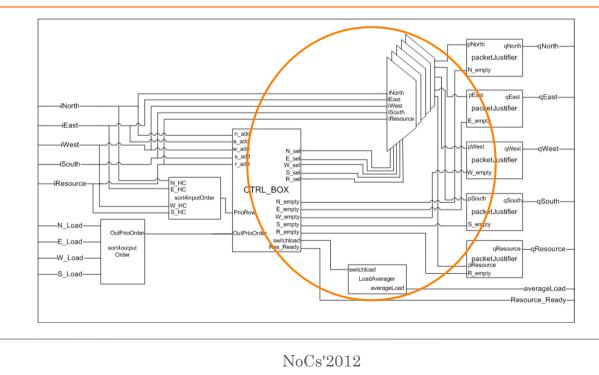

o Nostrum (http://www.ict.kth.se/nostrum/)

- 2D-mesh topology

- Hot potato routing

- Packet switching

- Synchronous

- o Hermes (PUCRS, Brazil)

- 2D-mesh topology

- Configurable routing (here minimal negative first routing)

- Wormhole switching

- Asynchronous (handshake protocol)

### AT THE ALGORITHMIC LEVEL

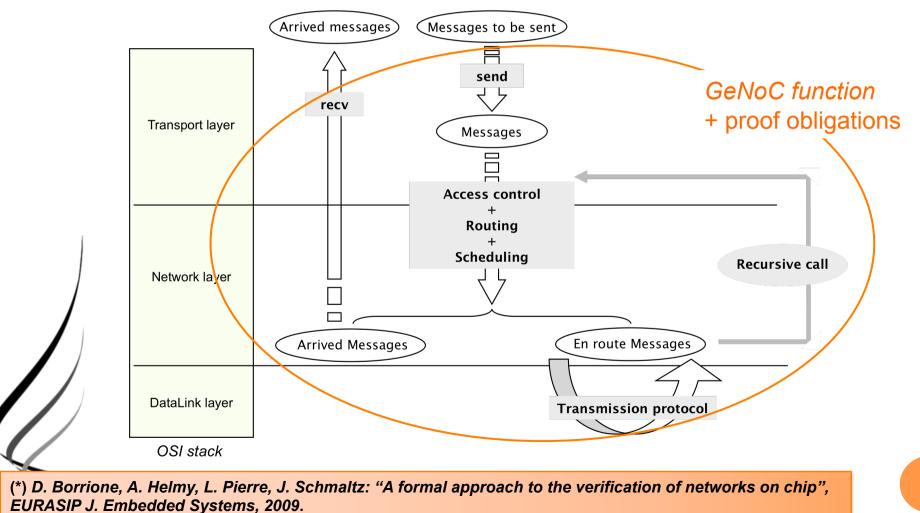

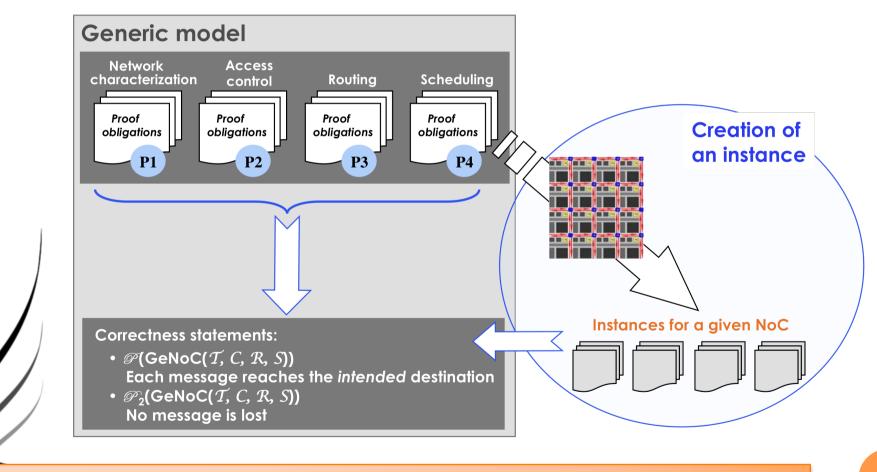

• Generic modeling and verification technique (\*)

### AT THE ALGORITHMIC LEVEL

• Generic modeling and verification technique (\*)

(\*) D. Borrione, A. Helmy, L. Pierre, J. Schmaltz: "A formal approach to the verification of networks on chip", EURASIP J. Embedded Systems, 2009.

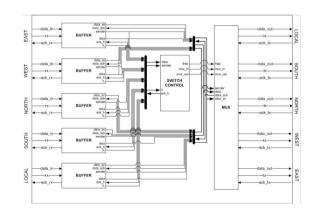

### AT THE IMPLEMENTATION LEVEL

• Assertion-Based Verification

• Assertion: statement about the intended behaviour or a requirement of the design

• Temporal logics: CTL, LTL,...

Specification languages: SVA (IEEE Std 1800), PSL (IEEE Std 1850)

• Assertion-Based Verification: does the design obey these temporal assertions?

• Static analysis (model checking)

Dynamic verification (during simulation)

### AT THE IMPLEMENTATION LEVEL

• Assertion-Based Verification

• Assertion: statement about the intended behaviour or a requirement of the design

• Temporal logics: CTL, LTL,...

• Specification languages: SVA (IEEE Std 1800), PSL (IEEE Std 1850)

• Assertion-Based Verification: does the design obey these temporal assertions?

• Static analysis (model checking)

• Dynamic verification (during simulation)

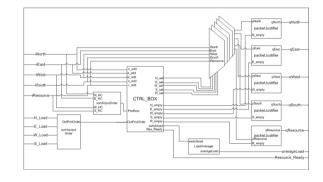

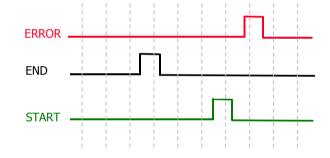

### ASSERTION-BASED VERIFICATION

- Verification of fine-grained properties on the signals of the design

- Examples:

- Temporal operators

default clock = (posedge clk);

always (END ->

next (START before ERROR))

Extended regular expressions

default clock = (posedge clk);

always ( { X and not Y; X and Y } |-> { not Ctrl [\*8] ; Ctrl } )

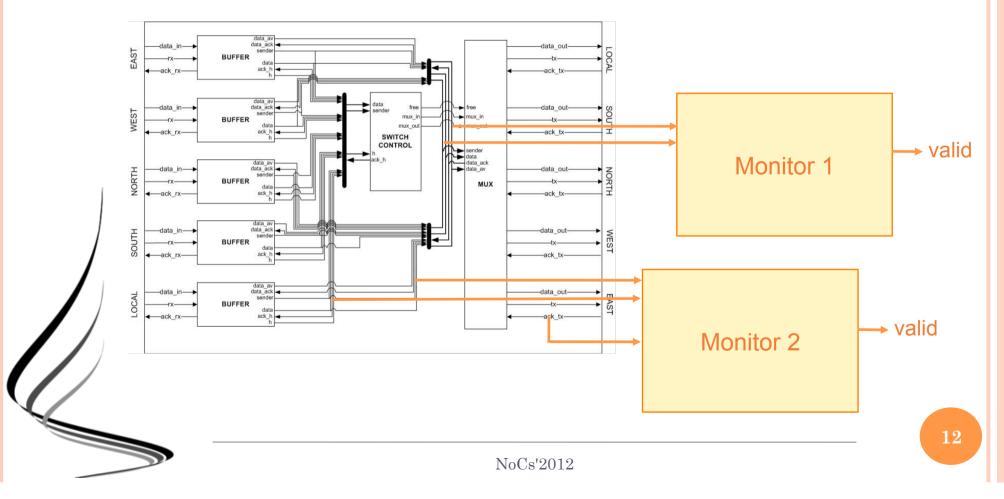

### ASSERTION-BASED VERIFICATION

• Hardware monitors from PSL assertions for router properties

#### o General-purpose assertions for routers

|   | Property                      | Routing                          | QoS                    | Synchronous/<br>asynchronous | Buffered/<br>bufferless  |

|---|-------------------------------|----------------------------------|------------------------|------------------------------|--------------------------|

| ] | No packet loss                |                                  |                        | Х                            | + switching<br>technique |

|   | No packet duplication         |                                  |                        | Х                            | Х                        |

|   | Correct delivery upon arrival | Deterministic/<br>fully adaptive |                        |                              |                          |

|   | Routing decision integrity    |                                  |                        |                              |                          |

| / | Satisfaction of QoS           |                                  | Guaranteed/best effort |                              |                          |

|   | Packet<br>progression         |                                  |                        |                              |                          |

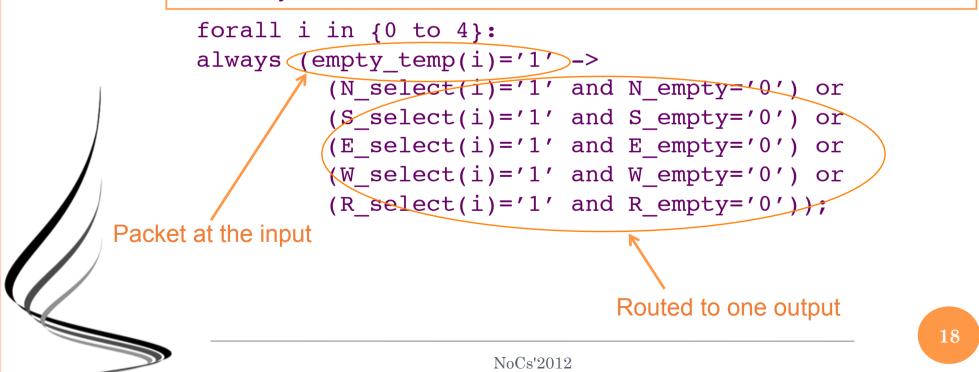

#### • Example: No packet loss

- Inside the router

- Case of buffered communications

- Wormhole: the allocated resources will remain allocated to the same packet flow until the last flit is transmitted

- ο...

#### Case of bufferless communications

- If a packet enters the router, it will be ready to leave the router at the same cycle

- A packet will not be dropped if the requesting destination is available

- Between two routers

- Case of synchronous communications

- Case of asynchronous communications

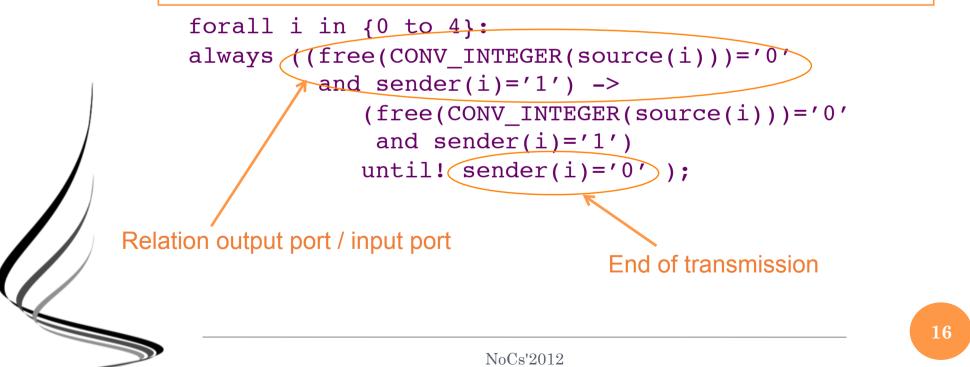

#### • Example: No packet loss

• Inside the router

#### Hermes (PUCRS, Brazil)

• The allocated resources will remain allocated to the same packet flow until the last flit is transmitted

#### • Example: No packet loss

• Inside the router

#### Hermes (PUCRS, Brazil)

• The allocated resources will remain allocated to the same packet flow until the last flit is transmitted

#### • Example: No packet loss

• Inside the router

o Nostrum (http://www.ict.kth.se/nostrum/)

• If a packet enters the router, it will be ready to leave the router at the same cycle

#### • Example: No packet loss

• Inside the router

o Nostrum (http://www.ict.kth.se/nostrum/)

• If a packet enters the router, it will be ready to leave the router at the same cycle

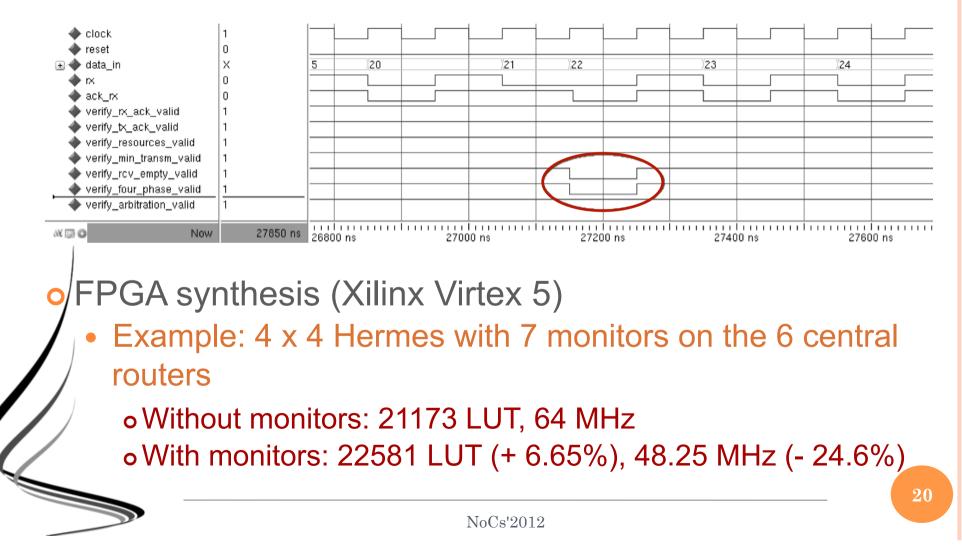

### EXPERIMENTAL RESULTS

• Instrumentation of NoCs with PSL properties

- Nostrum: 39 assertions

- Hermes: 30 assertions

- Properties automatically transformed into synthesizable verification components (\*)

- Can be used within the simulation or FPGA prototyping procedures: for debug during NoC design

- Or can be used as embedded verification components (ASIC/FPGA synthesis): for the online verification of safety requirements

(\*) TIMA « HORUS » technology (Y.Oddos, K.Morin-Allory, D.Borrione: "Assertion-Based Design with Horus", Proc. MEMOCODE'2008) integrated into Dolphin EDA tools: http://www.dolphin.fr/medal/sled/segment/sled\_sdg.php

# EXPERIMENTAL RESULTS

#### • Simulation (with fault injection)

# CONCLUSION - OVERALL APPROACH

# CONCLUSION

Multi-level verification solution

• Experimented on:

Nostrum: 199 ACL2 theorems (proof obligations and auxiliary theorems), 39 PSL properties

o Hermes: 272 ACL2 theorems, 30 PSL properties

#### • Future work:

Embedded verification components

$\rightarrow$  need specific synthesis optimisations, and specific facilities for collecting relevant diagnosis information

Runtime Assertion-Based Verification at the system level (NoC infrastructure in a SoC, SystemC TLM)